- FPGA开发板:Genesys2

- HDMI显示屏:1280×720

- 实现功能:按键切换图像显示

字符取模参考:8. vga显示器字符显示 --- [野火]FPGA Verilog开发实战指南------基于Altera EP4CE10 征途Pro开发板 文档

功能实现部分参考:

HDMI字符显示实验 --- ZYNQ 7000开发平台FPGA教程 1.0 文档

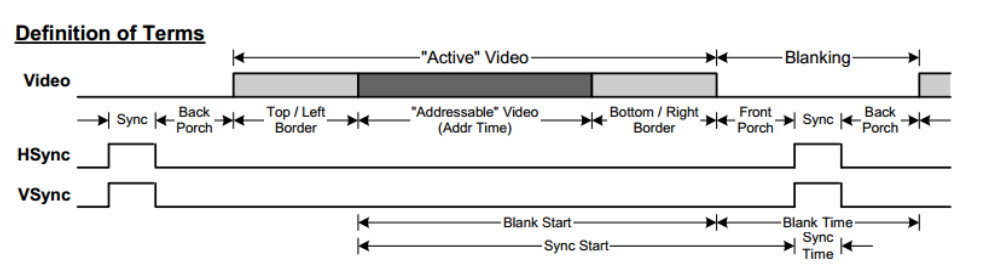

HDMI时序:

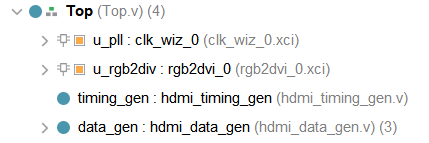

工程结构:

关键代码说明:

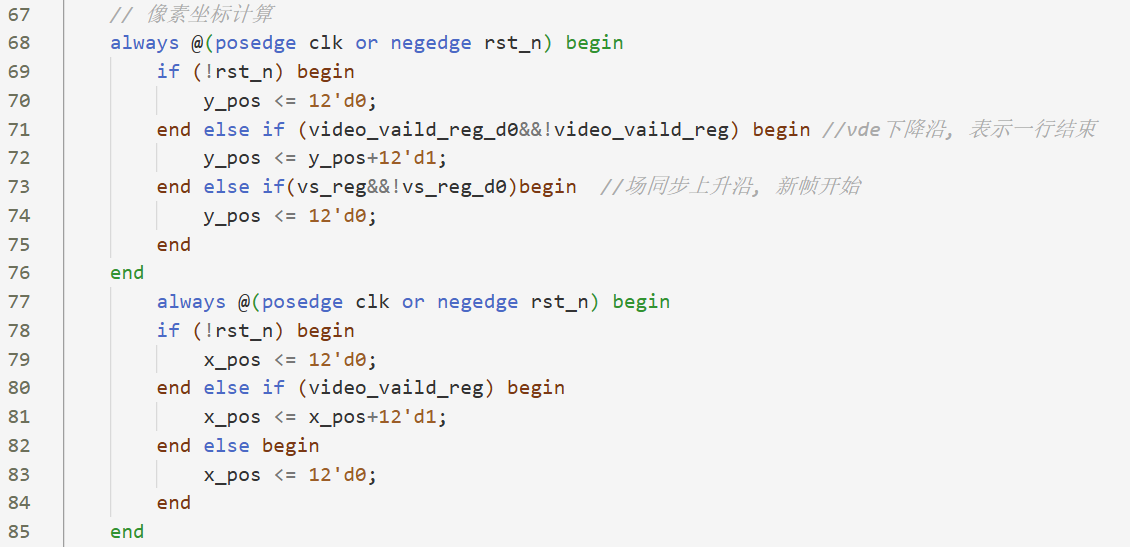

①像素坐标计算。检测到video_valid的下降沿时将y_pos加1,检测到场同步上升沿时将y_pos置0:

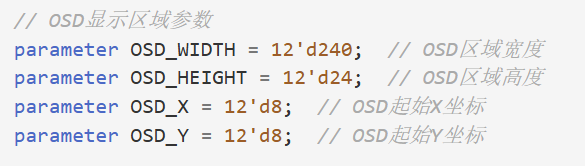

② 确定显示区域。这里显示区域大小为240x24,共5760个像素点,在ram中为720个字节。点阵大小需要和区域大小一致,假设单个字符点阵大小设置为40*24(英文字符为20*24),则总点阵大小为240x24可以显示12个英文字符:

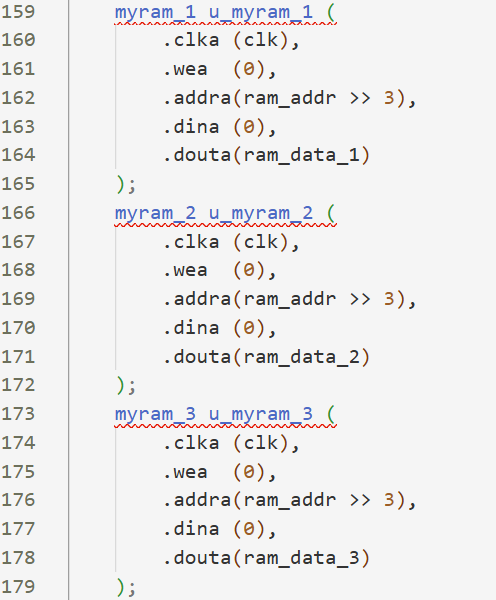

③ 使用三个ram存储三个不同的字符图像,并将ram_addr除8作为字节地址:

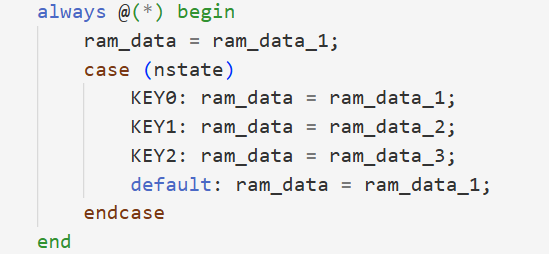

通过状态机实现按键控制字符显示功能:

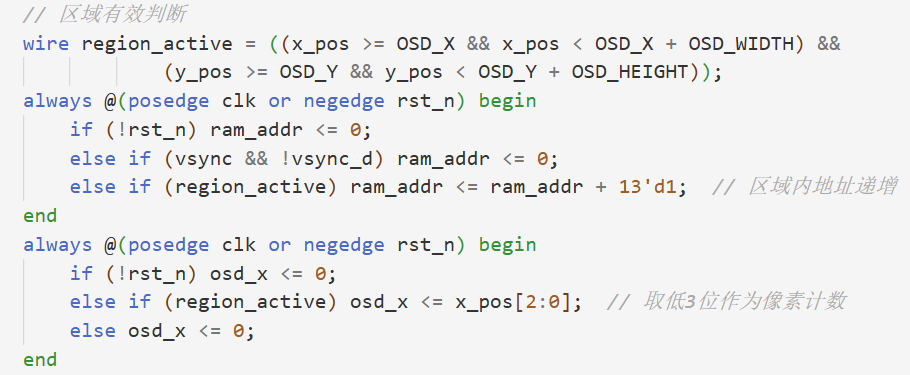

④ 有效区域内ram地址递增,并将x_pos的低三位(0~7)作为像素/比特地址:

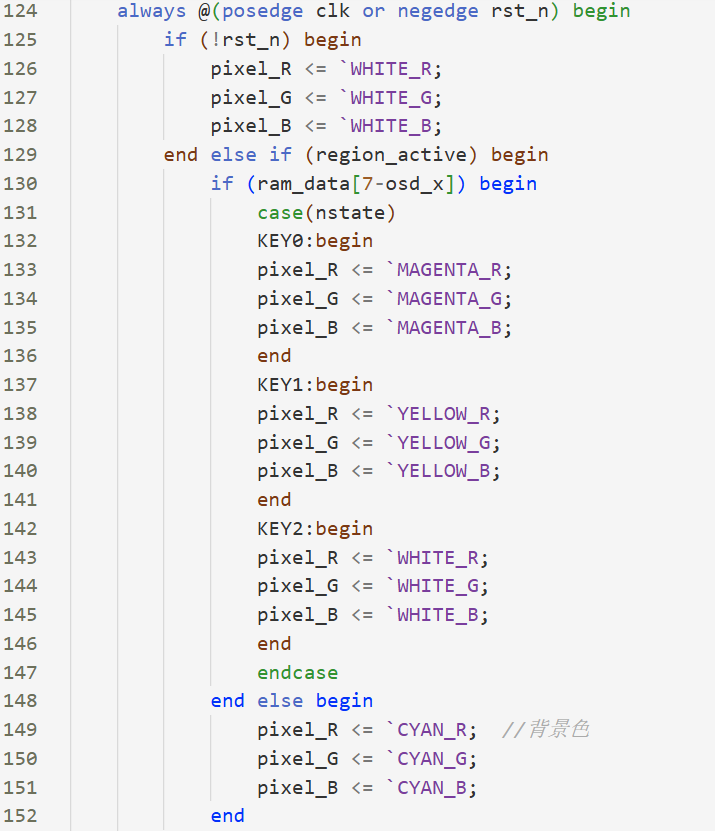

⑤ 从ram_data[7]到[0]判断像素数值:

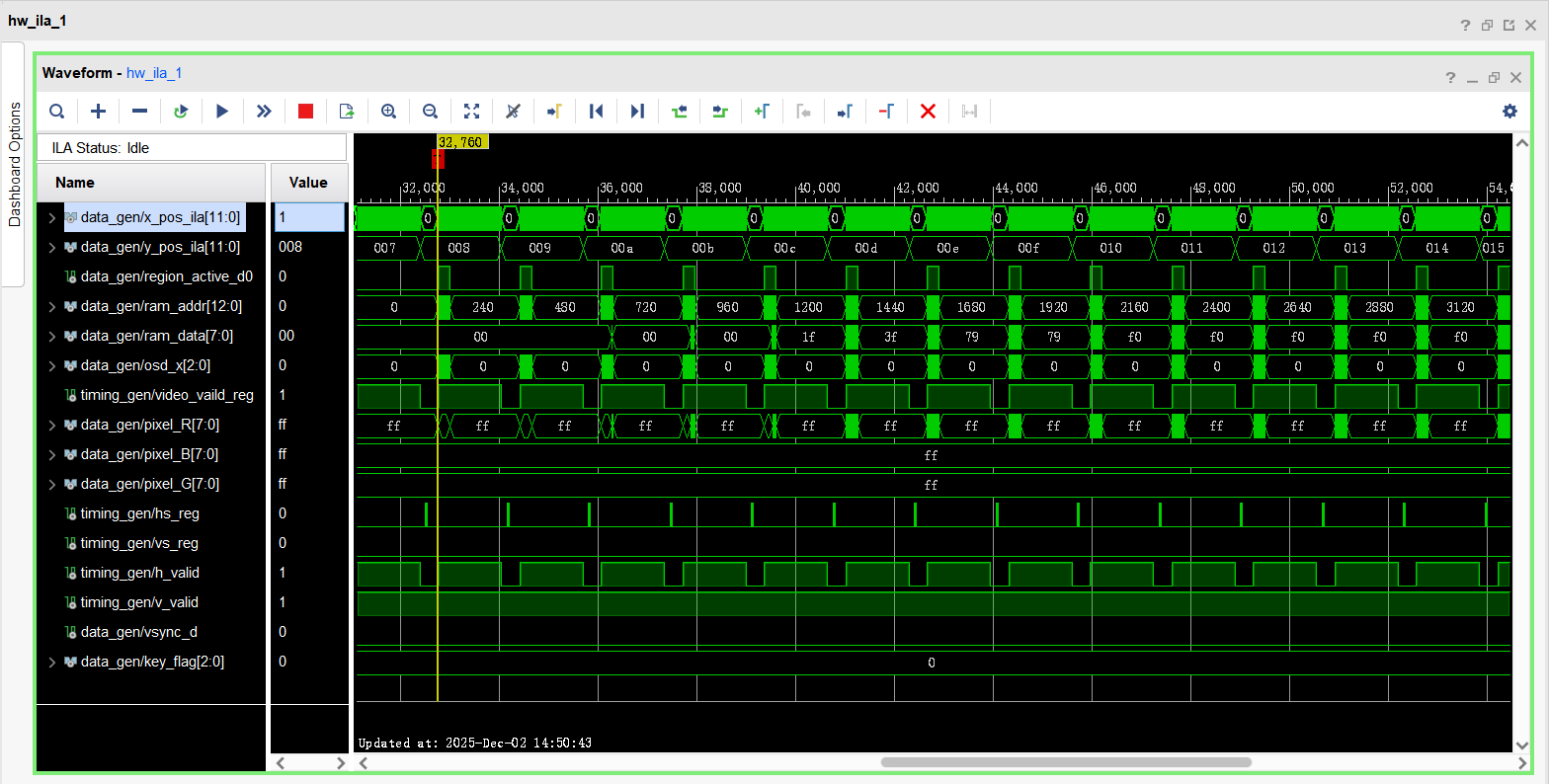

使用ILA观察波形,观察到ram_addr在有效区域内自增,一次持续时间内增加240,共增加24次,在5760处停止:

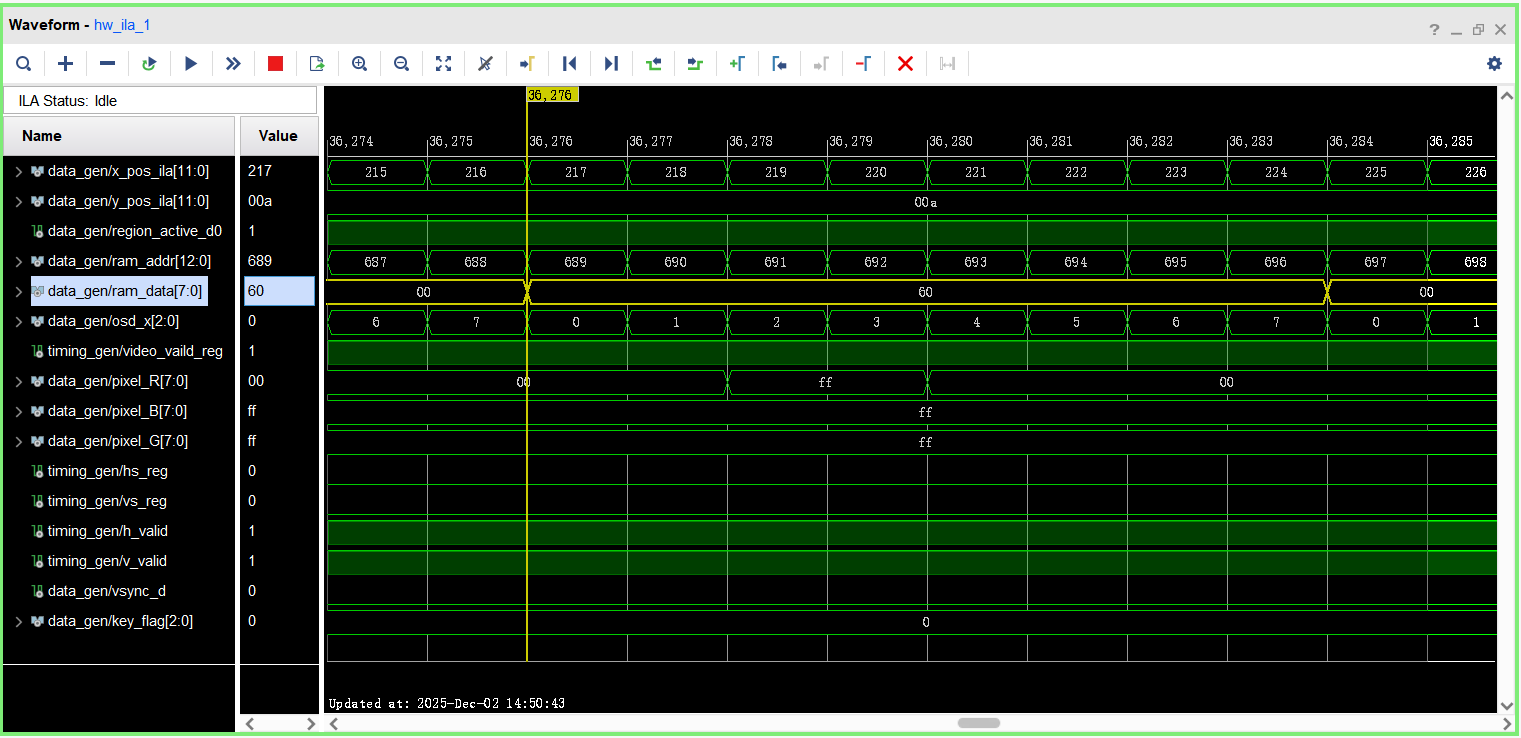

如图,ram_addr计数到688时(字节地址为86),读出数据为0x60,持续8个时钟周期,osd_x从0递增到7,分别在计数到1和2时检测到ram_data[6]和ram_data[5]为1,pixel_R/G/B在下一个周期更新输出:

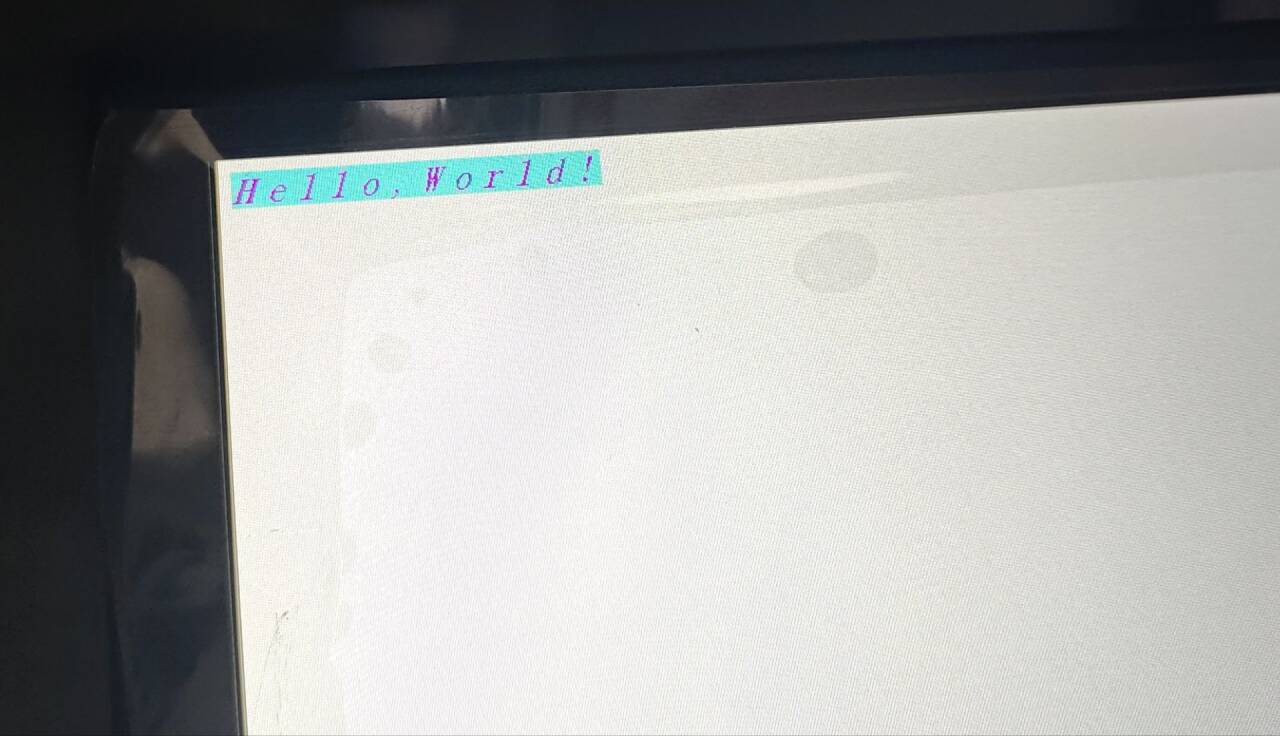

效果展示:

- 按下KEY0显示 Hello,World!:

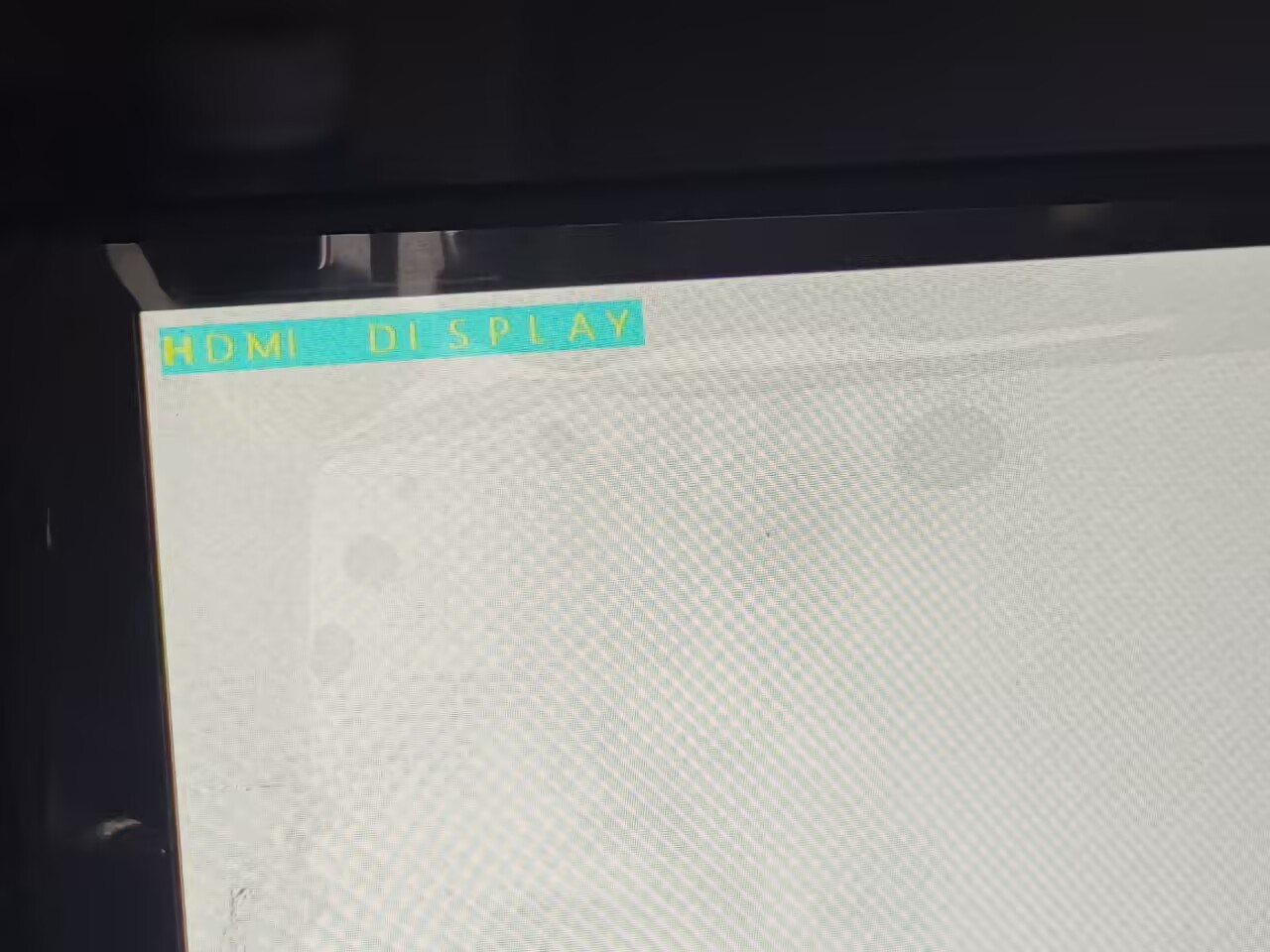

- 按下KEY1显示 HDMI DISPLAY:

- 按下KEY2显示 GENESYS2开发 :