目录

1.课题概述

基于FPGA的数字示波器,通过DDS-IP核生成标准正弦波形,再将波形数据转换为HDMI显示格式,最终在显示器上呈现波形形态。该系统既具备数字示波器的信号发生基础功能,也通过HDMI接口完成可视化输出,其整体架构包含DDS信号生成模块、波形缓存模块、HDMI视频驱动模块、时钟管理模块,正弦信号频率控制模块。

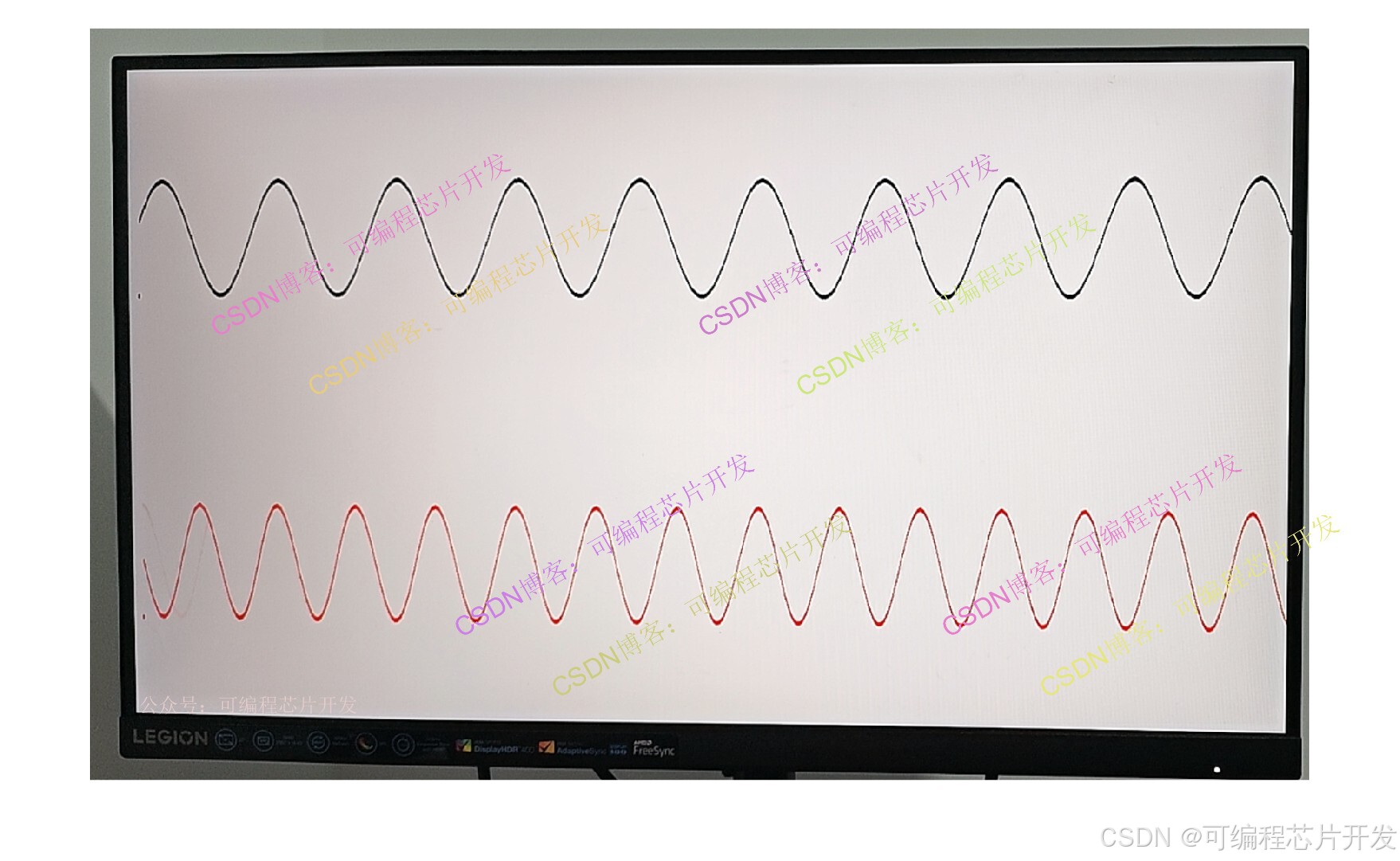

2.系统测试效果

在显示器上,显示不同频率的正弦波形:

fpga硬件测试不同开发板之间的移植,可以参考如下的文章:

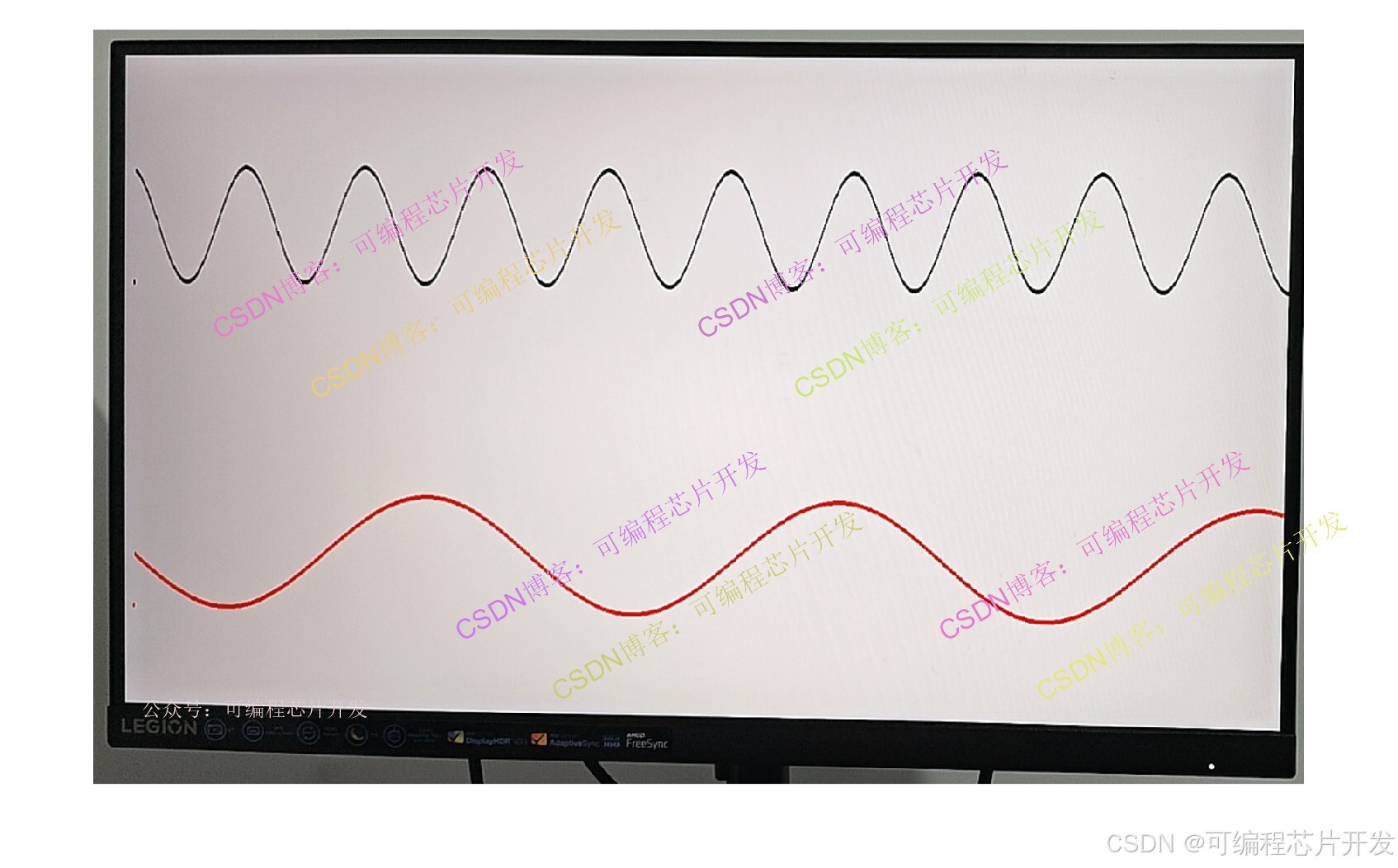

修改频率,显示器显示效果如下:

3.核心程序与模型

版本:vivado2022.2

.....................................................

// һ DDS

//the module of sin signal

wire[7:0]signal_sin1;

wire [15 : 0] m_axis_data_tdata;

dds_compiler_0 dds_compiler_0u (

.aclk (divclk), // input wire aclk

.aresetn (rst_n), // input wire aresetn

.s_axis_config_tvalid(1'b1), // input wire s_axis_config_tvalid

.s_axis_config_tdata(32'd2000000), // input wire [31 : 0] s_axis_config_tdata

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata), // output wire [15 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata() // output wire [31 : 0] m_axis_phase_tdata

);

assign signal_sin1={m_axis_data_tdata[15],m_axis_data_tdata[15:9]};

wire[7:0]signal_sin2;

wire [15 : 0] m_axis_data_tdata2;

dds_compiler_0 dds_compiler_1u (

.aclk (divclk), // input wire aclk

.aresetn (rst_n), // input wire aresetn

.s_axis_config_tvalid(1'b1), // input wire s_axis_config_tvalid

.s_axis_config_tdata(K), // input wire [31 : 0] s_axis_config_tdata

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata2), // output wire [15 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata() // output wire [31 : 0] m_axis_phase_tdata

);

assign signal_sin2={m_axis_data_tdata2[15],m_axis_data_tdata2[15:9]};

wire signed[7:0]test1 = signal_sin1;

wire signed[7:0]test2 = signal_sin2;

wire video_clk;

wire video_clk_5x;

wire video_hs;

wire video_vs;

wire video_de;

wire[7:0] video_r;

wire[7:0] video_g;

wire[7:0] video_b;

color_bar hdmi_color_bar(

.clk0(divclk),

.clk(video_clk),

.rst(1'b0),

.i_start(1'b1),

.test1(test1),

.test2(test2),

.hs(video_hs),

.vs(video_vs),

.de(video_de),

.rgb_r(video_r),

.rgb_g(video_g),

.rgb_b(video_b)

);

endmodule

00X6_010m4.系统原理简介

FPGA作为整个系统的控制核心,承担着模块调度、数据处理、时序同步的功能:

1.时钟管理模块通过PLL IP核生成各模块所需时钟(DDS 工作时钟、HDMI 像素时钟、系统同步时钟),保证各模块时序一致。

2.DDS IP核在时钟驱动下生成正弦波数字序列,输出至波形缓存模块(FIFO/BRAM)进行临时存储,解决DDS输出速率与HDMI显示速率的匹配问题。

3.HDMI视频驱动模块生成标准视频时序,在有效像素区域内,根据当前 X 轴像素坐标读取缓存中的正弦波幅值数据,将其转换为Y轴像素坐标对应的灰度数据(如黑白波形显示)或RGB数据(如彩色波形显示)。

4.TMDS编码模块将RGB数据、同步信号封装为HDMI差分信号,通过FPGA的HDMI输出引脚传输至显示器,最终呈现稳定的正弦波形。

正弦波形与显示像素之间的映射

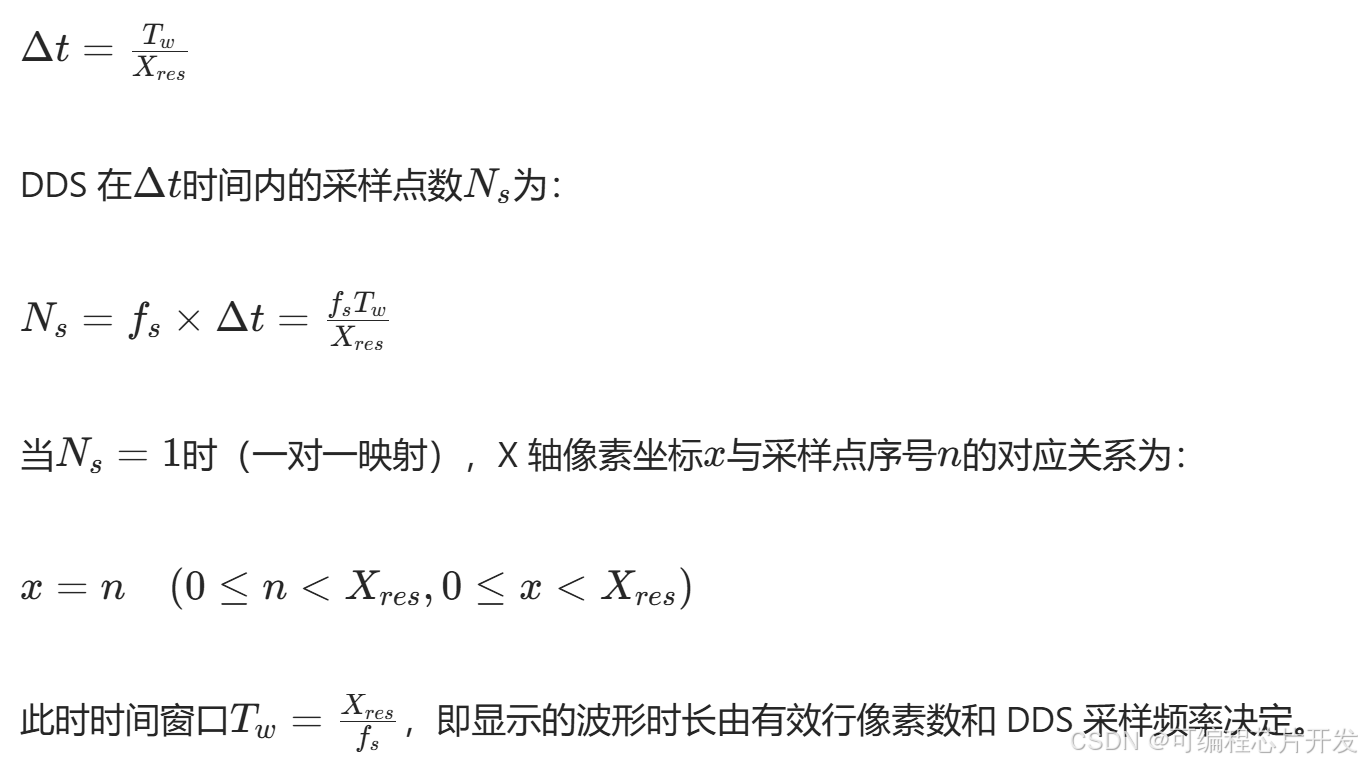

1.X轴(时间-行像素)映射公式

设DDS的采样频率为fs(等于DDS工作时钟频率fclk),显示器有效行像素数为Xres(如720P为1280,1080P为1920),波形显示的时间窗口为Tw,则每个行像素对应的时间间隔Δt为:

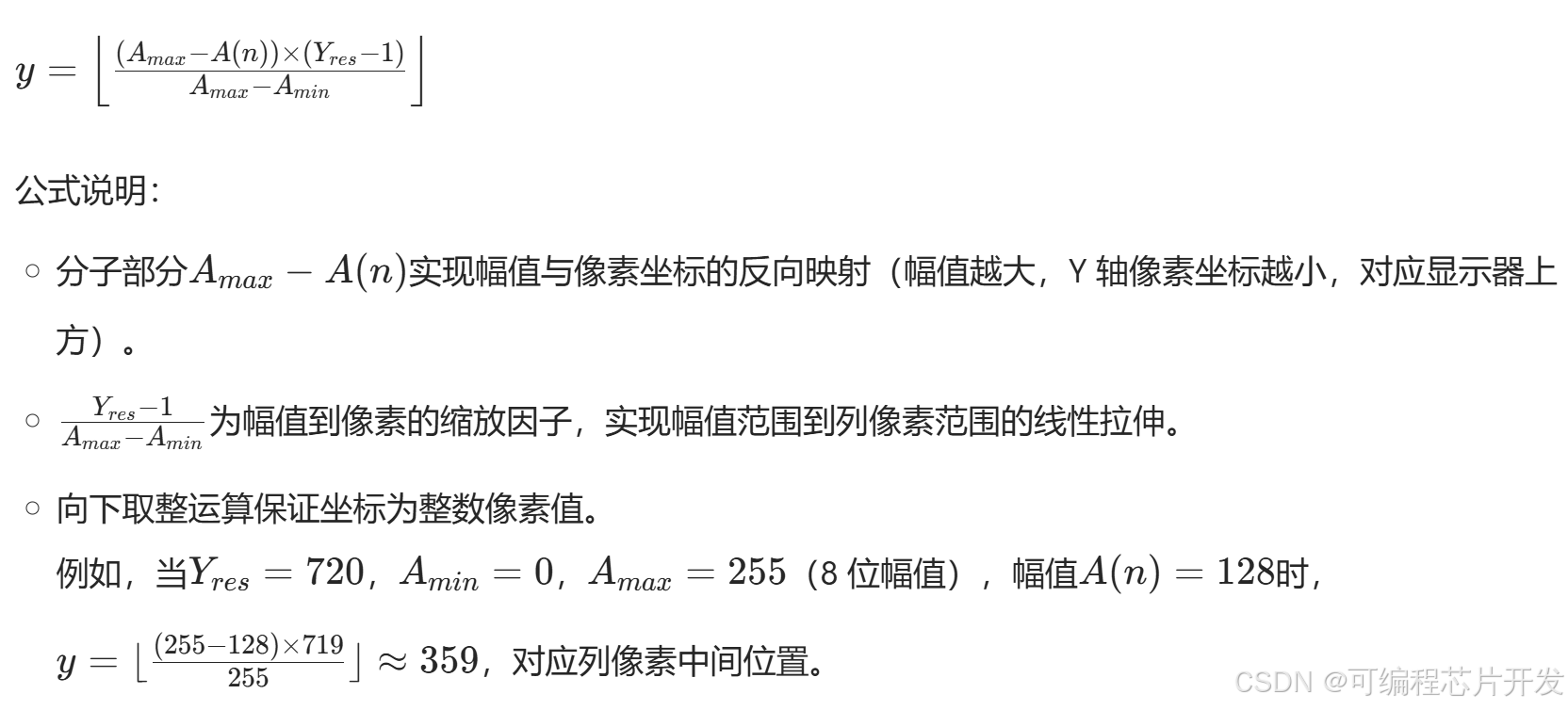

2.Y轴(幅值-列像素)映射公式

设显示器有效列像素数为Yres(如720P为720,1080P为1080),DDS输出的正弦波幅值范围为[Amin,A max],列像素坐标y(从上到下为0到Yres−1)与幅值A(n)的映射关系为:

5.完整工程文件

v v

关注后,GZH回复关键词: a18