Latch 是什么

Latch 其实就是锁存器,是一种在异步电路系统中,对输入信号电平敏感的单元,用来存储信息。锁存器在数据未锁存时,输出端的信号随输入信号变化,就像信号通过一个缓冲器,一旦锁存信号有效,则数据被锁存,输入信号不起作用。因此,锁存器也被称为透明锁存器,指的是不锁存时输出对于输入是透明的。

几种产生 Latch 的情况

-

组合逻辑中 if 语句没有 else;

-

组合逻辑 中 case 的条件不能够完全列举时且不写 default;

-

组合逻辑中输出变量赋值给自己。

其中包括

情况一:if-else中出现输出变量赋值给自己;

情况二:case中出现输出变量赋值给自己;

情况三:assign中出现输出变量赋值给自己(如下)

verilog

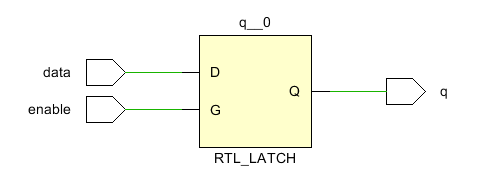

module latch

(

//=========================< Port Name >==============================

//input

input wire data ,

input wire enable ,

//output

output wire q

);

assign q = (enable == 1'b1)? data:q;

endmodule根据上面 RTL 代码综合出的 RTL 视图,我们可以看到也产生了latch。

其他情况参考:Verilog中锁存器(Latch)原理、危害及避免(野火《FPGA Verilog开发实战指南------基于Xilinx Artix7》第十三章)

时序逻辑不产生Latch

只有不带时钟的 always 语句 if 或者 case 语句不完整才会产生 latch,带时钟的语句if 或者 case 语句不完整描述也不会产生 latch。

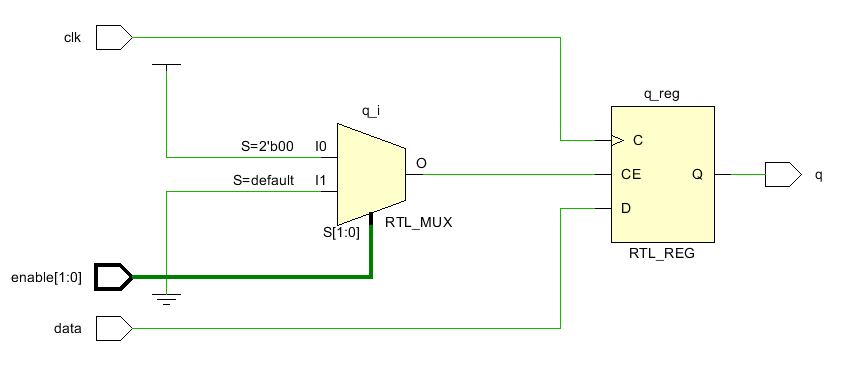

下面为缺少 else 分支的带时钟的 always 语句和不带时钟的 always 语句,通过实际产生的电路图可以看到第二个是有一个 latch 的,第一个仍然是普通的带有时钟的寄存器。

verilog

module nolatch

(

//=========================< Port Name >==============================

//input

input wire clk ,

input wire data ,

input wire [1:0] enable ,

//output

output reg q

);

always @(posedge clk) begin

if(enable == 2'd0)begin

q<=data;

end

else if(enable == 2'd1) begin

q<=q;

end

end

endmodule根据上面 RTL 代码综合出的 RTL 视图,我们可以看到即使 if 语句没有 else、输出变量赋值给自己也不产生latch。

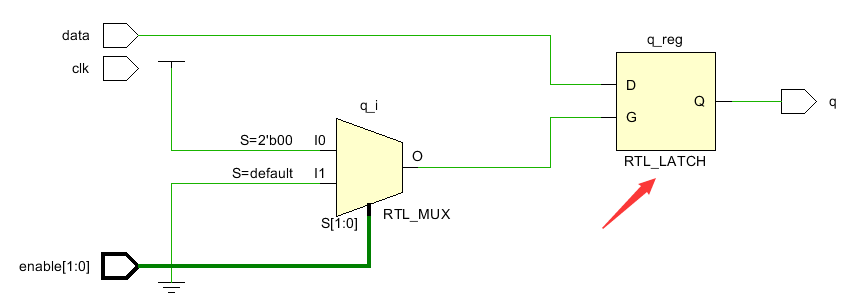

将上面代码中的always @(posedge clk) 换成 always @(*),(块中使用阻塞或非阻塞赋值)此时产生latch。

Latch的特点及危害

(1)对毛刺敏感

使能信号有效时,输出状态可能随输入多次变化,产生空翻,对下一级电路很危险,不能异步复位,因此在上电后处于不确定的状态。并且其隐蔽性很强,不易查出。因此,在设计中,应尽量避免latch的使用。

(2)不能异步复位

由于其能够储存上次状态的原因,上电后Latch处于不定态。

(3)复杂的静态时序电路分析

首先,锁存器没有时钟信号参与信号传递,无法做STA;其次,综合工具会将 latch 优化掉,造成前后仿真结果不一致。

(4)占用更多资源

注意,"FPGA 中只有LUT和FF的资源,没有现成的Latch,所以如果要用Latch,需要更多的资源来搭出来。"这个观点不完全是正确的。

在Xilinx的FPGA中,6系列之前的器件中都有Latch; 6系列和7系列的FPGA中,一个Slice中有50%的storage element可以被配置为Latch或者Flip-Flop, 另外一半只能被配置为Flip-Flop。比如7系列FPGA中,一个Slice中有8个Flip-Flop,如果被配置成了Latch,则该Slice的另外4个Flip-Flop就不能用了FPGA结构与片上资源 1.4。这样确实造成了资源的浪费。但在在UltraScale的FPGA中,所有的storage element都可以被配置成Flip-Flop 和Latch。

(5)额外的延时

在ASIC设计中,锁存器也会带来额外的延时和DFT,并不利于提高系统的工作频率。

(6)锁存器的优点

如果锁存器和触发器两者都由与非门搭建的话,锁存器耗用的逻辑资源要比D触发器少(D触发器需要12个MOS管,锁存器只需6个MOS管),锁存器的集成度更高,所以在ASIC设计中会用到锁存器,且只有在CPU高速电路或者RAM这种面积很敏感的电路才使用锁存器。

综上,在组合逻辑中一定要避免输出信号处于不定的状态,一定要让输出无论在任何条件下都有一个已知的状态,就可以避免 Latch 的产生。