目录

[1.1. 名字](#1.1. 名字)

[1.2. 为什么要 4 个脚?(内部结构揭秘)](#1.2. 为什么要 4 个脚?(内部结构揭秘))

[1.3. 原理图中的画法(红线的意思)](#1.3. 原理图中的画法(红线的意思))

[2.1. 按钮不仅是电子元件,它是"受力件"](#2.1. 按钮不仅是电子元件,它是“受力件”)

[2.2. 为什么"不连线"会导致强度变低?](#2.2. 为什么“不连线”会导致强度变低?)

[2.3. 总结](#2.3. 总结)

1.按键简介

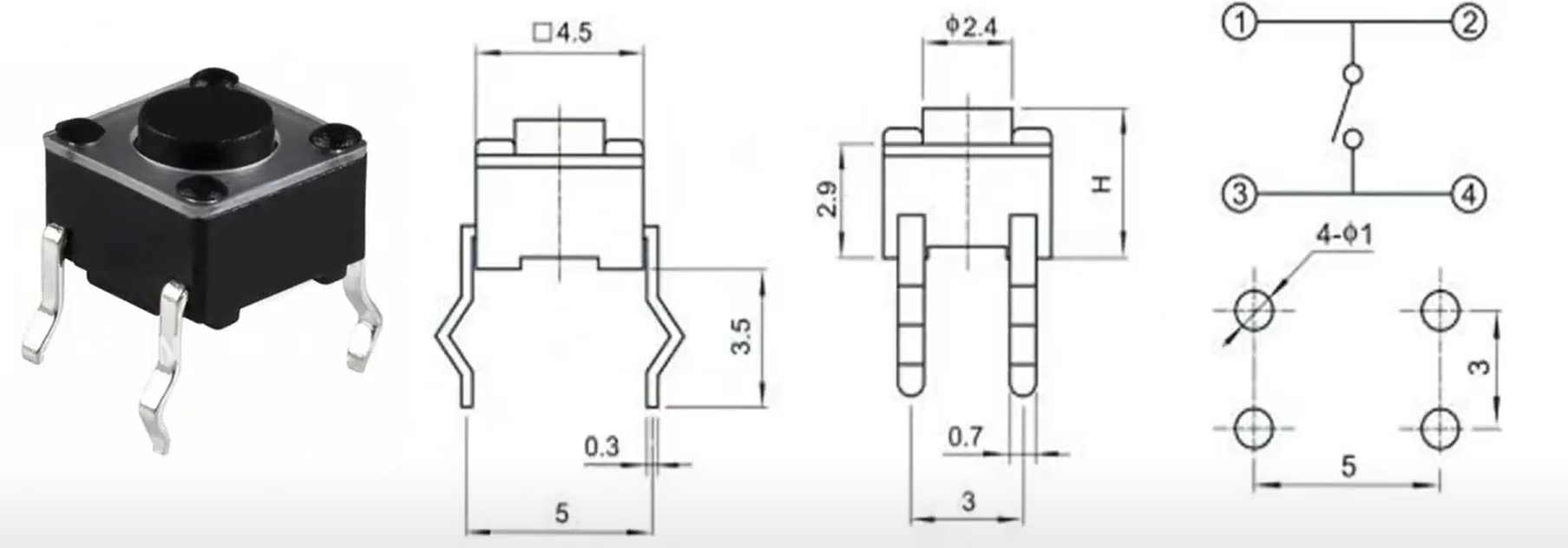

这是非常常见的 4 脚轻触开关 (Tactile Switch / Tact Switch),也是电子设计中最常用的按键元件。

1.1. 名字

-

学名: SPST-NO(单刀单掷-常开)轻触开关。

-

俗称: 轻触按键、微动开关(虽然严格说微动是另一种,但口语常混用)、Tact Switch。

-

尺寸: 最常见的是 6x6mm 或 12x12mm 规格。

1.2. 为什么要 4 个脚?(内部结构揭秘)

虽然原理图上它是一个简单的开关(按下导通,松开断开),只需要 2 个引脚,但它做成 4 个引脚主要有这两个原因:

-

机械稳固性: 4 个脚焊在板子上比 2 个脚更稳,不容易被手指按得松动或脱落。

-

内部连通(跳线作用):

-

Pin 1 和 Pin 2 在开关内部是永远连通的(通常是同一侧的两个脚,或者对称的两个脚,具体看厂家)。

-

Pin 3 和 Pin 4 在开关内部也是永远连通的。

-

动作原理: 当你按下按钮时,金属弹片变形,把 (1,2) 这一组 和 (3,4) 这一组 接通。

-

1.3. 原理图中的画法(红线的意思)

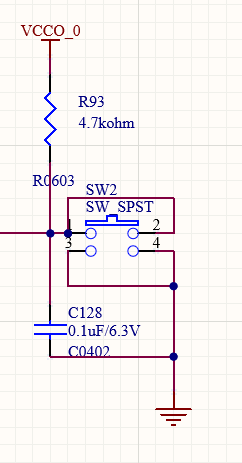

在原理图 SW2 中,画法非常严谨(或者用的元件库比较规范):

-

特意用红色的导线把 Pin 1 和 Pin 2 连起来,把 Pin 3 和 Pin 4 连起来。

-

目的: 这是为了确保在 PCB 画板时,这 4 个焊盘都能正确连接到网络上。如果不连,有时候软件会以为只需要接其中一个脚,导致机械强度不够。

总结

这就是一个几十分钱的普通轻触开关 ,在这里用作 复位按键 (Reset Button) ,按下后会把 FPGA_PROGRAM_B 信号拉到地(GND),让 FPGA 重新配置。

2.机械强度

简单来说,"机械强度不够" 指的是:当你用力按按钮时,按钮可能会被你**"按掉"或者焊盘被"撕下来"**。这背后涉及到一个 PCB 设计中非常实用的小细节:

2.1. 按钮不仅是电子元件,它是"受力件"

电阻、电容焊在板子上,平时没人去碰它们。但按键不一样,它是用来"按"的。

-

每次你按下开关,都会对它施加一个向下的压力 ,甚至可能带有侧向的推力(如果手指滑了)。

-

这个力最终完全由底部的焊锡和**PCB板上的铜皮(焊盘)**来承受。

2.2. 为什么"不连线"会导致强度变低?

这就是之前提到的"软件"和"物理"的联动关系。

-

场景 A:原理图上只连了 Pin 1 和 3(Pin 2, 4 悬空)

-

软件行为: 画 PCB 时,软件认为 Pin 2 和 Pin 4 是"没用的孤儿"。铺铜(Ground Pour)的时候,为了避免短路,大面积的铜皮会自动避开这两个脚,留出缝隙。

-

物理结果: 这两个脚的焊盘就像孤零零的小岛,仅仅靠那一小块铜皮粘在玻璃纤维板(FR4)上。

-

后果: 只有 2 个脚受力。当你用力按时,这两个"孤岛"焊盘很容易连着焊锡一起被撕裂 或剥离。

-

-

场景 B:原理图上把 4 个脚都连好了(比如都连到 GND)

-

软件行为: 画 PCB 时,软件认为这 4 个脚都是"自己人"。如果你铺了大面积的 GND 铜皮,铜皮会通过"十字连接(热焊盘)"直接抓住这 4 个脚。

-

物理结果: 此时,这 4 个焊盘不再是孤岛,而是和大半个板子的铜皮连为一体。

-

后果: 4 个脚同时受力,而且因为连着大片铜皮,焊盘牢牢地"抓"在板子上,怎么按都不容易掉。

-

2.3. 总结

所谓"机械强度不够",就是怕你按得太猛,把焊盘给按掉了。

最佳实践:在原理图里画红线一样,把 1-2 短接,3-4 短接。这样在 PCB 里,4 个脚都会被强行连入电路网络(通常会有导线或铜皮拉住它们),就像给椅子钉稳了 4 条腿,绝对比只钉 2 条腿要结实得多。