一.使用工具仿真

使用FUXI关联modelsim直接仿真,这种操作一般是在纯逻辑代码,没有IP核时,使用最为方便,但是如果有IP,这种操作方法容易报错,所以做仿真之前做好选择

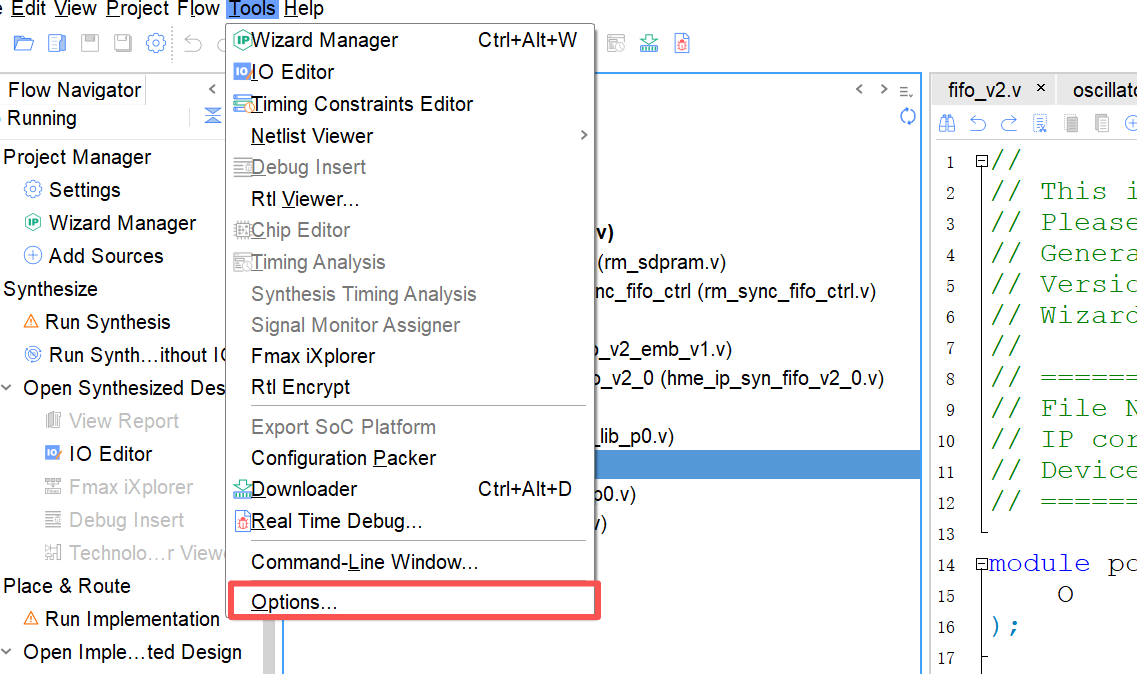

打开FUXI工程,在Tools中选择options选项

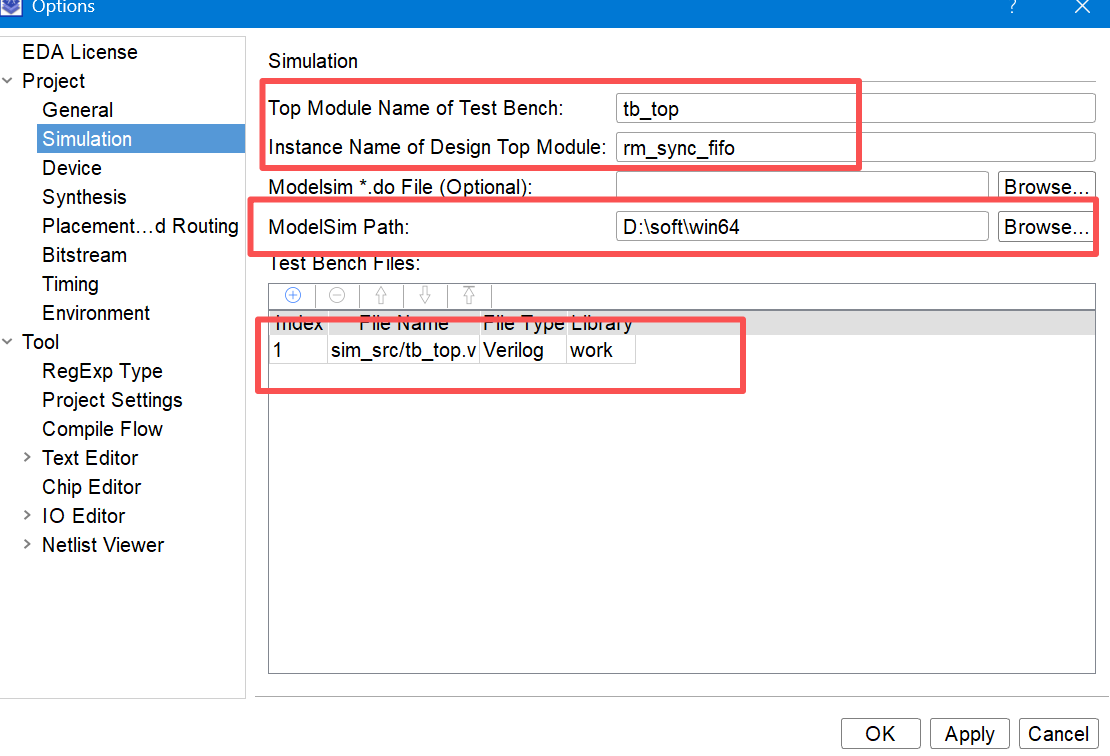

添加modelsim仿真工具的路径,然后添加仿真代码

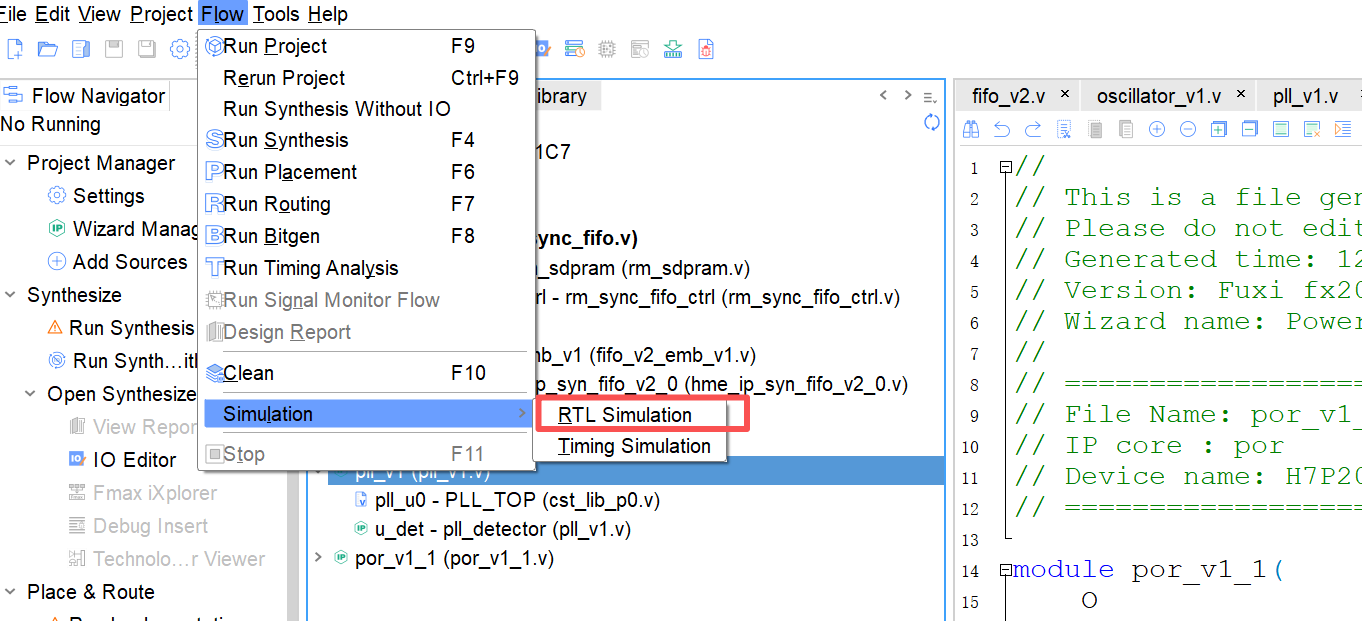

选择Flow中的RTL仿真,调用modelsim仿真

选择Flow中的RTL仿真,调用modelsim仿真

二.使用脚本仿真

二.使用脚本仿真

使用脚本仿真,需要四个文件:files.f文件,run_sim.bat文件,start.do文件,仿真testbench代码

下面一一介绍哦

1.files.f文件 这里面的路径是我的电脑的路径,操作时需要更换为自己的路径

添加仿真库文件,RTL源代码

D:/Fuxi/2025-03-28-win64-rel-99/data/lib/p0_sim.v

../src/ip/pll_v1.v

../src/ip/por_v1_1.v

../src/ip/oscillator_v1.v

../src/ip/emb_v1.v

../src/top.v2.start.do文件 : 汇总编译,设置波形的命令,其中第三步里面的lblock需要更换为自己的tb名.第四步里面的tb_top同样是举例子,需要更换为你自己的tb名

#Step 1: Create and Map the work lib

vlib work

vmap work work

#Step 2: Compile all the files

vlog -64 -sv +acc -incr +define+SIM -timescale 1ns/1ns -work work -f files.f -l rtl.log

#Step 3: Start the simulator, log all waveforms, load wave file and run

vsim -voptargs="+acc" -sva +define+SIM -c work.lblock -l sim.log -wlfdeleteonquit

#Step4: No need to add waveform signals in advance, like VCS, you can directly pull the signal to view the waveform. But it will consume computer storage space.

log -r /tb_top/*

#Step 5: Set the window types

view wave

view structure

view signals3.run_sim.bat文件 操作时,双击run_sim.bat文件,调用start.do文件进行仿真

echo pause

::删除Modelsim生成的相关文件

RD work /s /q

DEL transcript vsim.wlf /q

vsim -do start.do

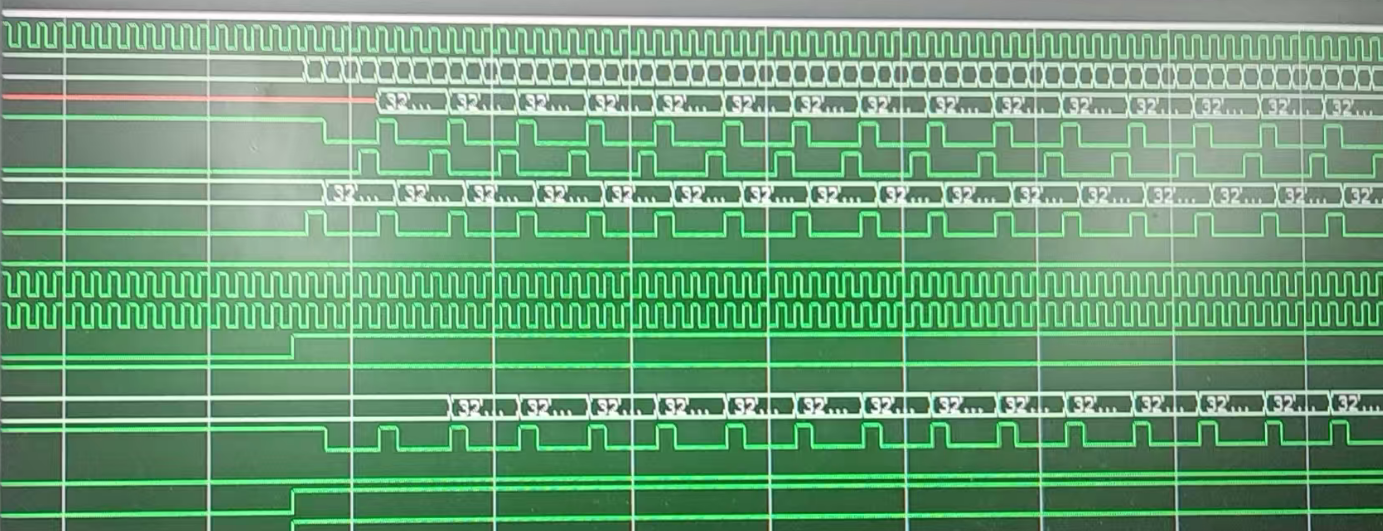

pause然后你就可以看到modelsim启动,看到美丽的波形,帮助你进行调试