这里记录三种仿真方式:

第一种是将verilog文件一个一个敲在终端上进行仿真;

第二种是将多个verilog文件的文件路径整理在一个文件中,然后进行仿真;

第三种是利用makefile文件进行仿真;

以8位加法器为例:

一位加法器:

module fa(a, b, cin, sum, cout);

input a, b, cin;

output sum, cout;

assign {cout, sum} = a + b + cin;

endmodule以一位加法器组成的4位加法器:

module add4(a, b, cin, sum, cout);

input [3:0] a, b;

input cin;

output cout;

output [3:0] sum;

wire [3:1] c;

fa u1(a[0], b[0], cin, sum[0], c[1]);

fa u2(a[1], b[1], c[1], sum[1], c[2]);

fa u3(a[2], b[2], c[2], sum[2], c[3]);

fa u4(a[3], b[3], c[3], sum[3], cout);

endmodule以4位加法器组成的8位加法器

module add8(a, b, cin, sum, cout);

input [7:0] a, b;

input cin;

output cout;

output [7:0] sum;

wire c4, c8_0, c8_1;

wire [7:4] sum_0, sum_1;

add4 u1(a[3:0], b[3:0], cin, sum[3:0], c4);

add4 low_add(a[7:4], b[7:4], 1'b0, sum_0, c8_0);

add4 high_add(a[7:4], b[7:4], 1'b1, sum_1, c8_1);

assign sum[7:4] = c4?sum_1:sum_0;

assign cout = c4?c8_1:c8_0;

endmoduletestbench

module addertb;

reg [7:0] a_test, b_test;

wire [7:0] sum_test;

reg cin_test;

wire cout_test;

reg [17:0] test;

add8 u1(a_test, b_test, cin_test, sum_test, cout_test);

initial

begin

for (test = 0; test <= 18'h1ffff; test = test +1) begin

cin_test = test[16];

a_test = test[15:8];

b_test = test[7:0];

#50;

if ({cout_test, sum_test} !== (a_test + b_test + cin_test)) begin

$display("***ERROR at time = %0d ***", $time);

$display("a = %h, b = %h, sum = %h; cin = %h, cout = %h",

a_test, b_test, sum_test, cin_test, cout_test);

$finish;

end

#50;

end

$display("*** Testbench Successfully completed! ***");

$finish;

end

endmodule1.第一种:将verilog文件一个一个敲在终端上进行仿真:

在存在verilog文件的文件夹内,打开终端,输入以下命令

1.1 先进行编译:

vcs fa.v addertb.v add8.b add4.v -l readme.log +v2k -debug_all1.2 再进行仿真:

./simv -l run.log1.3 打开图形化界面DVE

./simv -gui1.4 在选中所有信号,再右键add to wave,再new wave view

1.5 最后输出波形

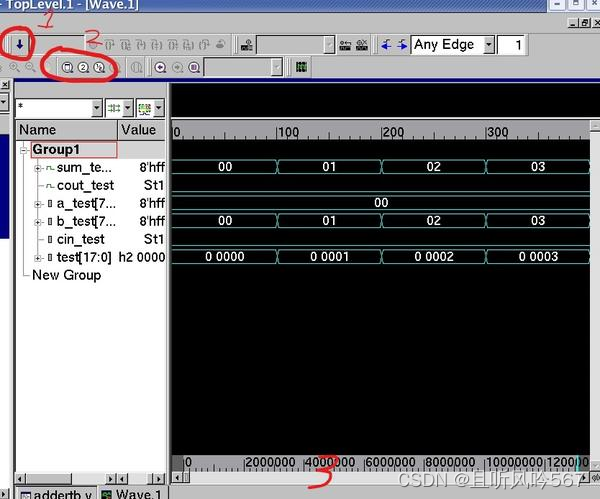

点击1处的小箭头,便有波形出现。使用2处的三个按钮(预览全局、放大和缩小)调整波形。在3处鼠标左键按住不动,左右拖动即可选取一个观察的时间范围。

- 第二种将多个verilog文件的文件路径整理在一个文件中,然后进行仿真

2.1 将verilog文件路径放在一个文件中,文件命名为file.f

find -name '*v' > file.f

gvim file.f2.2 再进行编译

vcs -f file.f -l readme.log +v2k -debug_all2.3 编译后,再进行仿真,图形化界面和输出波形与第一种方法类似

- 第三种是利用makefile文件进行仿真

3.1先编写makefile文件,文件名为simv

.PHONY:com sim clean

OUTPUT = simv

VCS = vcs -sverilog +v2k -timescale=1ns/1ns \

-debug_all \

-o ${OUTPUT} \

-l compile.log \

SIM = ./${OUTPUT} -l run.log

com:

${VCS} -f file.f

sim:

${SIM}

clean:

rm -rf ./csrc *.daidir *.log simv* *.key3.2 再进行编译,打开终端,输入

make com3.3 再进行仿真,输入

make sim3.4 再打开图形化界面

./simv -gui参考资料: