目录

[一、存储器的基本概念 80](#一、存储器的基本概念 80)

1)存储容量存储容量)

2)单位成本单位成本)

3)存储速度存储速度)

[二、主存的基本组成 87+89](#二、主存的基本组成 87+89)

[三、SRAM vs DRAM 86](#三、SRAM vs DRAM 86)

[1)破坏性读出 and 需要再生](#1)破坏性读出 and 需要再生)

1)集中刷新集中刷新)

2)分散刷新分散刷新)

3)异步刷新异步刷新)

[1)非破坏性读出 不需要重生](#1)非破坏性读出 不需要重生)

[四、ROM (Read-Only Memory) 88](#四、ROM (Read-Only Memory) 88)

[1.MROM(Mask) 掩模式·····](#1.MROM(Mask) 掩模式·····)

[2.PROM(Programable) 一次可编程·····](#2.PROM(Programable) 一次可编程·····)

[3.EPROM(Erasable) 可擦除可编程·····](#3.EPROM(Erasable) 可擦除可编程·····)

[(1)UVEPROM 紫外线擦除](#(1)UVEPROM 紫外线擦除)

[(2)EEPROM (E^2PROM) 电擦除](#(2)EEPROM (E^2PROM) 电擦除)

[五、提高主存速度 90](#五、提高主存速度 90)

[2.多模块存储器 90](#2.多模块存储器 90)

[六、主存与CPU之间的连接 101](#六、主存与CPU之间的连接 101)

[七、外存 109](#七、外存 109)

[2.独立冗余磁盘阵列 RAID](#2.独立冗余磁盘阵列 RAID)

[八、固态硬盘 SSD 111](#八、固态硬盘 SSD 111)

[4. vs 机械接盘](#4. vs 机械接盘)

[6. 联系 OS](#6. 联系 OS)

[九、Cache 115](#九、Cache 115)

(3)cpu修改Cache的data,则如何保持与主存中的原data的一致性

[十、主存与Cache之间的映射关系 118](#十、主存与Cache之间的映射关系 118)

[十一、Cache的替换算法 122](#十一、Cache的替换算法 122)

[十二、Cache写策略 123](#十二、Cache写策略 123)

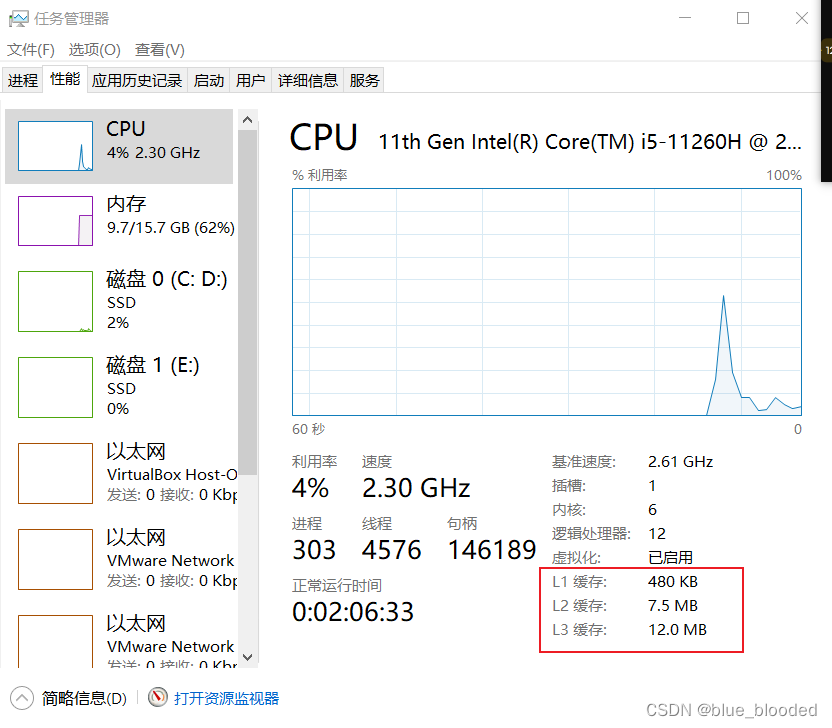

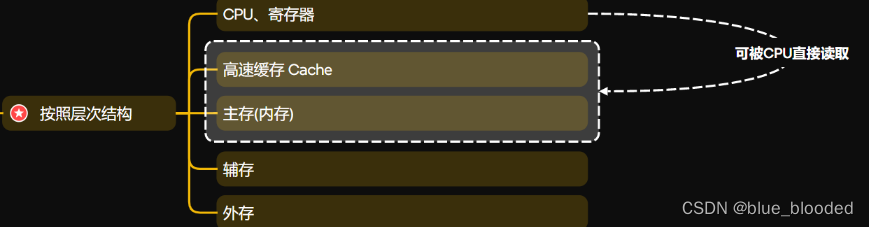

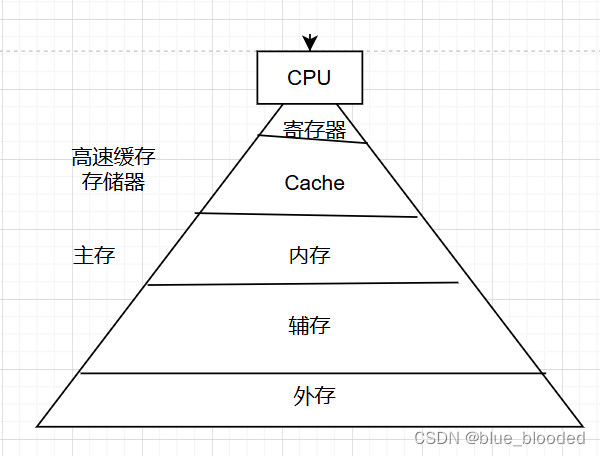

一、存储器的基本概念 80

1.按照层次结构

Attn:①寄存器集成在CPU中

②辅存和外存的区分不大

2.按照各种分类

(41)存储介质

半导体:Cache 磁介质:disk、硬盘 光介质:光盘

(2)存取方式

随机存储器(RAM):EPROM、SRAM、DRAM

顺序存取存储器(SAM):磁带

直接存取存储器(DAM):磁盘(SSD) 、光盘 (CD-ROM)

相联存储器(内存存储器)(CAM):快表

只读存储器 (ROM)

ATTN:不要根据东西的名称分,要根据具体内容

(3)内存是否可更改

只能读ROM

可读写else

(4)信息的可保存性

断电是否发生data丢失:易失性存储器

RAM

非易失性存储器:ROM、磁性存储器、光存储器

(5)读出之后data是否破坏

读了之后摧毁data / 不摧毁:破坏性读出 DRAM and 非破坏性输出 SRAM

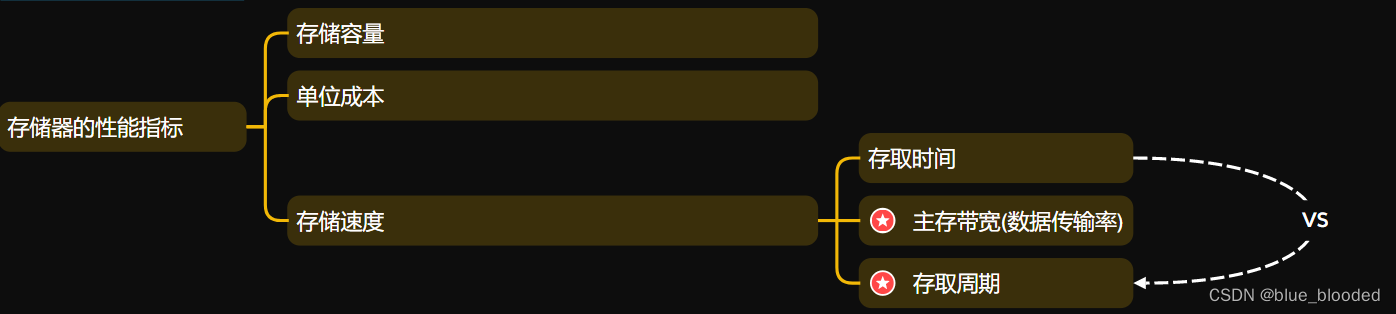

3.存储器的性能指标

1)存储容量

2)单位成本

每bit价格

3)存储速度

存储时间、存取周期、主存带宽(data传输率)

存储周期 = 存储时间+恢复时间

主存带宽 :每秒读写的data

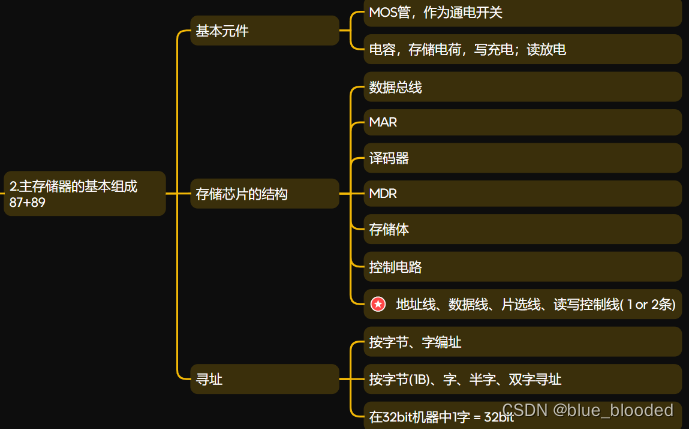

二、主存的基本组成 87+89

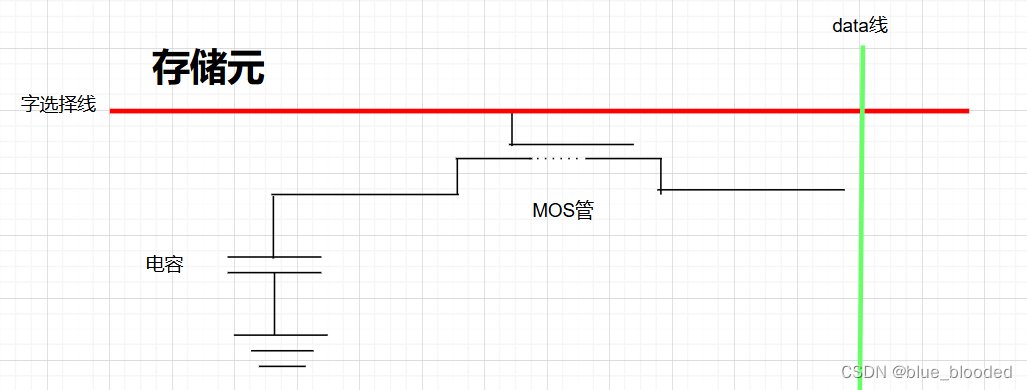

1.基本元件

存储元 : 电容 + MOS管

电容存储电荷,写就充电,读就放电

工作原理:根据高低电平(电荷)

因为电容这边接地,为0V,so用高电平的时候MOS导电,电容充电表示1,之后断开MOS管,电荷就保存在了电容中,在另一端读就为1

低电平MOS绝缘,电容还是0V,无电荷0,在另一端读就为0

多个存储元组成存储单元(存储字),多个存储单元组成存储矩阵(存储体)

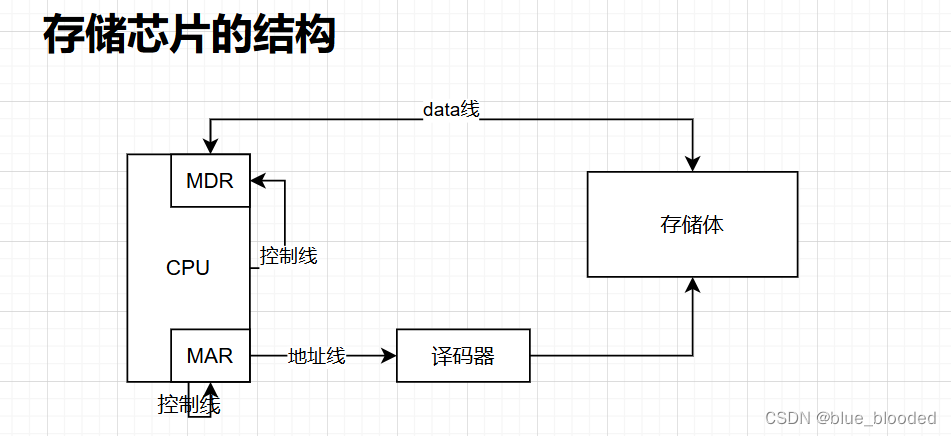

2.存储芯片的结构

CPU发出指令,通过MAR获取进行读写的内存地址,通过译码器进行选择哪一块存储芯片的读写,读完之后通过data线送到MDR中,整体过程由CPU控制

MAR存储nbit数据,则译码器就有2^n个存储单位

读写控制线可以由一条or两条线组成

①一条 WE (有上划线) 低写高读

②两条线 WE (有上划线)写 OE(有上划线)读

片选控制线:选择读写内存中的那一块存储芯片上的data,低电平确定

CS (有上划线)、CE (有上划线) ,上划线表示低电平激活

3.寻址

按字节or 字编址

按字节 、字、半字、双字寻址

ATTn:在32bit机器中,1字= 32bit = 4B

三、SRAM vs DRAM 86

1.DRAM

(1)工作原理

运用栅极电容存储信息,1个MOS管,即存储元,多个存储元组成存储体

(2)特点

1)破坏性读出 and 需要再生

通过电容充放电进行读写,so读的时候会放电,电容中的电荷没了,so是破坏性读出

放电之后需要重新充电,"再生"

2)需要刷新

即使不重新读写,电荷也会慢慢流失,so需要定期刷新,三种方式

刷新与重生dis:刷新是按行为单位的

3)分两次送行列地址

地址复用技术

(3)DRAM刷新

1)集中刷新

计算出全部刷新需要的时间,则else进行CPU读取,留下这些时间进行全部刷新,这一部分时间称作死区,此时CPU不能读取

2)分散刷新

读一下刷一次,dis:存取周期翻倍

3)异步刷新

计算出全部刷新的时间,将其分布到每个刷新周期之间,这样就分散了死区,cpu不会等待时间过长

(4)DRAM地址复用技术

未使用之前,1条地址线对应1存储元,译码器连着这么多的线,设计比较难,so使用行译码器和列译码器,条数就开方了,并且芯片引脚也减少

2.SRAM

(1)工作原理

使用6个MOS管,so会存储信息

(2)特点

1)非破坏性读出 不需要重生

2)不需要刷新

3)同时送行列地址

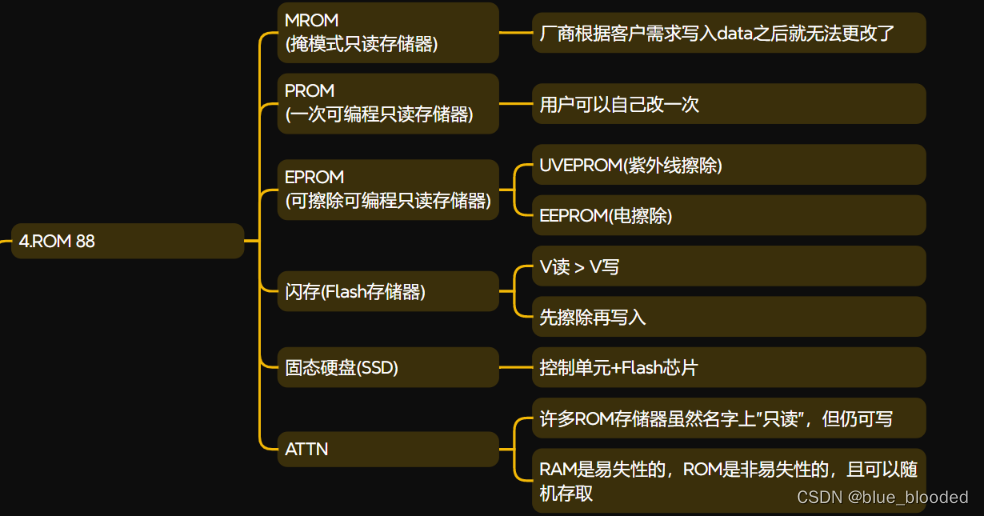

四、ROM (Read-Only Memory) 88

1.MROM(Mask) 掩模式·····

厂家根据用户需求进行设计,之后任何人不能再修改

2.PROM(Programable) 一次可编程·····

用户可DIY,保存之后不能再修改

3.EPROM(Erasable) 可擦除可编程·····

(1)UVEPROM 紫外线擦除

紫外线照射 8~20min

(2)EEPROM (E^2PROM) 电擦除

4.闪存(Flash存储器)

先擦除后写 so V读 > V写

5.固态硬盘(SSD)

控制单元 + Flash芯片

6.ATTN

(1)许多ROM依然可以写

(2)ROM是非易失性的,也可以随机存取

五、提高主存速度 90

1.reason

存取周期 = 存取时间 + 恢复时间

恢复时间占主要时间,且恢复期间cpu无法读写

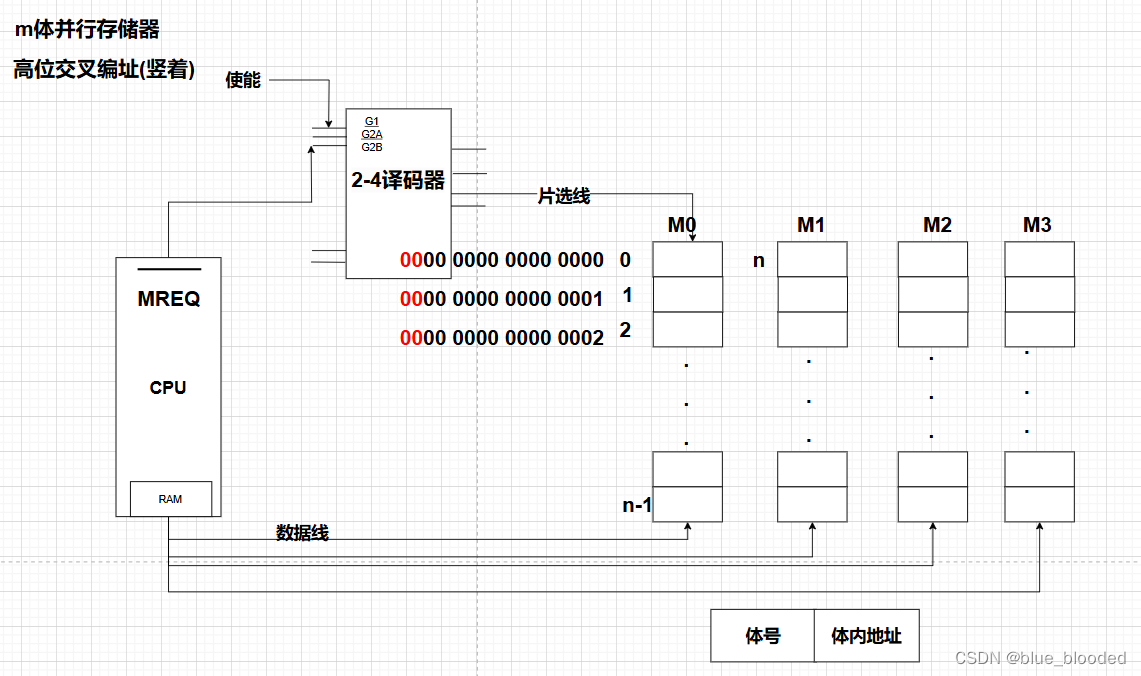

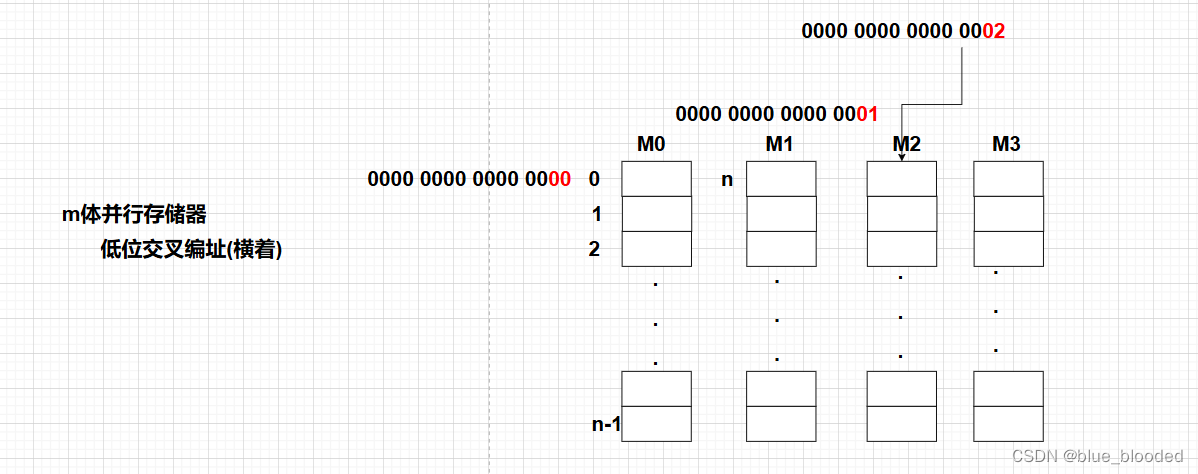

2.多模块存储器 90

(1)多体并行存储器

多体模块(理解成内存条)组成

1)高位交叉编址

体号+体内地址,体号表示选择的是哪一块,体内表示模块内的第几个,"竖着编址"

2)低位交叉编址

体内地址+体号,"横着编址"

best 模块数m = 存取周期T/存取时间r

if 想cpu不停止,则 m>= T/r ;m> T/r,模块会有空闲,无法达到最高效,增加成本;m<T/r,cpu仍需等待

一般是进行字扩展,组与组之间串联,由此确定模块的个数

(2)单体并行存储器

将m体模块合并成一个模块,每次并行读出m个连续的字,so每个存储单元存储m个字,总线宽度也为m个字

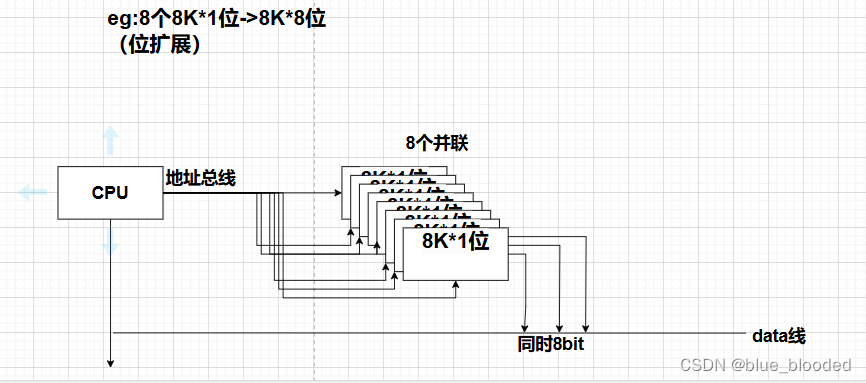

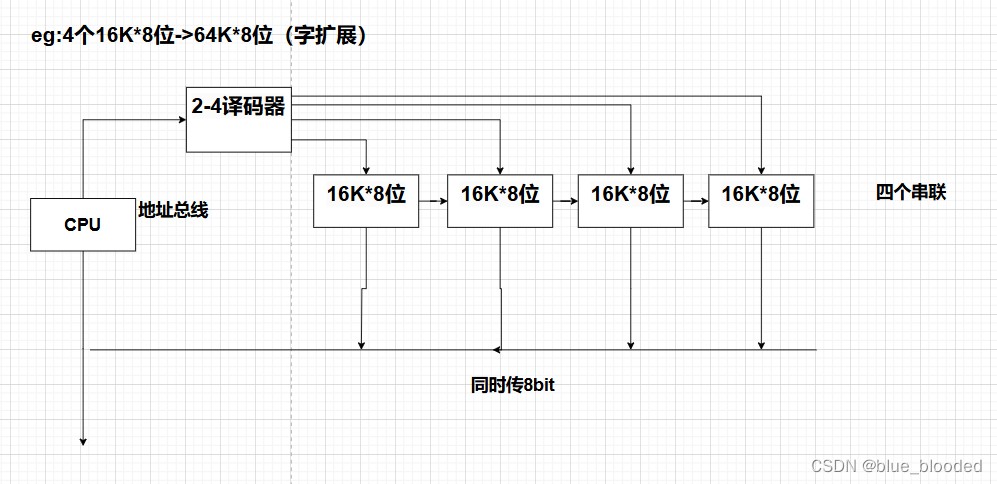

六、主存与CPU之间的连接 101

1.存储器芯片的基本结构

移码驱动电路+存储体+读写电路+地址线、片选线、数据线、读/写控制线

2.位扩展

芯片并联,增加data总路读写的效率

3.字扩展

芯片串联,扩容

(1)线选法

直接连接,1地址线--1芯片(组)

(2)译码片选法

使用译码器,n地址线 -- 2^n 芯片(组)

4.字位同时扩展

结合位扩展+字扩展

七、外存 109

1.disk原理

(1)disk组成

磁盘驱动器、磁盘控制器、盘片

(2)性能指标

1)容量

2)记录密度

道密度、位密度、盘密度

因为每条磁道中data数量相同,so外道密度<内道密度

3)平均存取时间

寻道时间、旋转延迟时间、传输时间

4)data传输率

磁盘存储器再单位时间内想主机传送data的字节数

Dr = rN (转速 * 每条磁道容量)

(3)硬盘地址

柱面扇

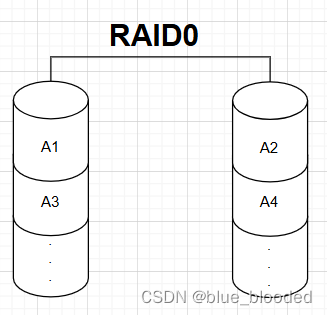

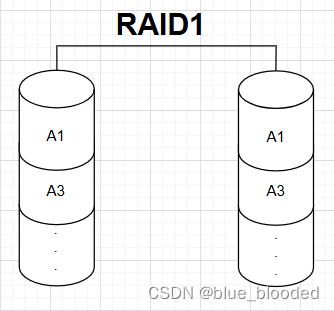

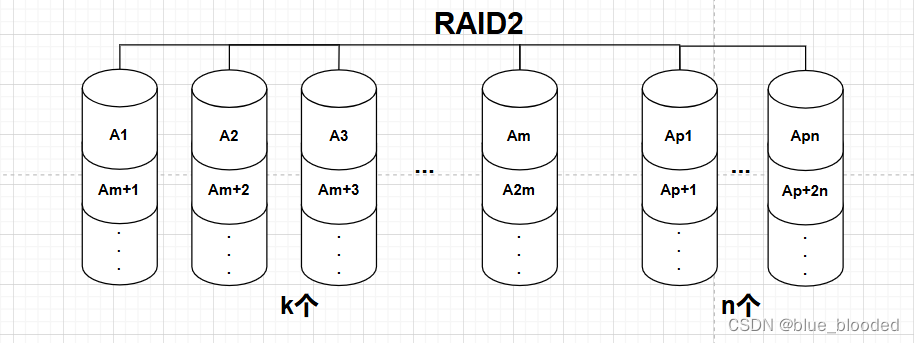

2.独立冗余磁盘阵列 RAID

因为 数据总线发送data时只能1bit的发,so用串-并交换电路,能同时nbit

实现:多个独立的物理disk组成一个独立的逻辑盘

RAID的应用是在实现手段,安全性差距,等级越大越安全

(1)RAID0

无冗余的,无校验的磁盘阵列,(类比低位编址的多体存储器)

disa:不能检验,错了就错了

(2)RAID1

镜像磁盘阵列(有冗余,有检验)

disa:冗余50%,检验就比较另一份

(3)RAID2

采用可以纠错的海明码的磁盘阵列,,采用k位disk和n位海明校验码

eg:4个disk则最少需要3位海明校验码

reason:k+n位最多表示2^(k+n) -1种错误,有一种是没错

so 2^(k+n) -1 >= k+n

参考视频:

(4)RAID3~RAID5(了解)

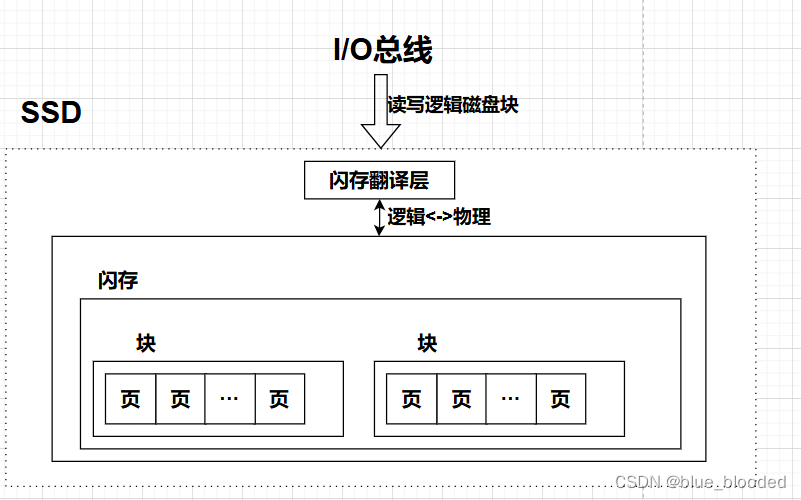

八、固态硬盘 SSD 111

1.原理

闪存技术 、可电擦除

2.组成

闪存翻译层 + Flash Chips

3.读写性能

以页为单位读写(类比disk的块)

以块为单位进行擦除,擦完之后才能写,即使块中有空页,也不能写

支持随机访问

4. vs 机械接盘

SSD快、安静、贵,擦除次数太多就坏了

5.磨损均衡技术

因为擦除太多会损坏,so采用方法

(1)动态擦除 --选擦除次数min

(2)静态擦除 -- 读写需求大的使用擦除次数少的,只读的使用擦除次数多的

6. 联系 OS

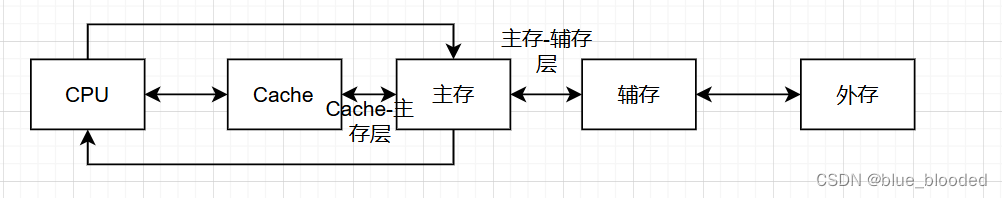

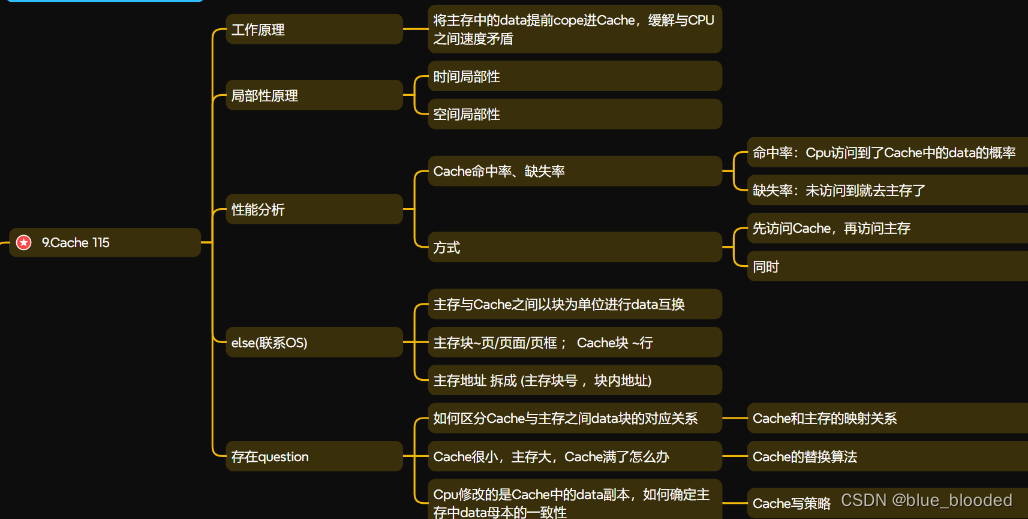

九、Cache 115

1.工作原理

SRAM构建,将主存中的部分data先拷贝到Cache中,缓解CPU和主存之间的速度矛盾

2.局部性原理

时间和空间

3.性能分析

(1)Cache命中率、缺失率

Cache命中率 :CPU访问Cache的概率

H = Nc /(Nc +Nm)

平均访问时间Ta= Htc + (1-H)(tc+tm) 先访问Cache再主存

平均访问时间Ta= Htc + (1-H)tm 同时访问

(2)方式

先访问Cache再主存;同时Cache 和主存

4.else(联系OS)

5.存在的question

(1)Cache与主存中data块的对应关系

Cache与主存之间的映射关系

(2)Cache块小,满了咋办

Cache替换算法

(3)cpu修改Cache的data,则如何保持与主存中的原data的一致性

Cache写策略

十、主存与Cache之间的映射关系 118

1.Cache存放data格式

有效位+标记+整块data

有效位表示data是否有效,∵全0也可表示具体data

标记表示data在内存中的pos

2.全相联映射

随便放,有空就行

主存地址 = 块号 + 块内地址

adv:空间利用充分

disa:确定data在内存中的位置较慢

3.直接映射

地址号 mod 块号 ,位置唯一

映射到的块号 = 内存地址低位c

c = log2Cache块数

4.组相连映射

先将Cache块进行分组,然后直接映射入组,组内随意放空地方

十一、Cache的替换算法 122

1.随机算法(RAND)

当Cache满了之后,if有新的内存块要访问,随机替换一个Cache行中的data

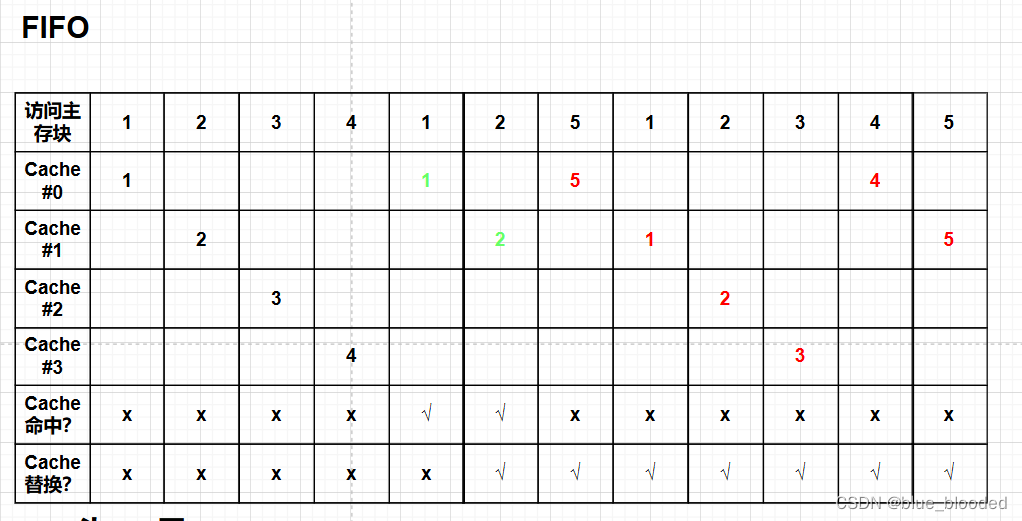

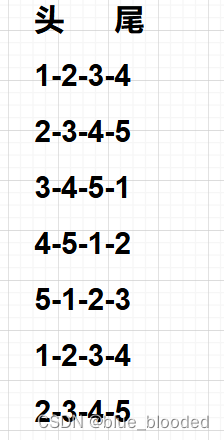

2.先入先出(FIFO)

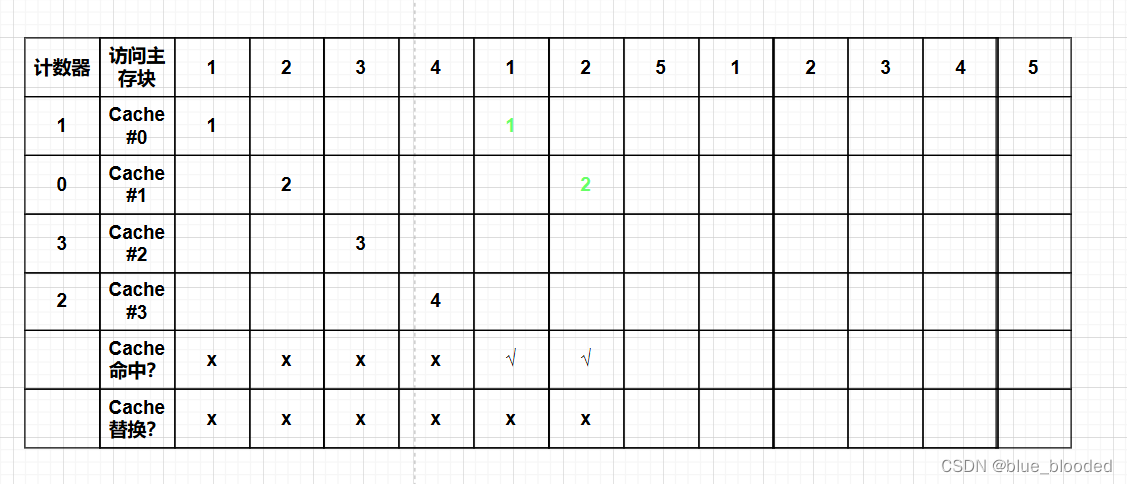

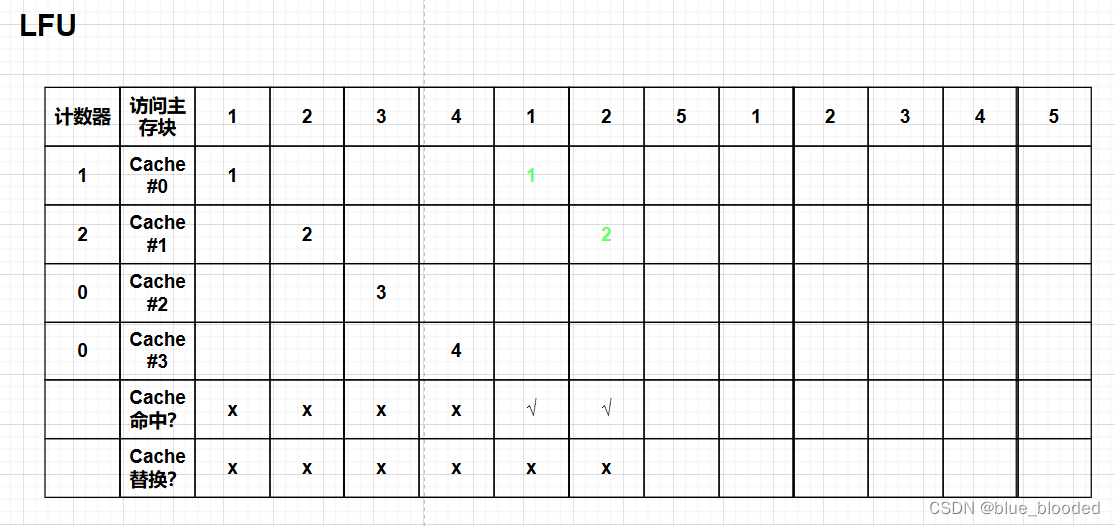

eg:4个Cache行,依次访问1,2,3,4,1,2,5,1,2,3,4,5主存块

绿色表示命中,红色代表替换,(中间相同ele省略)

[tip] 使用辅助队列

由图中后半部分发现频繁替换,称作抖动现象

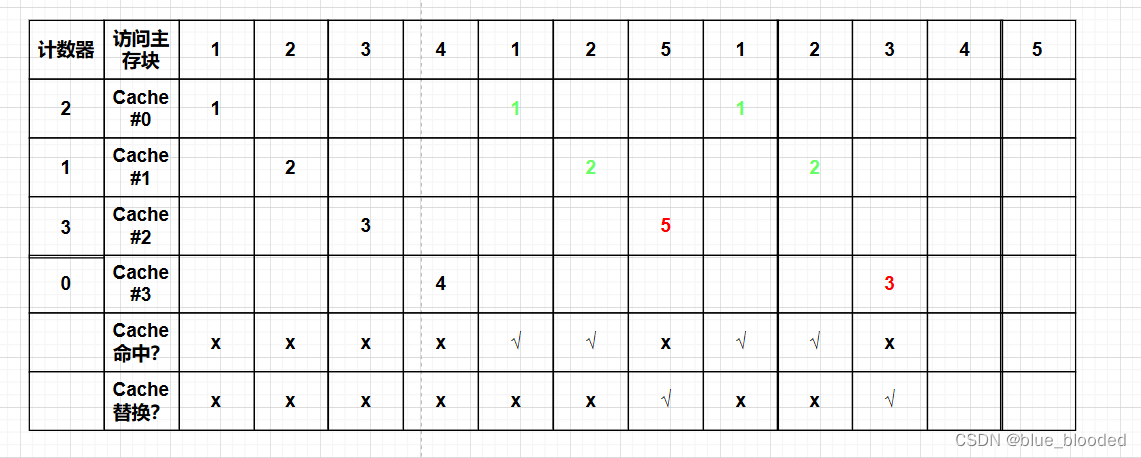

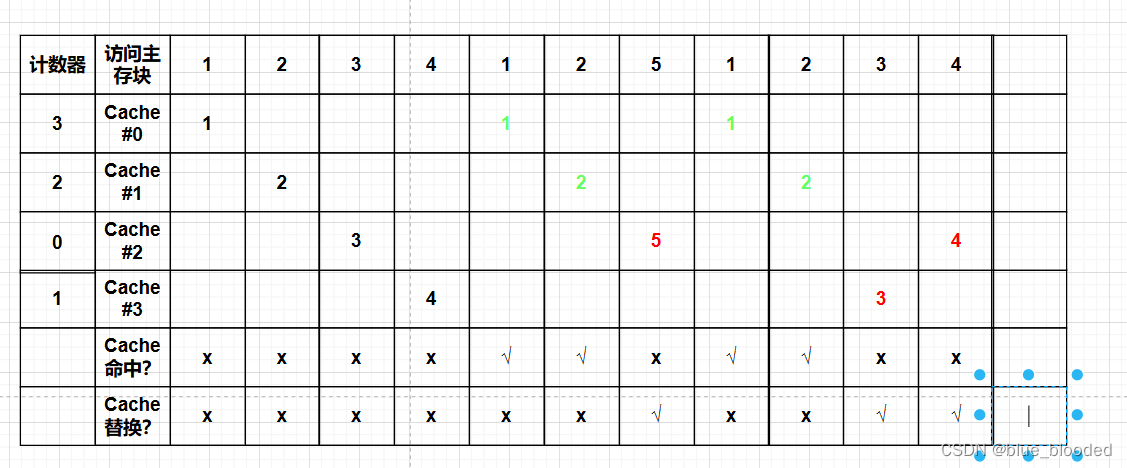

3.最近最少使用算法(LRU)

替换在访问的前几个中没有使用的那一个

(1)手算

往前看,差1个

(2)机器

使用计数器,计数器表示已经几次没有访问该Cache行了,if命中,该块对应清0,else+1;if未命中,有空行,填入Cache,else+1,无空行,找max,剔除,该行置0,else+1

分步解析

此时Cache满了

到5应该替换3,此行置0,else+1

到了3,替换4

到了4,此时最大5,count=3,替换5

到了5,此时最大1,count=3,替换1

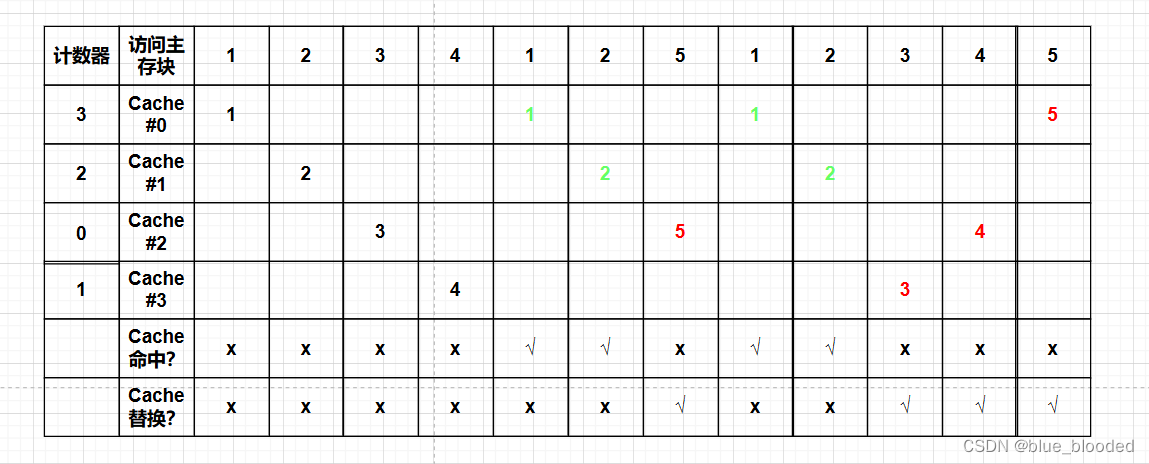

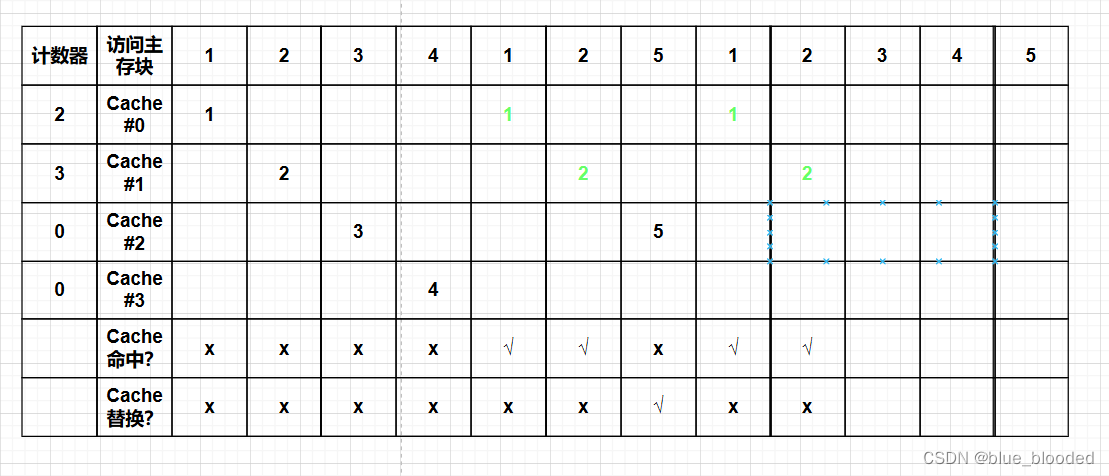

4.最不经常使用算法(LFU)

全局不常用,使用计数器,表示该行Cache访问次数。每次访问一个,if为空,放入Cache行,count+1,if不空,命中,+1,未命中,替换min,if有同,FIFO or 行数小的

逐步分解(先换行号小)

此时3Cache2 、3小,5替3

此时3替5

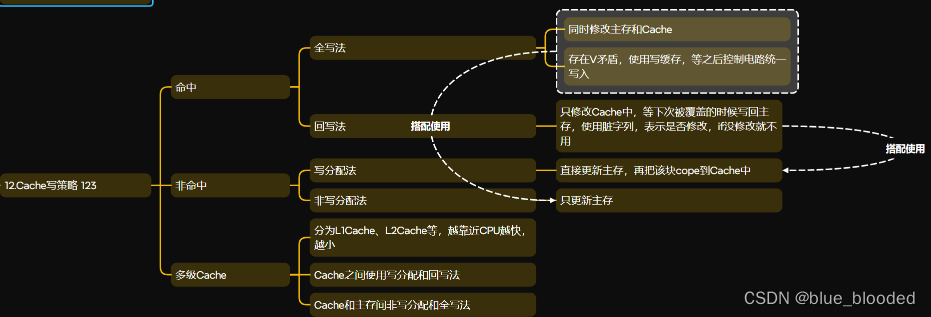

十二、Cache写策略 123

1.命中

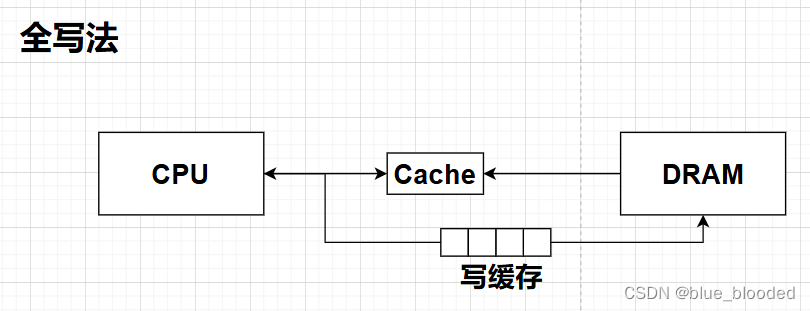

(1)全写法

同时修改主存和Cache,存在速度矛盾,so使用写缓存,等止呕控制电路一块写入

(2)回写法

写入Cache,等Cache中该块被替换时,写入主存

2.未命中

未命中说明去主存中寻找,根据将data放不放入Cache进行分

(1)写分配法

放入Cache

(2)非写分配法

不放入Cache

Attn:非写分配法不放入Cache,全写法全修改,就不需要从主存放入Cache中了,so搭配使用

写分配 和 回写法搭配使用

3.多级Cache

再将Cache进行分级,级越高离CPU越近,容量越小,速度越快