文章目录

- [一、 HLS是什么?与VHDL/Verilog编程技术有什么关系?](#一、 HLS是什么?与VHDL/Verilog编程技术有什么关系?)

- 二、HLS有哪些关键技术问题?目前存在什么技术局限性?

- [三.在win10(或者Ubuntu系统下)安装 Intel 或者 Xilinx 的支持HLS的FPGA编程开发软件(Quartus18或者Vivado18),设置好环境,完成一个入门级的HLS程序,并进行仿真或者实际开发板运行。](#三.在win10(或者Ubuntu系统下)安装 Intel 或者 Xilinx 的支持HLS的FPGA编程开发软件(Quartus18或者Vivado18),设置好环境,完成一个入门级的HLS程序,并进行仿真或者实际开发板运行。)

一、 HLS是什么?与VHDL/Verilog编程技术有什么关系?

HLS

高层次综合(High Level Synthesis, HLS)是Xilinx公司推出的最新一代的FPGA设计工具,它能让用户通过编写C/C++等高级语言代码实现RTL级的硬件功能。随着这款工具的出现,软硬之间的区别越来越模糊,即使你对于硬件完全不懂,你也能编写出符合工程功能要求的RTL代码。

可以将其看作一种简化了学习成本的硬件开发工具,通过使用被大众广泛接受的C/C++等高级语言来实现、操作硬件功能。

HLS与VHDL/Verilog的关系

新兴的HLS与VHDL/Verilog两种工具就像是通往一个目的地的两条不同的路,这三者都只是为人所用的工具,类似于软件开发中的不同编程语言,虽然在效力和功能上互有优劣,但本质上是一类物事。

二、HLS有哪些关键技术问题?目前存在什么技术局限性?

支持的软件编程语言:目前,高层次综合支持的软件编程语言有限,大多数工具支持C/C++和SystemC等语言。因此,开发人员需要在这些语言中编写硬件描述。

复杂性:高层次综合涉及多个优化阶段和复杂的算法,需要大量的计算资源和时间。因此,它对硬件层面的知识和经验要求较高。

可移植性:高层次综合生成的电路可能会受到工具和目标平台的限制,因此需要进行定制化和优化。这可能会限制电路的可移植性和可重用性。

成本问题:高层次综合需要使用专业的工具和硬件平台,这可能会增加开发成本和时间。

三.在win10(或者Ubuntu系统下)安装 Intel 或者 Xilinx 的支持HLS的FPGA编程开发软件(Quartus18或者Vivado18),设置好环境,完成一个入门级的HLS程序,并进行仿真或者实际开发板运行。

安装Xilinx 2018.3相关软件

使用vivado创建HLS------点亮led灯

创建 HLS工程

打开Vivado HLS 2018.3后,点击create new project进行新HLS工程的创建

添加工程文件并编写代码

编写.h头文件(led.h)

c

#ifndef _SHIFT_LED_H_

#define _SHIFT_LED_H_

#include "ap_int.h"

#define CNT_MAX 100000000

//#define CNT_MAX 100,100M时钟频率下计数一秒钟所需要的计数次数

#define FLASH_FLAG CNT_MAX-2

// typedef int led_t;

// typedef int cnt_t;

typedef ap_int<1> led_t;

typedef ap_int<32> cnt_t;

void flash_led(led_t *led_o , led_t led_i);

#endifled.cpp

c

#include "led.h"

void flash_led(led_t *led_o , led_t led_i){

#pragma HLS INTERFACE ap_vld port=led_i

#pragma HLS INTERFACE ap_ovld port=led_o

cnt_t i;

for(i=0;i<CNT_MAX;i++){

if(i==FLASH_FLAG){

*led_o = ~led_i;

}

}右键点击Test Bench选择New File创建test_led.cpp文件并编写以下内容

c

#include "led.h"

#include <stdio.h>

int main(){

led_t led_i=0x01;

led_t led_o;

const int SHIFT_TIME = 4;

int i;

for(i=0;i<SHIFT_TIME;i++){

flash_led(&led_o , led_i);

led_i = led_o;

printf("shift_out is %d \n",(int)(led_o&0x01));

}

}

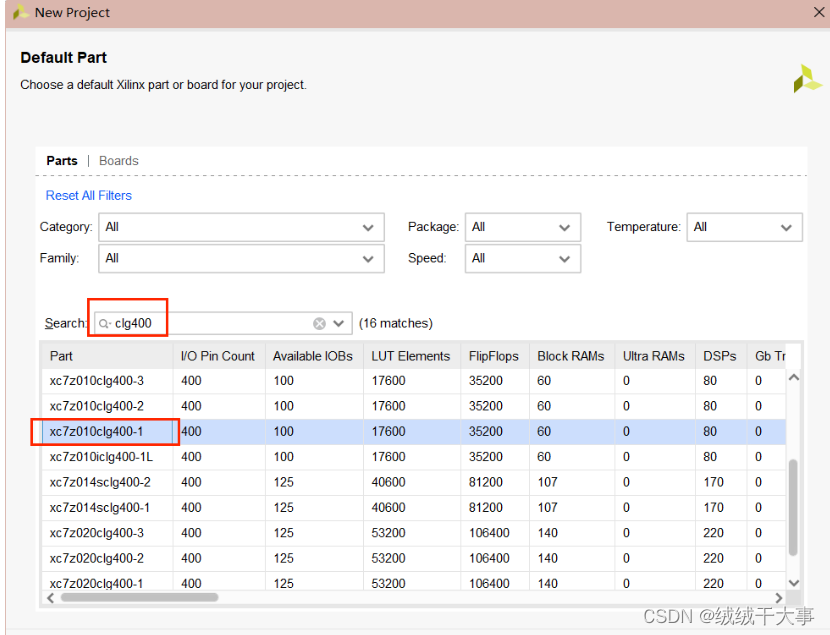

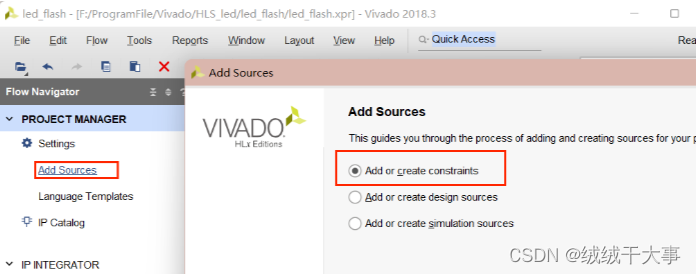

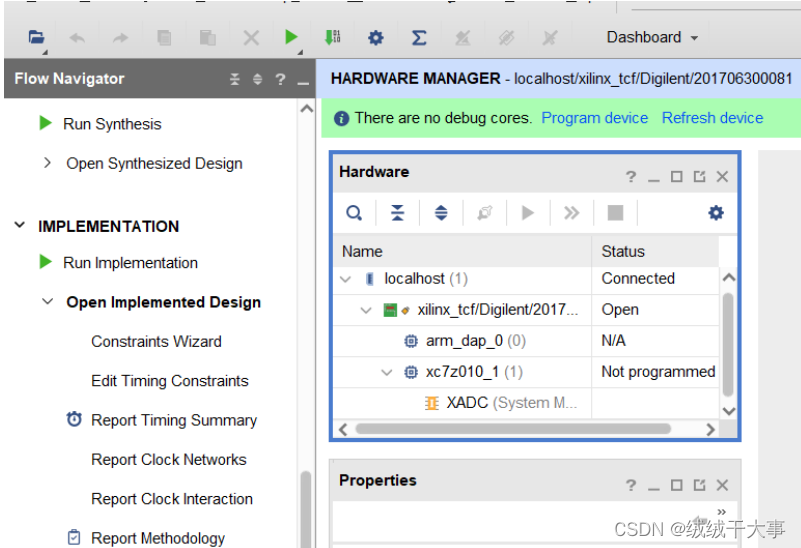

创建Vivado工程

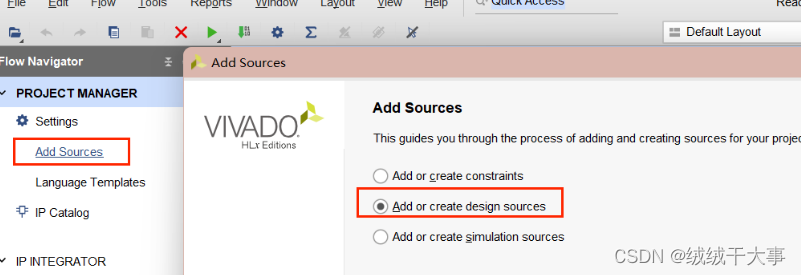

导入HLS生成的IP核

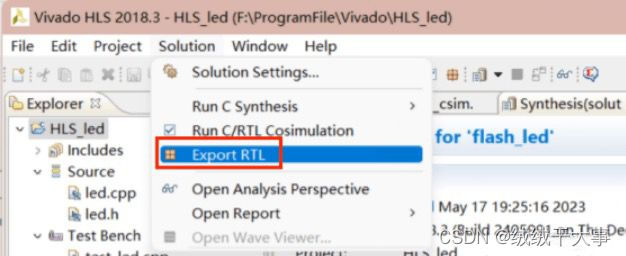

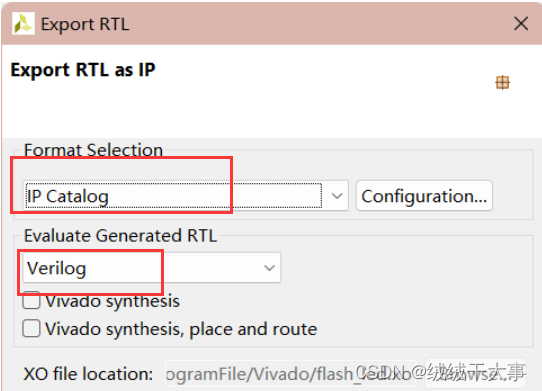

选择Solution->Export RTL

添加实验代码

c

`timescale 1ns / 1ps

module flash_led(

input wire clk ,

input wire rst_n ,

output wire led_o

);

wire rst ;//同步复位

wire ap_ready ;//当前可以接收下一次数据

reg ap_start ;//IP 开始工作

reg led_i_vld ;//输入数据有效

wire led_o_vld ;

reg led_i ;//输入的 led 信号

wire led_o_r ;

wire ap_done ;

wire ap_idle ;

reg [1:0] delay_cnt ;

assign rst = ~rst_n ;

assign led_o = led_o_r ;

//----------------delay_cnt------------------

always @(posedge clk) begin

if (rst==1'b1) begin

delay_cnt <= 'd0;

end

else if(delay_cnt[1]==1'b0) begin

delay_cnt <= delay_cnt + 1'b1;

end

end

//----------------ap_start------------------

always @(posedge clk) begin

if (rst==1'b1) begin

ap_start <= 1'b0;

end

else if(delay_cnt[1]==1'b1)begin

ap_start <= 1'b1;

end

end

//----------------led_i_vld------------------

always @(posedge clk) begin

if (rst==1'b1) begin

led_i_vld <= 1'b0;

end

else if(delay_cnt[1]==1'b1)begin

led_i_vld <= 1'b1;

end

end

//----------------ap_i------------------

always @(posedge clk) begin

if (rst==1'b1) begin

led_i <= 1'b0;

end

else if(led_o_vld==1'b1)begin

led_i <= led_o_r ;

end

end

flash_led_0 inst_flash_led (

.led_o_V_ap_vld(led_o_vld), // output wire led_o_V_ap_vld

.led_i_V_ap_vld(led_i_vld), // input wire led_i_V_ap_vld

.ap_clk(clk), // input wire ap_clk

.ap_rst(rst), // input wire ap_rst

.ap_start(ap_start), // input wire ap_start

.ap_done(ap_done), // output wire ap_done

.ap_idle(ap_idle), // output wire ap_idle

.ap_ready(ap_ready), // output wire ap_ready

.led_o_V(led_o_r), // output wire [0 : 0] led_o_V

.led_i_V(led_i) // input wire [0 : 0] led_i_V

);

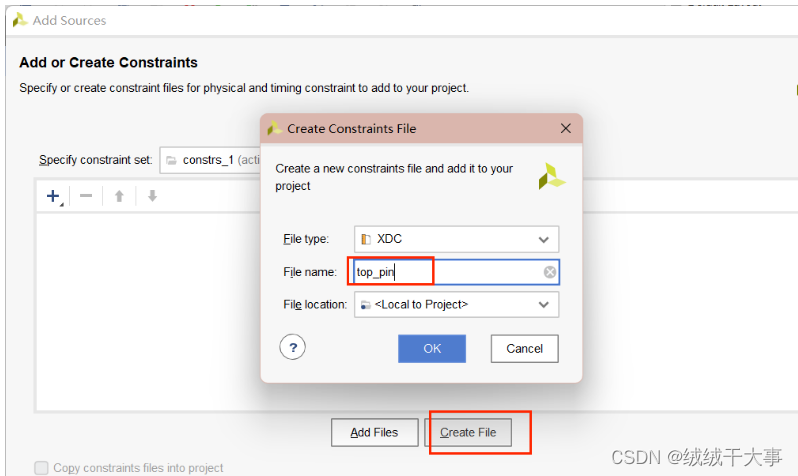

endmodule约束文件编写

c

##############LED define##################

set_property PACKAGE_PIN P15 [get_ports {led_o}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_o}]

##############Reset define##################

set_property PACKAGE_PIN P16 [get_ports {rst_n}]

set_property IOSTANDARD LVCMOS33 [get_ports {rst_n}]

##############50M CLK define##################

create_clock -period 20.000 -name clk -waveform {0.000 10.000} [get_ports clk]

set_property PACKAGE_PIN N18 [get_ports {clk}]

set_property IOSTANDARD LVCMOS33 [get_ports {clk}]编译生成获取结果

参考链接:https://blog.csdn.net/m0_64341369/article/details/139169137