文章目录

[1. 逻辑门电路](#1. 逻辑门电路)

[2. 非门(NOT Gate)](#2. 非门(NOT Gate))

[3. 与门(AND Gate)](#3. 与门(AND Gate))

[4. 或门(OR Gate)](#4. 或门(OR Gate))

[5. 与非门(NAND Gate)](#5. 与非门(NAND Gate))

[6. 或非门(NOR Gate)](#6. 或非门(NOR Gate))

[7. 异或门(XOR Gate)](#7. 异或门(XOR Gate))

[8. 异或非门(XNOR Gate)](#8. 异或非门(XNOR Gate))

[9. 逻辑门总结](#9. 逻辑门总结)

1. 逻辑门电路

在数字电路中,逻辑门是实现逻辑运算的基本单元。常见的逻辑门包括与门(AND)、或门(OR)、非门(NOT)、与非门(NAND)、或非门(NOR)、异或门(XOR)和同或门(XNOR)。下面详细解释这些基础逻辑门及其在digital软件中的仿真。

对于digital软件的安装和配置可以看下面的文章

2. 非门(NOT Gate)

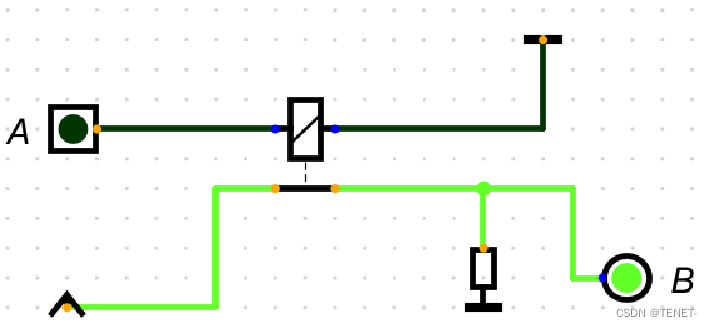

按照下面的顺序在digital中搭建一个非门电路:

- 打开digital软件,从"组件------输入输出"中,选择一个输入和一个输出;

- 从"组件------导线"中选择一个地、一个电源和一个下拉电阻;

- 从"组件------开关"中选择一个继电器;

- 右键点击输入,标签输入A;

- 右键点击输出,标签输入B;

- 右键点击继电器,勾选"闭合继电器";

按照如下电路图连接:连接完成后,选择快捷菜单栏的仿真键开始仿真。

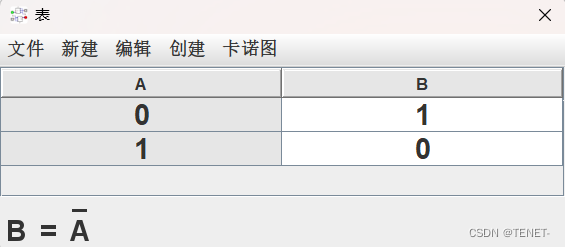

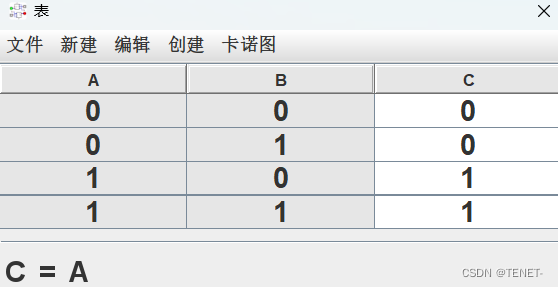

按F9分析可以看到真值表和表达式,这种输入信号和输出信号完全相反的电路,叫做非门

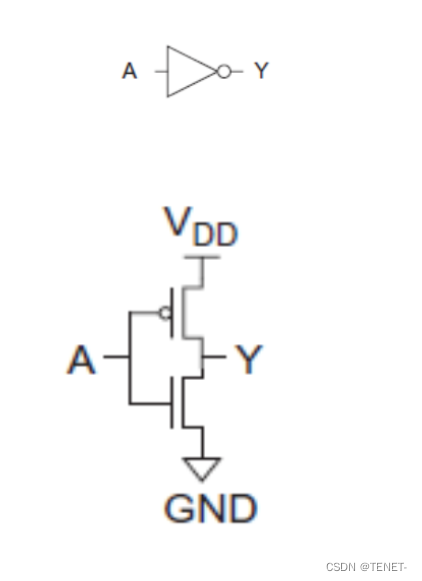

但是这里用继电器 的行为是用在日常电路中,但在集成电路中不会使用继电器,而是使用MOS管来代替,比如NMOS和PMOS,如下所示:

按照这个电路搭建集成电路,上方为PMOS晶体管,下方为NMOS晶体管,这样也可以得到非门的效果。

当输入A为低电平(0)时:

- PMOS导通,NMOS截止。

- 输出为高电平(1)。

当输入A为高电平(1)时:

- PMOS截止,NMOS导通。

- 输出为低电平(0)。

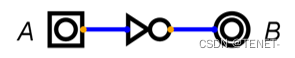

在之后的电路搭建中,直接使用软件自带的各种逻辑门组件更方便。

3. 与门(AND Gate)

- 从"组件------输入输出"中,选择两个输入和一个输出;

- 从"组件------导线"中选择两个地、一个电源和一个下拉电阻;

- 从"组件------开关"中选择两个继电器;

给输入编号A、B,给输出编号C,按照如下图连接:

按F9分析可以看到真值表和表达式,这种只有两路都同时置1就是输出才会置1的电路,叫做与门。

4. 或门(OR Gate)

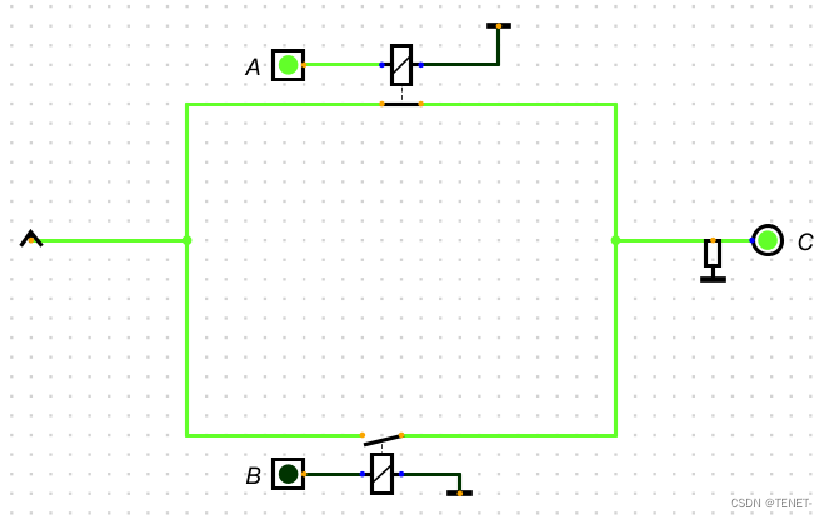

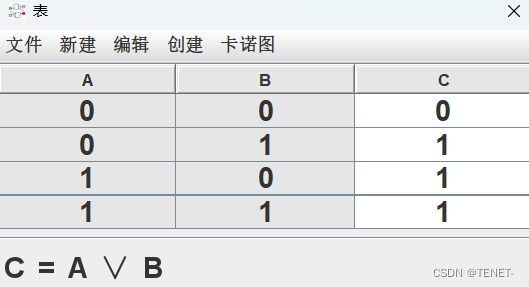

按照如下图搭建电路:

按F9分析可以看到真值表和表达式,这种只要有一路置1就导致输出置1的电路,叫做或门。

5. 与非门(NAND Gate)

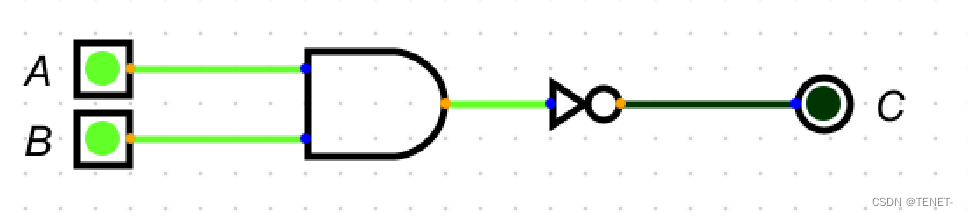

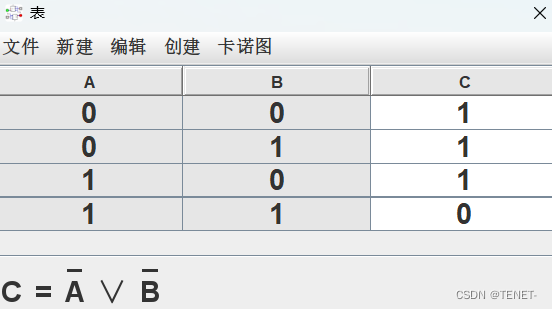

按照如下图搭建电路:

按F9分析可以看到真值表和表达式,这种全1出0,其他出1的电路,叫做与非门。

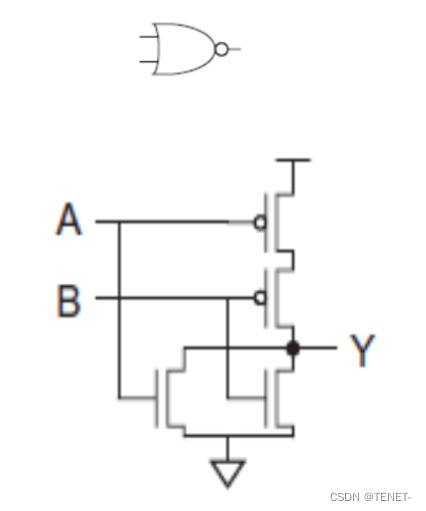

同样的,在集成电路中也是使用MOS管来实现电路。如下所示:

如图搭建电路,并联的为PMOS管,串联的为NMOS管,同样可以实现与非门的效果。

当输入A为低电平(0)时:

- PMOS导通,NMOS截止。

当输入A为高电平(1)时:

- PMOS截止,NMOS导通。

6. 或非门(NOR Gate)

按照如下图搭建电路:

按F9分析可以看到真值表和表达式,这种有1出0,全0出1的电路,叫做或非门。

同样的,在集成电路中也是使用MOS管来实现电路。如下所示:

7. 异或门(XOR Gate)

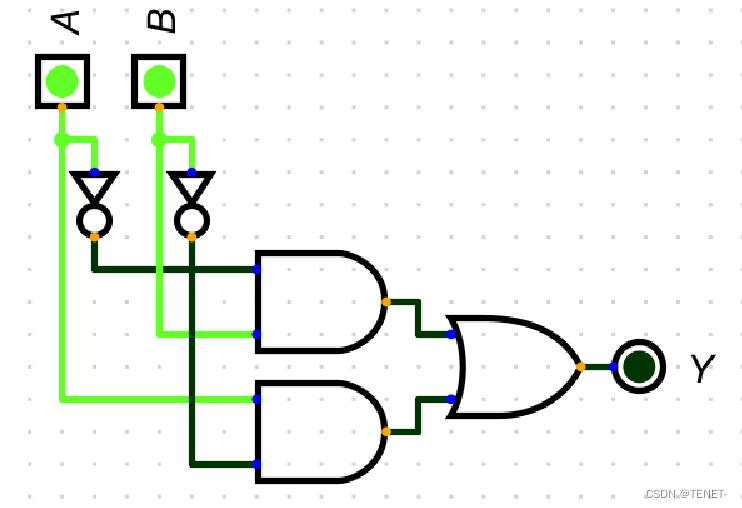

按照如下图搭建电路:

按F9分析可以看到真值表和表达式,这种相同出0,相异出1的电路,叫做异或门。

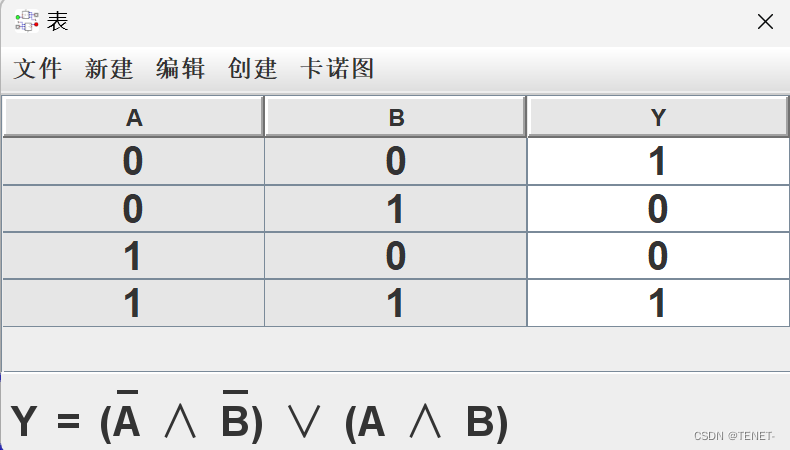

8. 异或非门(XNOR Gate)

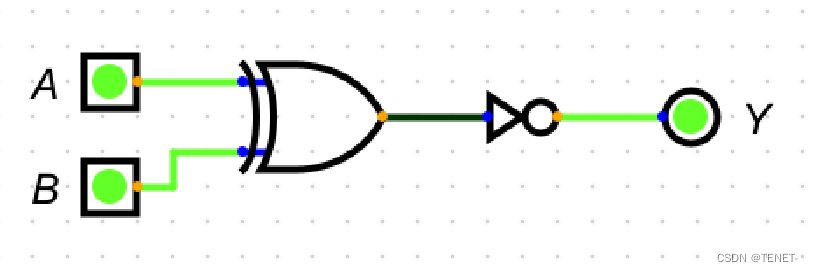

按照如下图搭建电路:

按F9分析可以看到真值表和表达式,这种相同出1,相异出0的电路,叫做异或非门。

9. 逻辑门总结