FSD, 参考资料来源FSD Chip - Tesla - WikiChip

另外可参考笔者之前分享文章:[自动驾驶技术]-6 Tesla自动驾驶方案之硬件(AI Day 2021),[自动驾驶技术]-8 Tesla自动驾驶方案之硬件(AI Day 2022)

1 整体介绍

特斯拉FSD计算机架构:

特斯拉FSD计算机架构:

-

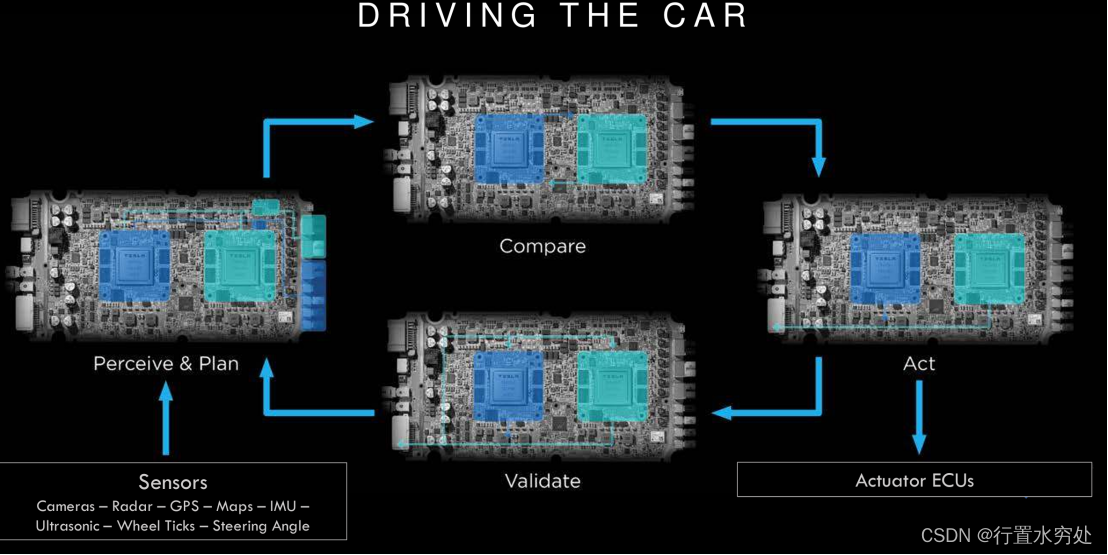

双冗余SoC,冗余电源:每个SoC拥有独立的电源和操作系统,确保高可靠性。

-

传感器输入:包括IMU、雷达、GPS、超声波传感器、轮速计、转向角和地图数据。

-

8个外部摄像头和12个超声波传感器:同时将数据输入两个FSD芯片。

-

独立处理:两个芯片独立生成车辆未来行动计划,并交由安全系统进行比较和验证。

2 FSD芯片规格

特斯拉D1芯片由1个GPU,2个NPU,3簇12个ARM Cortex-A72 CPU核,安全核,视频编码器等模块组成。

-

制程工艺:14nm FinFET CMOS,12层金属

-

面积:260 mm²

-

晶体管数量:60亿

-

包装:37.5 x 37.5 mm FCBGA

-

处理器:12个Cortex-A72核心,2.2GHz

-

神经网络性能:36.86*2 TOPS

-

功耗:每芯片低于40W

3 芯片核心组件

-

GPU:用于图像处理

-

CPU:12核ARM Cortex-A72

-

ISP(图像信号处理器)

-

H.265视频编码器

-

内存控制器、PHYs、片上互连和外围设备

3.1) 神经网络加速器(NNA)

-

两个独立实例双神经处理单元(NPU):每个NPU拥有32MB的SRAM,用于存储临时网络结果,减少数据移动。

-

设计频率:使用8位乘法和32位加法,2GHz+。

-

多路累加器阵列:每个NPU有96x96的乘加阵列,总共9,216个MACs和18,432个操作。

-

硬件SIMD、ReLU和Pooling单元(参见3.2和3.3)。

-

每个实例32MB SRAM,优化带宽;操作流程在每个周期中,数据从SRAM读入MAC阵列进行计算,结果数据写回SRAM。

-

激活函数支持包括ReLU、Sigmoid Linear Unit (SiLU)、TanH。

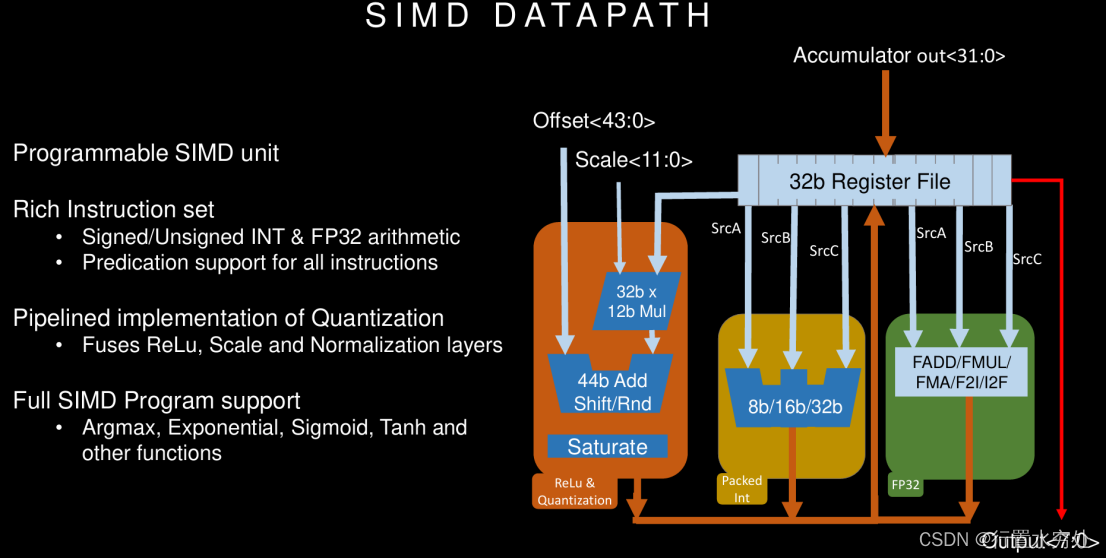

3.2) SIMD数据路径

-

可编程SIMD单元,支持丰富的指令集

-

浮点与整数运算

-

支持所有指令的谓词化

-

量化硬件的流水线实现,融合ReLu、缩放和归一化层

3.3) 池化硬件

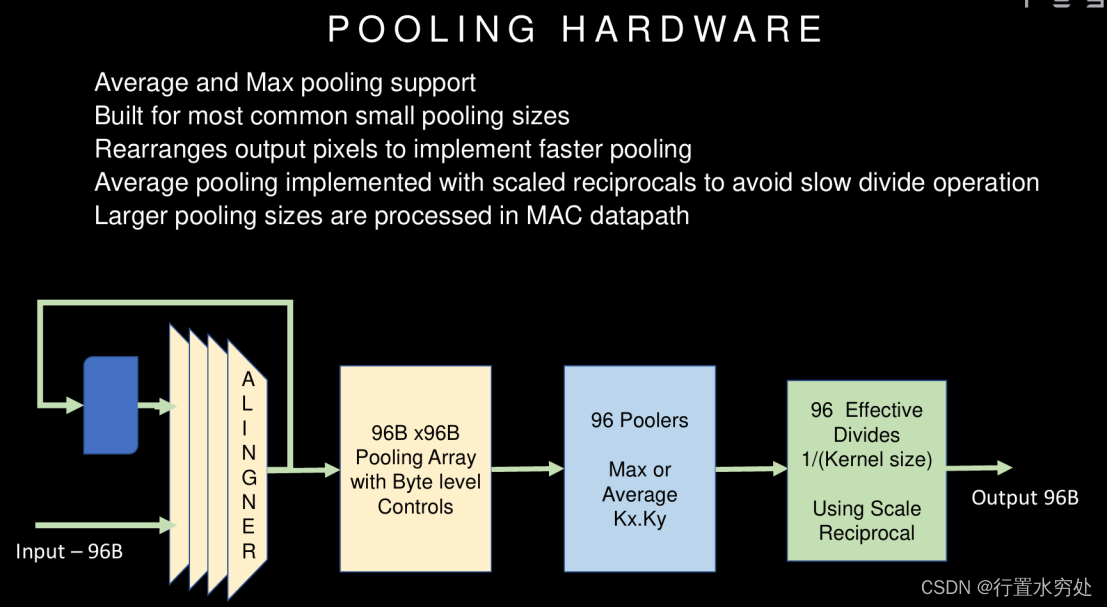

-

支持平均和最大池化

-

为最常见的小池化尺寸优化

-

重新排列输出像素以实现更快的池化

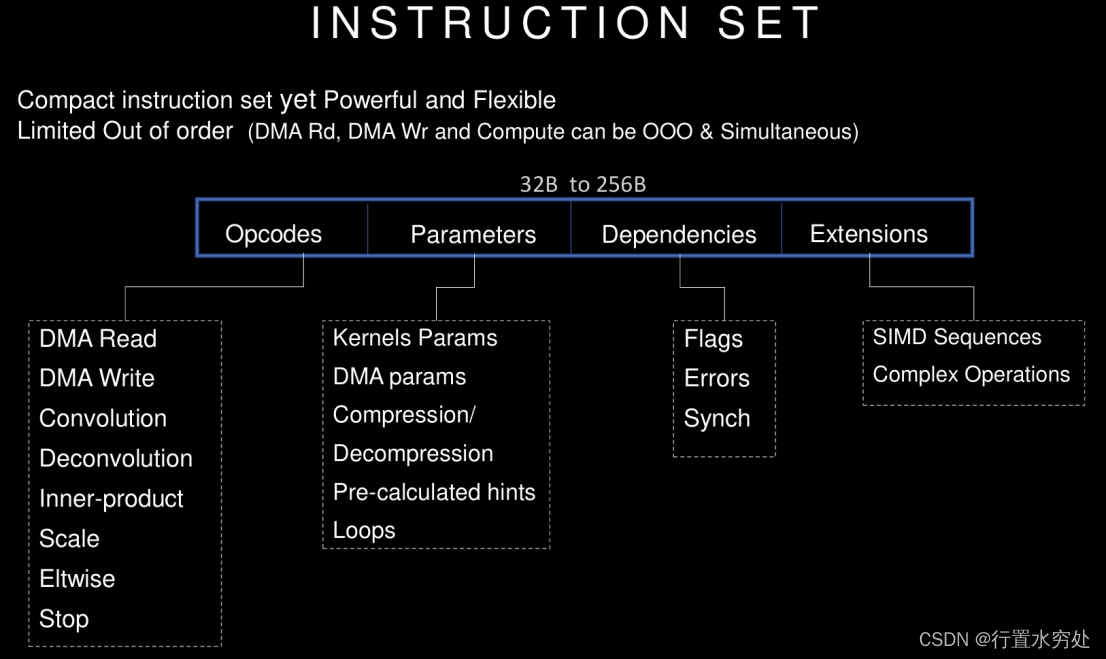

3.4)指令集和微架构:

-

简化硬件设计:一些硬件被简化,增加了软件复杂性,但降低了硅片成本。

-

软件优化:特斯拉的神经网络编译器负责层融合、内存访问平滑、通道填充和DMA操作。

-

运行模式:神经网络程序在芯片启动时加载并驻留内存,NPU在异步运行整个神经网络模型后中断CPU进行后处理。

4 特斯拉自研优势

- 优化性能:通过自研SoC,特斯拉可以针对特定的自动驾驶任务进行深度优化,提高处理效率和系统响应速度。

- 降低成本:自研芯片可以减少对第三方供应商的依赖,从而降低长远的成本。

- 增强控制:特斯拉可以完全掌控芯片的设计和生产过程,确保产品的质量和安全性,同时能够快速进行更新和改进。

- 知识产权:自研芯片可以保护特斯拉的技术和算法不被竞争对手轻易复制。

5 特斯拉NNA设计哲学

专注加速MAC操作:由于99.7%的操作是乘加(MAC),加速MAC能显著提升性能。

硬件专用量化和池化单元:提高整体速度和效率。

灵活的SIMD单元:支持丰富的指令集,包括整数和浮点运算。

灵活的状态机控制逻辑:减少控制功耗,支持复杂操作。

数据共享和最小化数据移动:减少SRAM和DRAM活动,进一步降低功耗。

单时钟域设计:支持DVFS(动态电压频率调整)以优化功耗和时钟分布。