1 仿真概述

Simulator仿真虽然不需要使用硬件资源,但是需要编写激励文件,也就是testbench代码。

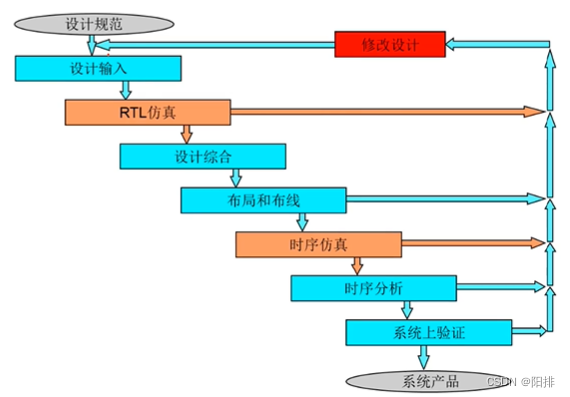

仿真是设计输入后的第一个步骤,也是实现后的最后一个步骤,可以分为功能仿真(RTL仿真)和时序仿真。

- 功能仿真:验证电路的功能是否符合设计要求,不考虑电路门延迟与线延迟。

- 时序仿真:布局布线后仿真,电路映射到特定的工艺环境以后,综合考虑FPGA芯片的路径延迟与门延迟,验证电路能否在一定时序条件下满足设计构想的过程,能较好地反映芯片实际工况。

2 Testbench文件

激励程序是输入设计顶层模块的信号波形,TB文件的结构如下:

typescript

`timescale 仿真单位/仿真精度

module test_bench();

// 通常testbench没有输入与输出端口

// 信号或变量定义声明

//使用initial初始化信号电平

//使用always语句产生时钟波形

//例化设计模块 模块名 例化名(...)

endmodule- `timescale 1ns/1ps较为常见。

- 在以上仿真时间情况下,# 100表示延迟100ns。

- 如果是`timescale 1ps/1ps,# 100表示延迟100ps,延迟只看timescale的仿真单位。

3 试验步骤

本节使用之前的LED交替闪烁试验工程作为模板,添加tb文件进行仿真试验。

3.1 编写testbench文件

1、在Sources窗口右键Simulation Sources,Add Sources。

2、新建源文件:Create Source File,文件取名为tb_test_project.v。

3、编写测试文件:

查看test_project模块的输入输出,tb中如果对端口使用always或initial进行赋值,则使用reg类型;如果对端口使用assign进行赋值,则使用wire进行赋值。

// 000_test_project.v

module test_project(

input sys_clk,

input sys_rst_n,

output [1:0] led

);

// ......模块中初始化赋值使用initial,begin和end一头一尾相对应。#200为延时200ns,模拟复位按钮按下一段时间后弹起。

如果sys_clk时钟周期为20ns,则时钟频率为50MHz,在一个时钟周期内高电平和低电平分别占据10ns。因此采用always语句来模拟时钟。

typescript

// tb_test_project.v

`timescale 1ns / 1ps

module tb_test_project();

// 信号或变量定义声明

reg sys_clk;

reg sys_rst_n;

wire [1:0] led;

//使用initial初始化信号电平

initial begin

sys_clk = 1'b0;

sys_rst_n = 1'b0;

#200

sys_rst_n = 1'b1;

end

//使用always语句产生时钟波形

always #10 sys_clk = ~sys_clk;

//例化设计模块 模块名 例化名(...)

test_project u_test_project(

.sys_clk(sys_clk),

.sys_rst_n(sys_rst_n),

.led(led)

);

endmodule3.2 开始仿真

点击Vivado左侧窗口Simulation的Run Simulation,选择Run Behavioral Simulation。

五个选项分别为:

- Run Behavioral Simulation:运行行为仿真(功能是否完整)。

- Run Post-Synthesis Functional Simulation:运行综合后的功能仿真

- Run Post-Synthesis Timing Simulation:运行综合后的时序仿真

- Run Post-Implementation Functional Simulation:运行实现后的功能仿真

- Run Post-Implementation Timing Simulation:运行实现后的时序仿真

运行一段时间后,可以观察到波形如下所示:

如果需要查看cnt计数器的值,点击u_test_project,然后将cnt拖动到右侧波形图中,然后重新运行仿真就可以看到cnt的变化情况。

运行较长时间后,可以在波形图中观察到当cnt的值为25000000后,led的值发生改变。

Ctrl+S就可以保存波形信息为.wcfg格式。