Q:如何将计算出的结果(最长的连续1的个数)显示在DE2-115开发板的HEX上?

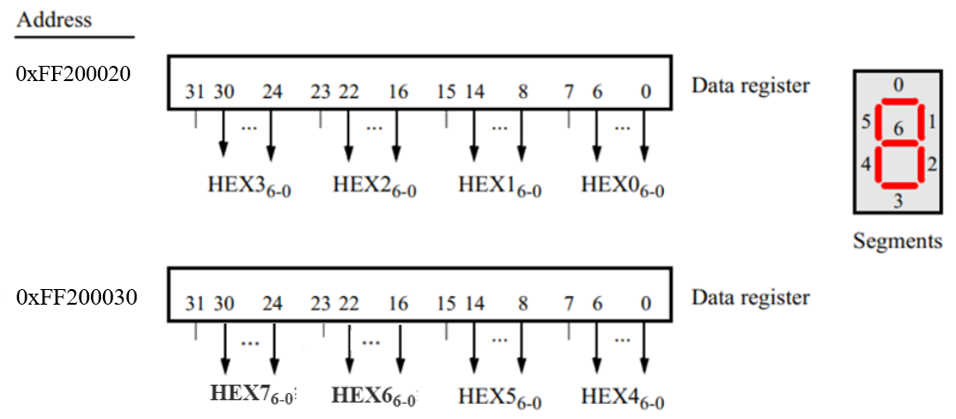

**A:**基本原理:DE2-115_Computer_System中的HEX并行端口作为内存映射设备连接到DE2-115开发板的七段数码管,每个端口都对应内存映射地址。将寄存器r10中的二进制数计算结果转换为十进制数,通过点亮七段数码管相应的段来显示0-9这10个数字。如要在HEX0上显示数字0,就点亮除数码管段6之外的所有其他数码管段,即将 (00111111)B存储到与HEX3~0 并行端口对应的地址中。

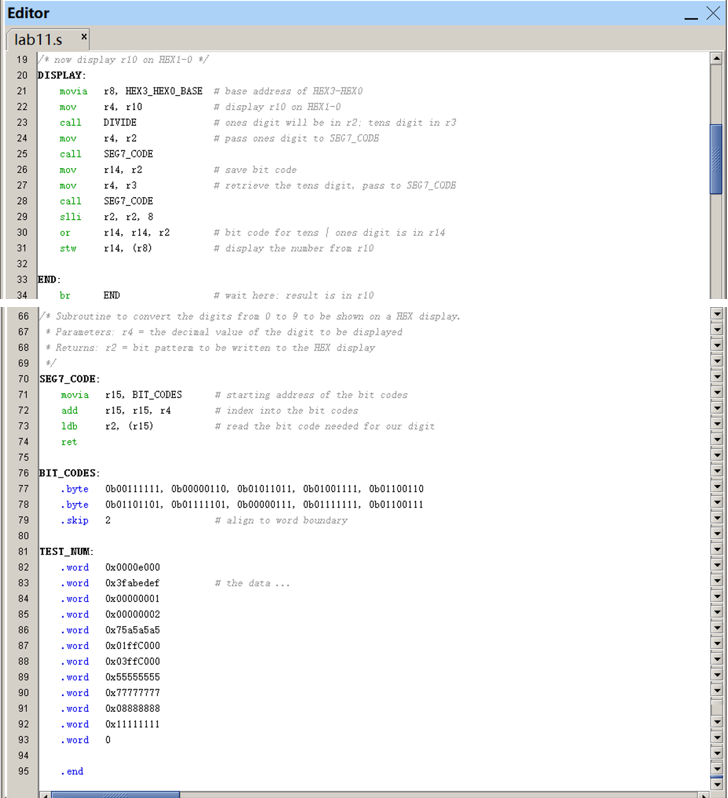

本实验的程序设计将最长的连续1的个数以十进制数显示在HEX1-HEX0上,部分汇编程序代码如下:

运行程序后可以观察到开发板上的HEX1显示1,HEX0显示2,即最长的连续1的个数为12。