Vc initiation process:

(1)FC_INIT1

(2)FC_INIT2

While in FC_INIT1, block tx tlp using VCx

Non-flit mode

(1)FC1-P (2)FC1-NP (3)FC1-CPL -> all dedicated

Flit mode

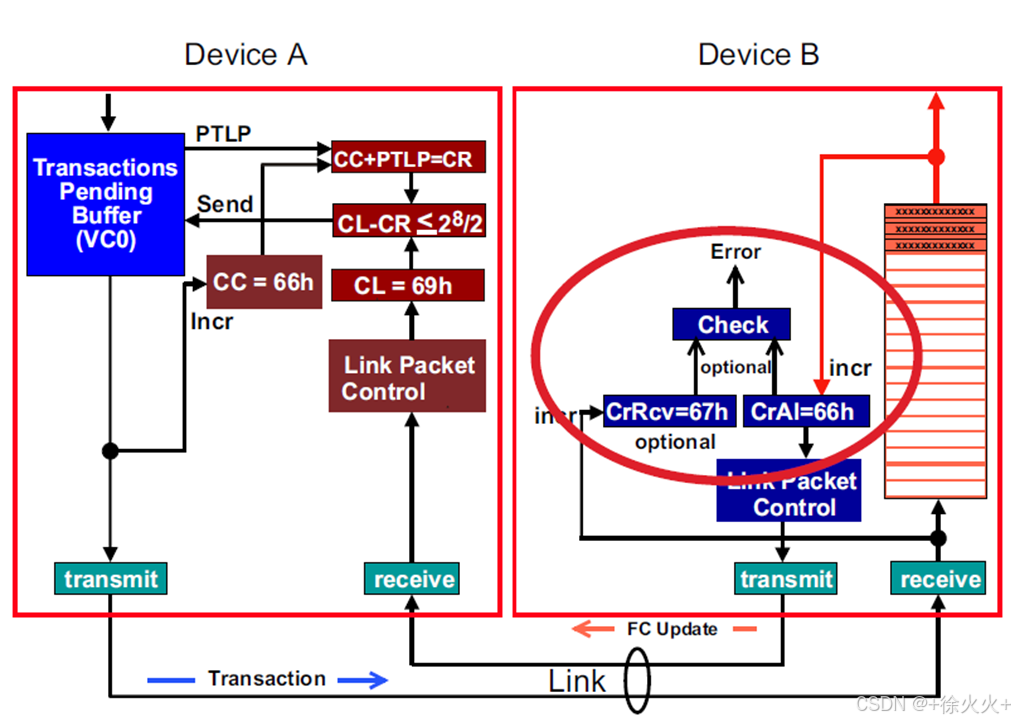

CREDITS_CONSUMED

Count of the total number of FC units consumed by TLP Transmissions made since Flow Control initialization

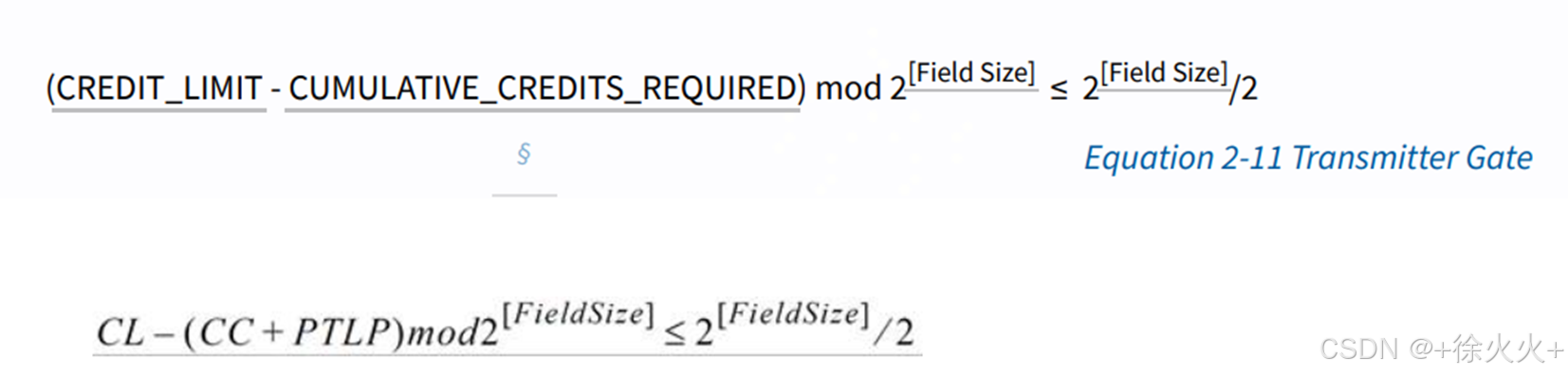

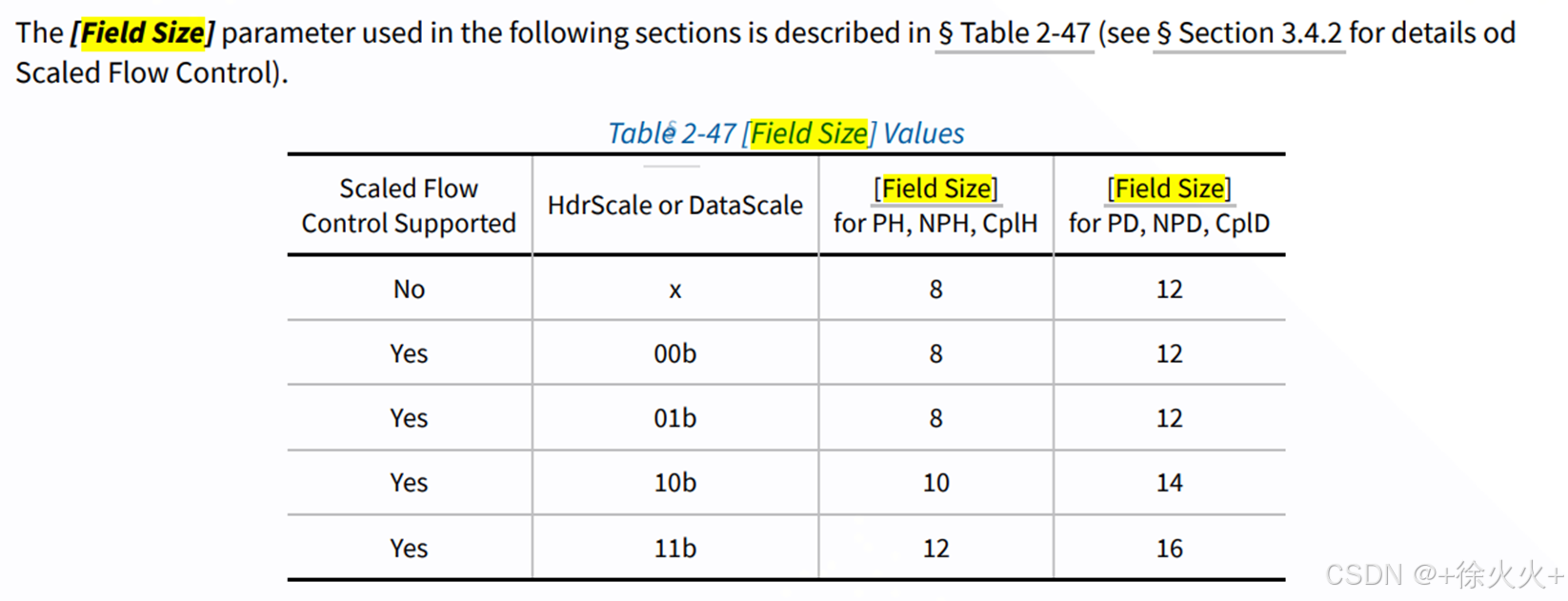

CREDIT_LIMIT****is fromFC updatedllp

reflects all credit flow control updates, for each FC update received, if CREDIT_LIMIT is not equal to the update value, set CREDIT_LIMIT to the update value

Update_FC **内的Credit值是Rx FC Buffer初始Credit及所有从该Buffer取出的TLP数据占用Credit的总和,是累加的。**想要获知 Rx FC Buffer 余量,对于 Rx 端需要综合 CA 及 CR 两个计数器,对于 Tx 端则是 CL 及 CC 两个计数器

对于TX来说是CL-CC;

对于RX来说是CA-CR

CREDITS_ALLOCATED, Count of the total number of credits granted to the Transmitter since initialization

Rx一共允许tx发送多少内容,rx处理完毕相应的事务之后这个cnt增加,递增

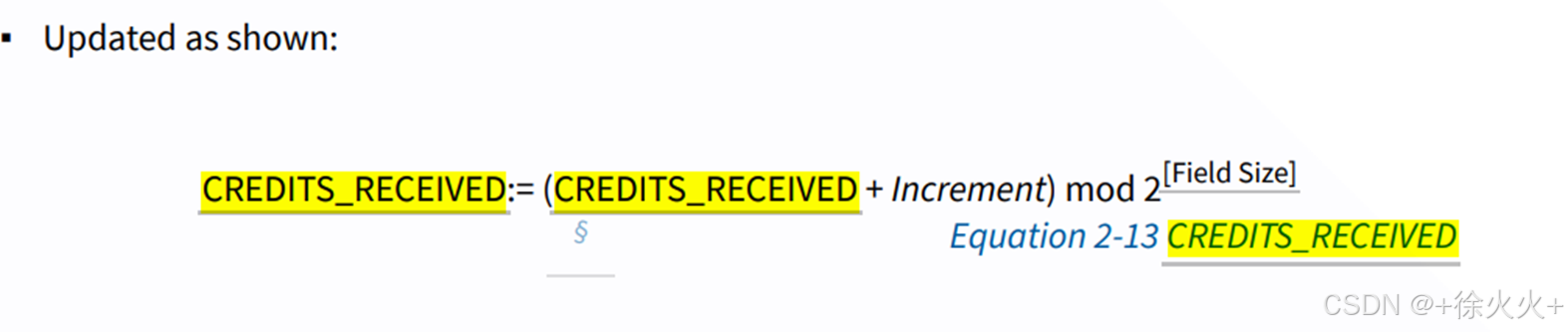

CREDITS_RECEIVED, Count of the total number of FC units consumed by valid TLPs Received since Flow Control initialization

已经接收的数量

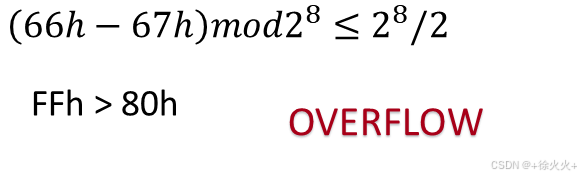

TLP进入Rx FC Buffer 之前,Receiver可判断 Rx FC Buffer是否有能力接收。若以下条件成立,表明 Rx FC Buffer 会溢出

TLP进入Rx FC Buffer 之前,Receiver可判断 Rx FC Buffer是否有能力接收。若以下条件成立,表明 Rx FC Buffer 会溢出