文章目录

基础知识

- 数值表示:位宽进制值,如 2d0 表示 2 位宽十进制 0,这里的位宽是 bit, 1 bit = 8 byte

- input 和 output 默认是 wire 类型

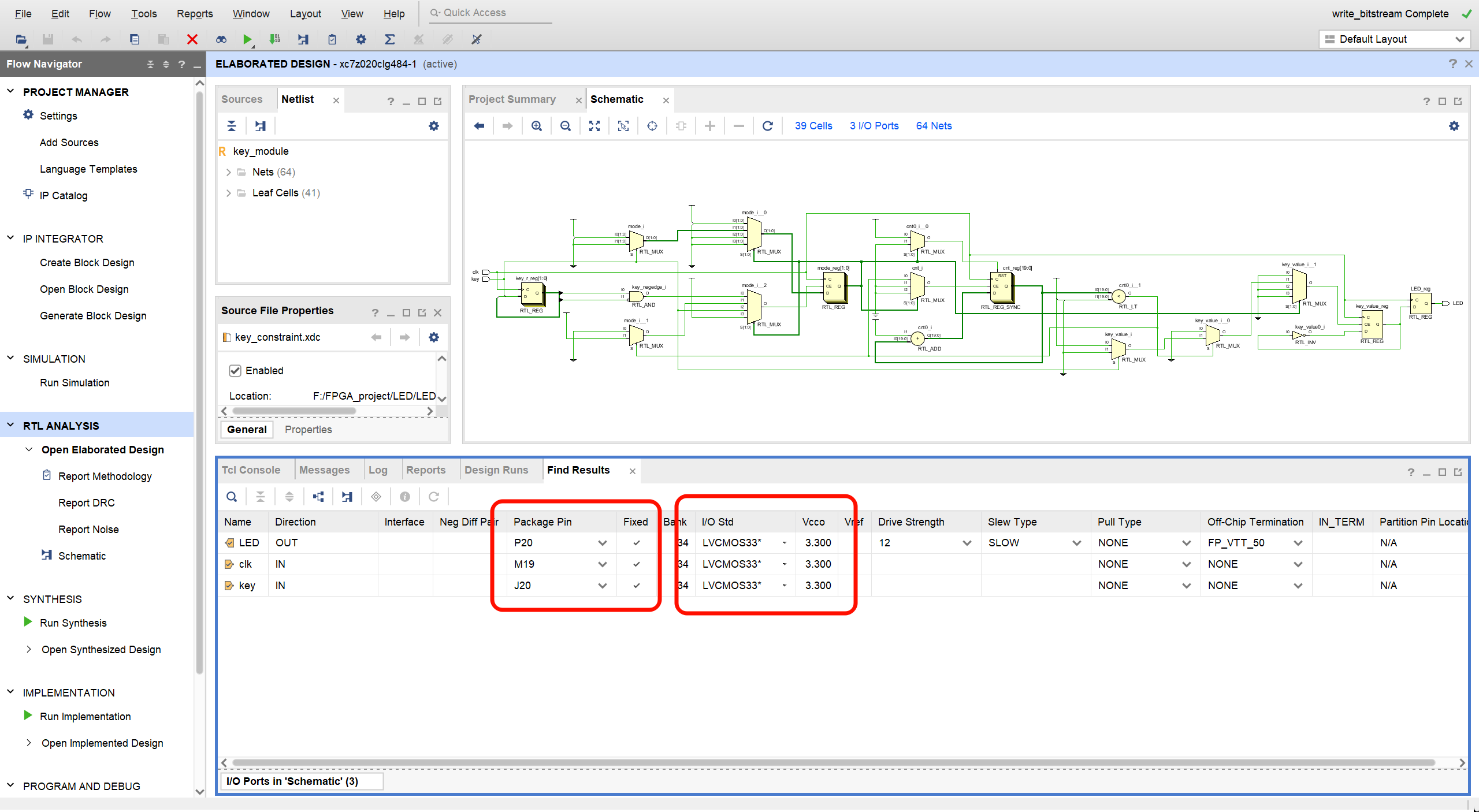

- 关于 管脚约束中 I/O std 的选择:

管脚约束

代码

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: LWX

//

// Create Date: 2025/08/03 17:38:28

// Design Name:

// Module Name: key

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module key_module(

input clk,

output reg LED,

input key

);

reg [1:0] mode = 2'd0; // 2bit 十进制 0

reg [19:0] cnt = 20'd0;

reg [1:0] key_r = 2'b11; // 接收按键状态的 2 位 reg

reg key_value = 0; // 按键值

always@(posedge clk) begin // 按键信号同步时钟

key_r[1] <= key_r[0];

key_r[0] <= key;

end

wire key_negedge = key_r[1] & ~key_r[0]; // 按下为 1,弹起为 0,标志按键状态的检测,只有前一刻为 1,这一刻为 0 才是 按下

always@(posedge clk) begin

case (mode)

2'd0 : begin // 初始状态

cnt <= 20'd0;

if (key_negedge) mode <= 2'd1;

end

2'd1: begin

if (cnt < 20'd1000000) begin // 计数中

cnt <= cnt + 1'b1;

end

else begin

if (key == 0) begin // 如果按键按下且 20s 之内还是按下

key_value <= ~key_value;

mode <= 2'd2;

end

else

mode <= 2'd0; // 如果按键松开,回到初始状态

end

end

2'd2: begin // 等待按键松开

if (key == 1)

mode <= 2'd0;

end

default: mode <= 2'd0;

endcase

end

always@(posedge clk) begin

LED <= key_value;

end

endmodule