Arm 架构学习

01 CPU Architecture

- 按指令集分

arm RISC (reduced instruction set computer)/ load store structure

x86 CISC(complex instruction set computer)/ direct visit memory

【架构知多少】谈谈X86架构与ARM架构区别_x86与arm架构区别-CSDN博客

- 按存储分

冯·诺依曼架构的特点是将程序指令和数据存储在同一块内存中,通过一个共享的总线进行数据传输。这种结构的优点是简单易懂,容易实现,广泛应用于现代计算机系统中。

哈弗架构则是将指令和数据分开存储,通过不同的总线进行数据传输,这种结构可以提高计算机的并行处理能力。

CPU是如何工作的?什么是冯·诺依曼架构和哈弗架构?-CSDN博客

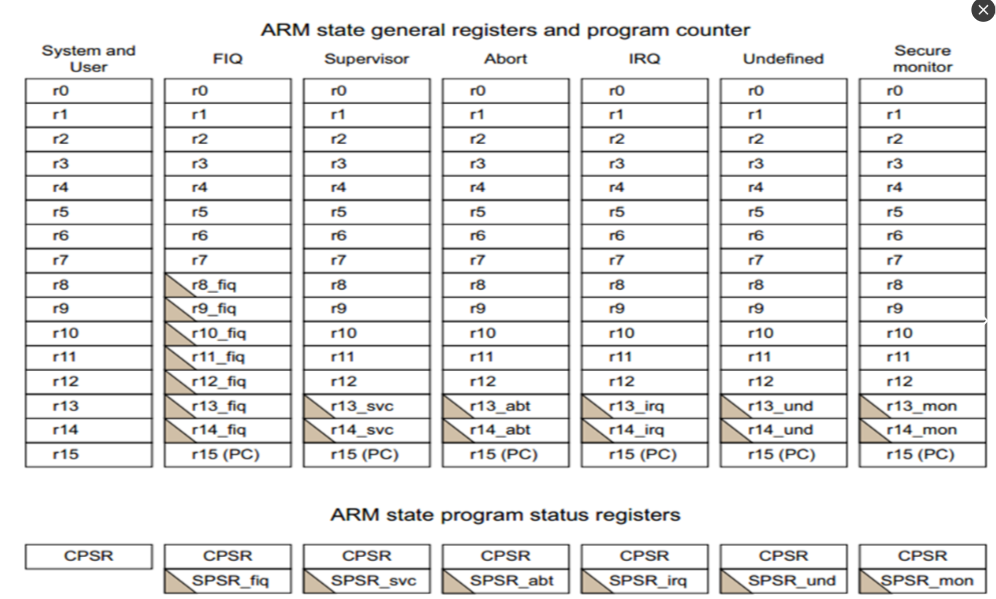

02 register

40个寄存器 = 33个通用寄存器 + 7个状态寄存器

专用寄存器

R16 CPSR 当前程序状态寄存器

R15 PC(Program Counter) 下一条代码指令

R14 LR(Link Register) 程序跳转

R13 SP(Stack Pointer) 栈指针

CPSR寄存器分为四个域,[31:24]为条件域用F表示、[23:16]为状态域用S表示、[15:8]为预留域用X表示、[8:0]为控制域用C表示

Bit[4:0]

[10000]User [10001]FIQ [10010]IRQ [10011]SVC

[10111]Abort [11011]Undef [11111]System [10110]MonitorBit[5]

0\]ARM状态 \[1\]Thumb状态 Bit\[6

0\]开启FIQ \[1\]禁止FIQ Bit\[7

0\]开启IRQ \[1\]禁止IRQ Bit\[28

> 当运算器中进行加法运算且产生符号位进位时该位自动置1,否则为0

> 当运算器中进行减法运算且产生符号位借位时该位自动置0,否则为1Bit[29]

> 当运算器中进行加法运算且产生进位时该位自动置1,否则为0

> 当运算器中进行减法运算且产生借位时该位自动置0,否则为1Bit[30]

当运算器中产生了0的结果该位自动置1,否则为0

Bit[31]

当运算器中产生了负数的结果该位自动置1,否则为0

03 Instruction set

ARM采用RISC架构,CPU本身不能直接读取内存,而需要先将内存中内容加载入CPU中通用寄存器才能被CPU处理。使用LDR/STR指令组合来实现 ARM CPU和内存数据的交换:

LDR(load register)指令将内存内容加载入通用寄存器。

STR(store register)指令将寄存器内容存入内存空间中。

寻址方式:

- 立即数寻址

- 寄存器寻址

- 堆栈寻址

万字长文带你由浅入深夯实ARM汇编基础------汇编指令及寻址方式最全梳理(附示例)!-CSDN博客

04 work mode

- user

- system

- IRQ

- FIQ

- SVC

- Abort

- Undef

- Monitor

异常模式:在ARM的基本工作模式中有5个属于异常模式,即ARM遇到异常后会切换成对应的异常模式。

05 memory mode

ARM支持大端、小端两种内存模式。

大端:数据高字节存在低地址,低字节存在高地址。

小端:数据高字节存在高地址,低字节存在低地址。

汇编判断大小端:

asm

r0 = 0x11223344 ;复制0x11223344给寄存器r0

r1 = 0x100 ;赋值0x100给寄存器r1

STR r0,[r1] ;把r1的值作为地址,加载r0的数值到0x100的地址中

LDRB r2,[r1] ;从地址0x100中取出1Byte数据判断r2的值可知道大小端:

小端模式下:r2=0x44

大端模式下:r2=0x11

ARM学习之ARM基础知识(一)_学arm需要什么基础-CSDN博客