本案本来是描述一下I2C总线的,在此之前推荐一下B站一个UP关于时序图的讲解

I2C入门第一节-I2C的基本工作原理_哔哩哔哩_bilibili

不过在描述I2C前先简单的探讨下51单片机IO口下拉电阻的基本情况,事实上这个问题困扰笔者很长时间了,这次也是一些基础的探索。网上搜索的IO口原理图都是逻辑图,所以有些情况就很尴尬,不知道怎么理解。这次神奇的B站没有拯救我,虽然有些科普视频,但还是无法比较准确的解决问题。

在前面的博文关于LCD1602液晶的描述时候,笔者的开发板是把液晶E端与单片机P1.5端口相连并且接了一个下拉电阻,它的作用是把P1.5端口电压(即液晶E端电压)拉成低电平。那么它是如何实现的呢?51单片机P1端口是准双向IO口并且是弱上拉,即它能提供的电流很小最大是200ua,5V电压下换算一下5/0.0002这个电阻是25K,开发板老师说的这个内置上拉电阻是20K左右。

如图准双向IO口的示意图网上能够找到比较常见的示意图: 在IO端口P1.x处接一个下拉电阻20K。

在IO端口P1.x处接一个下拉电阻20K。

笔者以前给出的准双向IO口示意图:

经典解释:VCC下面那个内置上拉电阻R就可以理解为是25K,

T2导通的时候IO口P1.x就输出低电平。

T2截止的时候IO口p1.x就输出高电平。

51单片机在上电结束后默认输出是高电平即T2是截止的,那么在P1.x端口接下拉电阻20K,为什么能把IO口拉成低电平呢?而不是和内置上拉电阻一起分5V的电压?

即该处的电压是5*20K/(25K+20K) = 2.22V. 但最后的结果是0V?为什么?这群大爷在出示意图的时候就不考虑这种情况容易引起误解,我找了不少关于这方面的讯息,都没有关于这方面的解释,这个问题很简单吗?还是只有我一个笨蛋。。。。(后文笔者写着写着就解决了。。。)

然后看一下51规格书提供的关于IO口这方面的说明

尝试解读一下:

1:上图栅极画圆圈表示PMOS 管,不画圆圈表示NMOS管。PMOS管低电平导通,NMOS管高电平导通,反之截止。可见上图3个Pmos管(T1,T2,T3)一个Nmos管(T4)

2.一导线穿过去表示这两个场效应管的G极是连接在一起的方便画法。

PMOS管就是载流子是正电荷或者叫空穴的mos管,这个P英文postive:正向、正极的意思。同样的NMOS这个N是negative负向的、负极的意思。这就比较好记忆了,笔者以前根本就记不住这个东西。别听某些人瞎说只要知道中文就好了。。。。。。笔者后面知道英文后就没怎么忘了,在命名mos管的时候都是以它的沟道的命名的。Pmos管就是P沟道,即它的多数载流子是正电荷或者叫空穴。

而mos管的中间段的沟道载流子都是栅极电压感应出来的,因此要感应出正电荷,那么栅极和源极之间的电压差即GS<0,对应着上文PMOS管低电平导通,这不是说G极一定是低电平,而是说G极的电压小于S极。

所以你会在一些电路图上看到PMos管的S极(源极)是高电平,漏极是低电平的,而且两种mos管逻辑图S级与D极的位置在电路图中是刚好相反,不像教科书里哪样S极都在示意图下面,D极在上面。其实这和三级管差不多,对于PNP的三极管它发射极是高电平,集电极是低电平。这里的高低电平都是相对的,不一定是基于地的电平更多的是比较电平。那么PMOS管低电平导通,NMOS管高电平导通就好理解是什么意思了。

笔者标识了一下mos管的管脚

可以看到T1的是PMOS,下面的T4是NMOS,它们的漏极是相连的,PMOS的源极是接VDD的,NMOS的源极是接地的。

写入程序使IO口 P2.0 = 0;那么用示波器测试P2.0端口它就会是低电平。走下线路图看下它是怎么工作的,51单片机P2.0是准双向IO口。

口锁存数据被写入0,经过非门,输出1。继续走有两个分支,往上走,它又会经过一个非门,先不管。看往下走的分支1,直通NMOS管T4以及PMOS管T2的G极,也就是说现在G极是高电平了,则T4导通了,T2是截止的。

然后我们继续走另一个分支2,经过两个非门则这时候的电平信号又转回低电平了,经过2个CPU延时,到达或门,或门的另一个引脚已然由分支1保持为高电平 ,显然分支1电平信息传递比分支2快,则现在或门的输出就是高电平了,T1是PMOS,这时候G端与S端的电平是相等的,那么PMOS管T1截止了。

那么IO端口P2.0就直接通过T4mos管接地了,现在端口电压输出低电平了。此时电流可以从外部装置(高电平)流入单片机,这个电流可以叫"灌"电流,也叫IO口推挽模式中的"挽",因为路线之间没有限流电阻,所以叫强"挽",所以外部装置要接限流电阻控制电流,否则会烧坏单片机。

我们观察一下T3mos管,发现它的G极是和IO端口引脚相连的 ,之间串有一个干扰滤波而且是个非门输出,IO端口低电平电压通过非门输出高电平,高电平加在T3的G极,T3就无法导通。再看一下准双向IO口示意图:

T3导通后这个内置上拉电阻才是20K左右,如果T3不导通,可以认为这个上拉电阻就是20K+T3截止的等效电阻,可以认为高阻抗,说人话就是阻值很大。

如此只有T4mos管工作,最终表现为IO口输出低电平。

现在用程序往IO口p2.0写入1,则现在口锁存数据为1,分支1 经过非门。T4和T2的G极都是低电平,则T4截止T2导通。T2是极弱上拉。只能提供30UA 的电流,

从数据手册上来看,它是在引脚悬空的时候工作的,用来维持高电平的。用欧姆定理可以看出来,这个等效的上拉电阻是5/0.00003=166 667欧姆近似一下就是166K,在如此的大的上拉电阻情况下还能使端口输出高电平,则说明输出IO端口到地的电阻比它大的多的多,则认为IO端口到地的阻抗是高阻抗 。且它是在悬空的时候才工作,说明IO口悬空的时候极弱上拉体供的电平信号无法反馈给T3的G极使它的管子打开。极弱上拉和弱上拉之间无法套娃工作(看后文解释)

再看下手册对于弱上拉的描述:

看的不是很明白?不过我们知道准双向IO口在作为输入的时候,它是要先向IO口写入1,这个时候单片机IO口的电压就可以随着外部装置电平的信号变化。

如果外部装置是高电平,这个时候单片机IO口就是高电平,外部电压是低电平,IO电平就是低电平。程序中会使用语句比如 sbit k = P2.0; k = 1(先向IO口写入1); vaule = k(在把IO电压赋值给变量) ;这个时候的vaule的值就不是我们写入单片机的高电平,而是外部装置的电平信息。也就是说当外部装置是高电平的时候vaule = 1;,是弱上拉在工作,一旦外部装置是低电平那么,弱上拉关闭,极弱上拉工作。此时该IO口输出的电平是低电平。即现在vaule = 0;

这最后一句话就不太好理解了。对于外部装置来说,本身是低电平,高电平是IO口,外装置需要的电流不从IO出,难道要外接上拉电阻到VCC给外部装置提供电流,让它能够把端口电压拉低?先不管这句到底什么意思继续下文分析。

支路2和之前一样,经过两个非门,保持的是高电平,然后到了或门,那么无论或门1脚的电平信息了,或门依然输出高电平,PMOS管T1依然无法打开。怎么不管是高还是低电平写入T1都打不开?这什么情况?从逻辑图看要想T1导通,或门输出必须都要是低电平。再看下逻辑图

从逻辑图上来看这是不可能的实现的,但是我们发现或门的那条支路2上有延时且多经过一个或门消耗更多的时间。

因此当先向IO端口写入0,这时或门的1脚是低电平 ,再向IO口写入1,那么如上图在时域上当或门2脚是低电平的时候,或门1脚还是保持之前的电平信息即低电平,这个时候或门**输出低电平,这时T1就导通了(**这个时间很短2个机器周期),同时T4是截止的。这个时候IO端口电压输出高电平,而且因为T1的上拉电阻很小(有没有阻值不知道反正也看不出,看它写了个强,那限流电阻肯定很小),因此是端口能够输出较大的电流给外部装置,这个电流就是"拉"电流,对单片机来说是把电流推出去一样,也叫"推"电流,它和上面的那个工作方式一起叫做推挽工作模式,因为限流电阻小说以叫强推挽输出。

但是持续时间很短2个机器周期,一旦分支2的或门一脚电平被更新为高电平(由于口线寄存器写入1),或门输出高电平,这个强推挽就关闭了,这时根据IO口外部装置的不同,工作在弱上拉或者极弱上拉。看下手册上是怎么说的,

它用了加快,而不是保持,说明这种方式确实是不能长时间保持的,强推结束收后就工作在弱上拉,或者极弱上拉。而且是发生在0到1跳变的时候才有效,强挽是可以长时间保持的。

我们知道51单片机P0端口是开漏输出,它和准双向IO(P1、P2、P3)的区别是没有内置上拉电阻,这个内置上拉电阻就是弱上拉,它依然是有强推挽和极弱上拉的。51单片机复位默认是工作在高电平的。最后又回到之前的问题单片机IO口接1个下拉电阻,IO口端口会被拉成低电平。

P0是开漏输出,但是不外接上拉电阻它无法输出高电平,则说明极弱上拉接外部装置时无法维持端口高电平,而强推挽只是一瞬间拉高电平。因此若想IO口长时间输出高电平,那么准双向IO口必然处于弱上拉的状态。

笔者对下拉电阻做过一个测试以下是测试数据:

测试对象开发版51单片机STC89C52 P2.0端口,测试方式是在P2.0端口接一个下拉电阻如图,使其工作在默认状态或者通过程序向P2.0端口写入1,测试端口电压,以下是测试结果:

220K 4.56V

150K 4.56V

100K 4.32V

85K 4.24V

80K 0.96V

47K 0.6V

20K 0.32V

10K 0V

从数据结果来看,当IO端口接下拉电阻的时候,IO口工作在极弱上拉而不是弱上拉模式,**它不满足弱上拉的工作条件(外部提供高电平)因此不能简单的用欧姆定律分压。**从结论上来看,极弱上拉的等效电阻很大而且也不是一成不变的,它是随着电流变化(毕竟不是电阻,而是晶体管的集合)。根据具欧姆定律,10K,20K与极弱上拉的等效电阻比起来很小,因此下拉电阻分配到的电压也就很低,IO端口就输出低电平。可以看出随着电阻的变大IO口电压还是有所变大,说明确实大一点的电阻分到了更大一点的电压虽然都是低电平范围内。

而到了85K的时候,端口突然输出高电平,从现象来看应该是弱上拉打开,(这时极弱上拉是否关闭不清楚它开着也不影响分压结果。它的阻抗相比弱上拉的阻抗来说大很多,更可能的猜想是内置上拉电阻20K,很可能是极弱上拉的阻抗和弱上拉的阻抗并联的等效阻抗),弱上拉的上拉电阻相比于现在的下拉电阻偏小,因此根据欧姆定律分压现在IO端口呈现高电平。

那为什么会发生这种情况呢?我们观察一下T3管子,发现它的G极是和IO口相连的,而且接了一个非门。那大胆的猜测就是IO的电压达到一个临界值的时候可能是1V(按照数据的合理推测 ),这个非门就能输出低电平了(上图A点),因此T3mos管打开了。IO口工作在弱上拉状态,通过欧姆定律的分压,IO电压瞬间就变成高电平,而这个IO端口高电平又促使这个非门输出低电平,而这个低电平又让T3管子导通。这是套娃了,如此IO端口现在输出保持在高电平了。表现为85K以上的下拉电阻,不再使IO口处于低电平,而是高电平。

再看一个电路图:

分析一下:

1:工作在默认状态或者向P2.0端口写入1

2:存在外接上拉电阻10K,因此该高电平信号(VCC)通过非门输出低电平(示意图A点),使T3mos管导通,那么现在的上拉电阻就是内置上拉电阻20K和外接上拉电阻10K并联的阻值:即10K*20K/(10K

+20K) = 6.67K,这个电阻和下拉电阻20K进行分压,则此时的IO口电压是:5*20/(20+6.7)=3.74V

我们用示波器看下结果:

结果是3.76V还是很准确的。

3:如果向P2.0端口写入0,IO口端口电压最终是0V,不过这里有个下降时间看逻辑分析仪的输出结果,

可以看到这个高电平持续了187ms,这个时间还是比较长的。

至此对于51单片机IO口以及上下拉电阻应该有了更深的认识了。对于前面博文LCD1602E端接下拉电阻为什么还能使能液晶应该有了新的认识。强推挽时间能够维持2个机器周期,对11.0592M的单片机来说就是2us,而LCD1602E端的使能要求是ns级别如图

因此即使接了下拉电阻,依然能够正常触发液晶1602.

总结一下:

1:51单片机上电恢复默认电平是高电平

2: 51单片机IO口悬空的时候是靠极弱上拉维持高电平的,它无法激活弱上拉

3:弱上拉需要外部高电平来激活,因为它是靠IO端口反馈信号来打开mos管的。

4:不要想着用默认IO端口高电平作为输出电源,它自身的存在都是靠着外部电平信号,从另一种角度来看信号逻辑,若想保持高电平,外部装置也得保持高电平,因为它们互相依靠,互相依存,互相激活,缺一不可。若想输出电流,就接外置上拉电阻。

5:接下拉电阻的时候,IO口是极弱上拉在工作。下拉电阻不能太大,否则可能套娃最后激活弱上拉。

6:结合上述结论的合理推论是,IO口作为输入端检测到高电平,这不一定证明外部装置处在高电平状态,也可能是高阻抗状态。

7:强推模式只工作两个机器周期,而且是发生在0到1的跳变时刻。强挽模式可以一直持续,一起构成强推挽工作方式。

8:片内IO端口到地的等效电阻变现为高阻抗,因此与下拉电阻并联的阻值就近似为下拉电阻本身。

9:该结论只支持准双向IO口。STM32笔者没学过IO口好像不太一样。

分享一下B站UP的关于IO的解释,笔者这不是要拷打,只是分享一下、

看出区别了吗?上面那个PMOS管Q1的S极和D极接反了,他的Q1是D极接VCC,S极与Q2的D极相连。正确的接法应该是按照我标的那样接。当然这是GPIO是不是有其他玄机笔者不清楚,无论怎么接它Q1的续流二极管肯定是反的,否则它无法放电。

那个续流二极管应该都是朝上的,这个其实不用特别去记忆,根据楞次定律,mos管的寄生电感会在mos管本身位置产生一个感应电动势,让电流保持,而续流二极管的作用就是和它构成回路放电,所以直接按照电流方向画就可以了,然后就知道续流二极管的方向了,如上图。

看mos管的示意图还是有些诀窍的:

1:G,D,S三个管脚。只有D极是孤零零的,因为GS之间构成极板电压因此在示意图上它们是有所表现的如:

2:中间的虚线代表的是绝缘栅型

3:分辩N沟还是P沟看这个小箭头,我们知道N沟P沟说的是它的载流子。

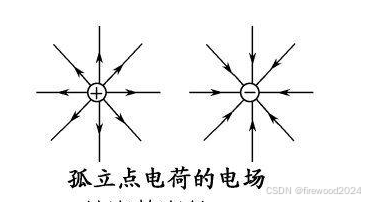

可以靠电场线去记忆, ,正电荷箭头是朝外发散,负电荷电场线箭头都是指着负电荷本身的。示意图的虚线就当成电荷本身了。

,正电荷箭头是朝外发散,负电荷电场线箭头都是指着负电荷本身的。示意图的虚线就当成电荷本身了。

Pmos是p沟,载流子正电荷(空穴)电场方向箭头朝外

Nmos是N沟,载流子电子 电场方向箭头朝内

小结:其实本来这篇是准备描述I2C的,写IO口了是为了MARK一下,以后如果找到结论,再来填。一开始笔者还不知道怎么解释IO口的现象,写着写着竟然找到答案了,也是意外之喜。觉得有问题的同学,可以提出来交流下。