时钟切换

描述

题目描述:

存在两个同步的倍频时钟clk0 clk1,已知clk0是clk1的二倍频,现在要设计一个切换电路,sel选择时候进行切换,要求没有毛刺。

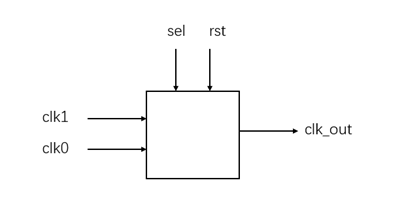

信号示意图:

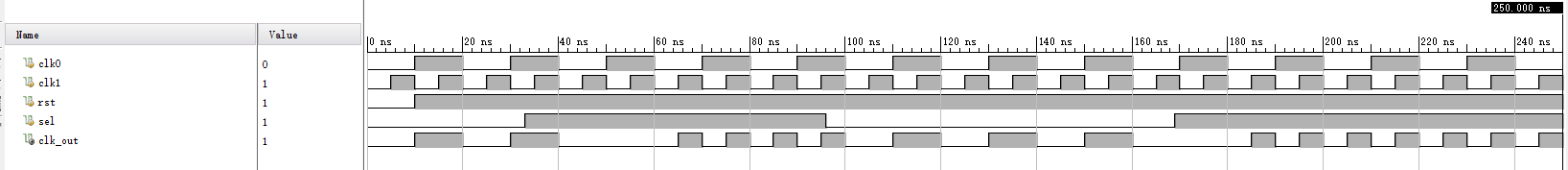

波形示意图:

输入描述:

clk0,clk1 为时钟

rst 为低电平复位

sel是时钟选择器

输出描述:

clk_out 信号输出

解题思路

时钟切换相关知识

主要参考以下博文:

①使用场景

随着各种应用场景的限制,芯片在运行时往往需要在不同的应用下切换不同的时钟源,例如低功耗和高性能模式就分别需要低频率和高频率的时钟。两个时钟源有可能是同源且同步的,也有可能是不相关的。直接使用逻辑进行时钟切换大概率会导致分频时钟信号出现毛刺现象,所以时钟切换逻辑也需要进行特殊处理;

当使用纯组合逻辑进行时钟切换时,容易出现毛刺现象:

仅使用组合逻辑 :

②毛刺出现情况

下面给出一种毛刺现象:

因为当前为纯组合逻辑,因此,当sel信号变化时,Clk_Out 信号会立马++从clk0的波形跳转为clk1的波形++。sel信号可在任意时间段进行变化,因此,当clk0和clk1电平相反时切换时钟,肯定会发生毛刺;(如图中时钟切换时,clk0为高电平,clk1为低电平)

③时钟切换方案

在两个电平相反的时候切换时钟,肯定会发生毛刺;在电平相同时切换时钟,即使不产生毛刺,时钟切换后的第一个时钟周期的占空比也不是理想的。所以为了避免毛刺的产生,需要在两个时钟都是下降沿的时候进行时钟切换;

时钟切换电路在各自不同的时钟下降沿 时对sel信号进行缓存,同时将各自缓存的sel信号作为反馈控制信号控制另一个时钟的输入,使得最终只有一路时钟有效;

设计电路如下:

④Verilog代码

当sel = 0 时,clk_out信号输出频率为clk0时钟频率;

当sel = 1 时,clk_out信号输出频率为clk1时钟频率;

注意时钟切换的时机 ,由波形图可知,时钟切换均在clk0和clk1下降沿时发生;

cpp

`timescale 1ns/1ns

module huawei6(

input wire clk0 ,

input wire clk1 ,

input wire rst ,

input wire sel ,

output reg clk_out

);

//*************code***********//

reg q0, q1;

//sel = 0 → clk0

always @(negedge clk0 or negedge rst) begin

if (!rst) q0 <= 1'b0;

else q0 <= ~q1 & ~sel;

end

always @(negedge clk1 or negedge rst) begin

if (!rst) q1 <= 1'b0;

else q1 <= ~q0 & sel;

end

always @(*) begin

clk_out <= (q0&clk0) | (q1&clk1);

end

//*************code***********//

endmodule