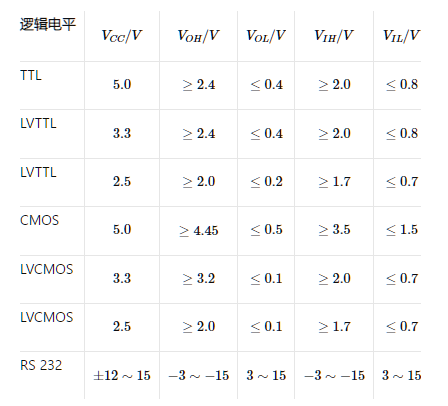

FPGA 在与外界进行信息交换时,为了确保信息的正确性,发送和接收信息都要对信息有认定的标准。在数字电路中,我们常用电压高低来表示"0"和"1",那么多高的电压才会被当作"1"呢,这个时候就需要一个标准,这个标准就是电平标准。

常见电平标准

TTL

TTL (Transistor - Transistor Logic,三极管 - 三极管逻辑电平) 是电平标准中的元老级成员。

在早期的数字电路中有广泛的应用,但是它有一些缺点,比如高电平的判决门限和供电电压之间的电压空间较大,容易造成信号的不稳定性;而且 5 V 的电压过于耗电。

LVTTL

LVTTL(Low Voltage Transistor - Transistor Logic,低压 TTL 电平标准)改进了 TTL 的缺点,将供电电压改为了 3.3 V 3.3V 3.3V,功耗也相应降低了,而且提升了信号稳定性。

CMOS

CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体电平)的特点是功耗较低,可以根据电路的工作状态自动调整功耗。

LVCMOS

LVCMOS(Low Voltage Complementary Metal Oxide Semiconductor,低压 CMOS 电平标准)在 CMOS 的基础上进一步降低供电电压,降低功耗。LVCMOS 在低功耗、中低速数字电路中非常受欢迎。

LVDS

LVDS,全称是Low Voltage Differential Signaling,是一种利用低压差分信号传输高速信号的电平标准,有低压,低功耗,噪声抑制能力强的特点。LVDS 的输出电压摆幅极小,只有 ± 350 m V \pm 350mV ±350mV,电流只有 3.5 m A 3.5mA 3.5mA 左右。由于其超低功耗和超快数据传输速率,常用于高速数据传输。