1、选择tools-》Megawizard plug-In manager

2、选择第一项,下一步

3、选择ATPLL,芯片系列、和输出文件类型,输出文件名称,单击next

4、出现配置PLL界面

5、选择输入时钟频率,单击next

6、生成reset、和locked信号,单击next

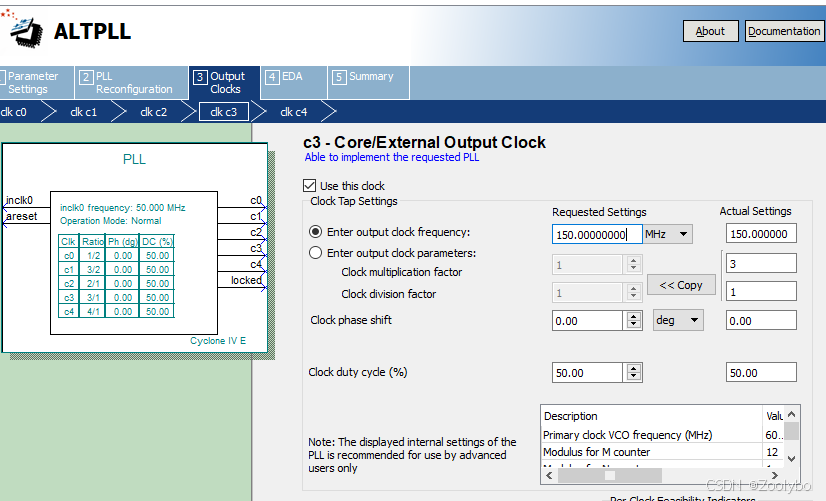

7、一路next到这个界面

8、我们输出5路信号

c0 25MHZ,c2 75MHZ,C2 100 MHZ C3 150MHZ c4 200MHZ,配置如下图

9、后面的可以保持默认,直接点击finish出现下图

10、继续点击finish ,选择yes

11、文件就生成了,IP和调用ok,可以在files里面查看生成的问价