仿真参考资料如下:

https://zhuanlan.zhihu.com/p/386057087

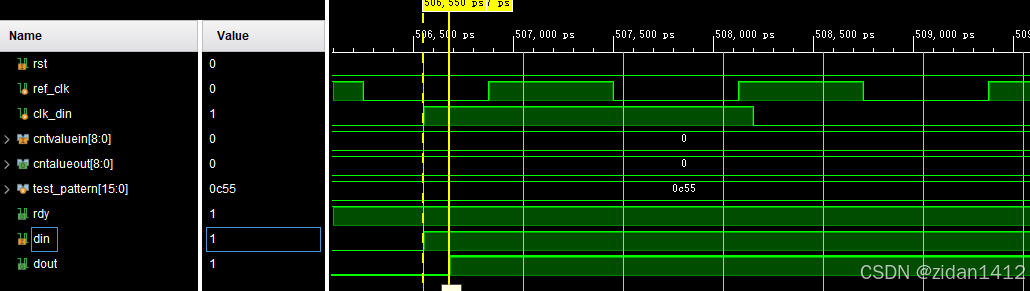

`timescale 1 ns/1 ps

module tb_idelay3_ctrl();

parameter REF_CLK = 2.5 ; // 400MHz

parameter DIN_CLK = 3.3 ; // 300MHz

reg ref_clk ;

reg clk_din ;

reg rst ;

wire din ;

reg [8 : 0] cntvaluein;

wire [8 : 0] cntalueout ;

wire rdy ;

wire dout ;

reg [15 : 0] test_pattern = 16'h0c55;

reg [3 : 0] data_cnt = 4'h0;

initial begin

rst = 1;

ref_clk = 0;

clk_din = 0;

#500;

rst = 0;

end

always #(REF_CLK/2) ref_clk = ~ref_clk;

always #(DIN_CLK/2) clk_din = ~clk_din;

always @(posedge clk_din or posedge rst)begin

if(rst)

data_cnt <= 4'd0;

else

data_cnt <= data_cnt +1'd1;

end

assign din = test_pattern[data_cnt];

always @(posedge clk_din or posedge rst)begin

if(rst)

cntvaluein <= 9'd0;

else if(data_cnt == 4'd15)

cntvaluein <= cntvaluein +1'd1;

else;

end

idelay3_ctrl u_idelay_ctrl (

.ref_clk ( ref_clk ),

.rst ( rst ),

.din ( din ),

.cntvaluein ( cntvaluein ),

.cntalueout ( cntalueout ),

.rdy ( rdy ),

.dout ( dout )

);

endmodule

module idelay3_ctrl(

input ref_clk ,

input rst ,

input din ,

input [8 : 0] cntvaluein ,

output [8 : 0] cntalueout ,

output rdy ,

output dout

);

IDELAYCTRL #(

.SIM_DEVICE("ULTRASCALE") // Set the device version for simulation functionality (ULTRASCALE)

) inst_IDELAYCTRL (

.RDY(rdy), // 1-bit output: Ready output

.REFCLK(ref_clk), // 1-bit input: Reference clock input

.RST(rst) // 1-bit input: Active high reset input

);

IDELAYE3 #(

.CASCADE("NONE"), // Cascade setting (MASTER, NONE, SLAVE_END, SLAVE_MIDDLE)

.DELAY_FORMAT("TIME"), // Units of the DELAY_VALUE (COUNT, TIME)

.DELAY_SRC("IDATAIN"), // Delay input (DATAIN, IDATAIN)

.DELAY_TYPE("VAR_LOAD"), // Set the type of tap delay line (FIXED, VARIABLE, VAR_LOAD)

.DELAY_VALUE(0), // Input delay value setting

.IS_CLK_INVERTED(1'b0), // Optional inversion for CLK

.IS_RST_INVERTED(1'b0), // Optional inversion for RST

.REFCLK_FREQUENCY(400.0), // IDELAYCTRL clock input frequency in MHz (200.0-800.0)

.SIM_DEVICE("ULTRASCALE_PLUS"), // Set the device version for simulation functionality (ULTRASCALE,

// ULTRASCALE_PLUS, ULTRASCALE_PLUS_ES1, ULTRASCALE_PLUS_ES2)

.UPDATE_MODE("ASYNC") // Determines whe n updates to the delay will take effect (ASYNC, MANUAL,SYNC)

)

IDELAYE3_inst (

.CASC_OUT(), // 1-bit output: Cascade delay output to ODELAY input cascade

.CNTVALUEOUT(cntalueout), // 9-bit output: Counter value output

.DATAOUT(dout), // 1-bit output: Delayed data output

.CASC_IN(1'd0), // 1-bit input: Cascade delay input from slave ODELAY CASCADE_OUT

.CASC_RETURN(1'd0), // 1-bit input: Cascade delay returning from slave ODELAY DATAOUT

.CE(1'b0), // 1-bit input: Active-High enable increment/decrement input

.CLK(ref_clk), // 1-bit input: Clock input

.CNTVALUEIN(cntvaluein[8:0]), // 9-bit input: Counter value input

.DATAIN(), // 1-bit input: Data input from the logic

.EN_VTC(!rdy), // 1-bit input: Keep delay constant over VT

.IDATAIN(din), // 1-bit input: Data input from the IOBUF

.INC(1'b0), // 1-bit input: Increment / Decrement tap delay input

.LOAD(1'b1), // 1-bit input: Load DELAY_VALUE input

.RST(1'b0) // 1-bit input: Asynchronous Reset to the DELAY_VALUE

);

endmodule

|--------------------|------------|

| delay tap =0 | 127ps |

| delay tap =1 | 131ps |

| delay tap =2 | 135ps |

| delay tap =3 | 139ps |

| ... | |

| delay tap =100 | 527ps |

| delay tap =200 | 927ps |

| delay tap =219 | 1003ps |

| delay tap =468 | 1999ps |

| delay tap =511 | 2171ps |

根据上表可知 delay_tap = 127 + 4N (N的取值为0到511)

根据简单的计算可知,双沿300M数据(对应单沿600M数据),数据持续时间为1.66ns,取到中间需要0.83ns,对应177taps