这篇文章躺在我网盘里N年了,记得是刚入门时候总结的,所以本文列举的芯片有点老,仅供参考,后面有时间我们在按照最新的架构进行分析。

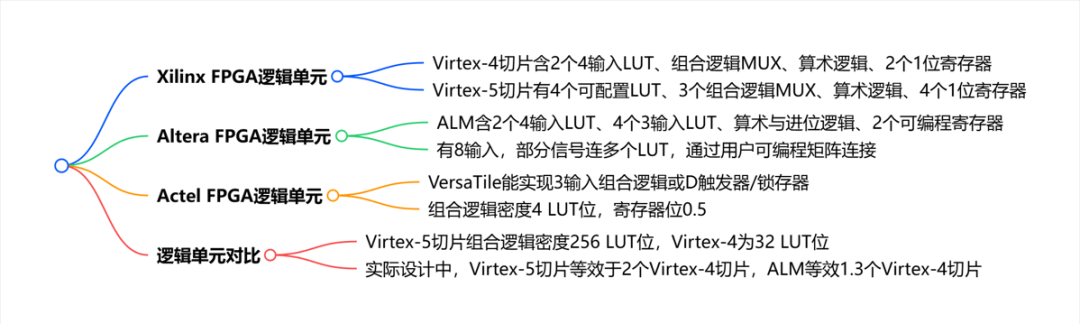

今天主要对Xilinx、Altera和Actel三家 FPGA 中使用的逻辑单元架构进行对比,最后对这三家逻辑量换算进行说明。

FPGA介绍

不介绍了...

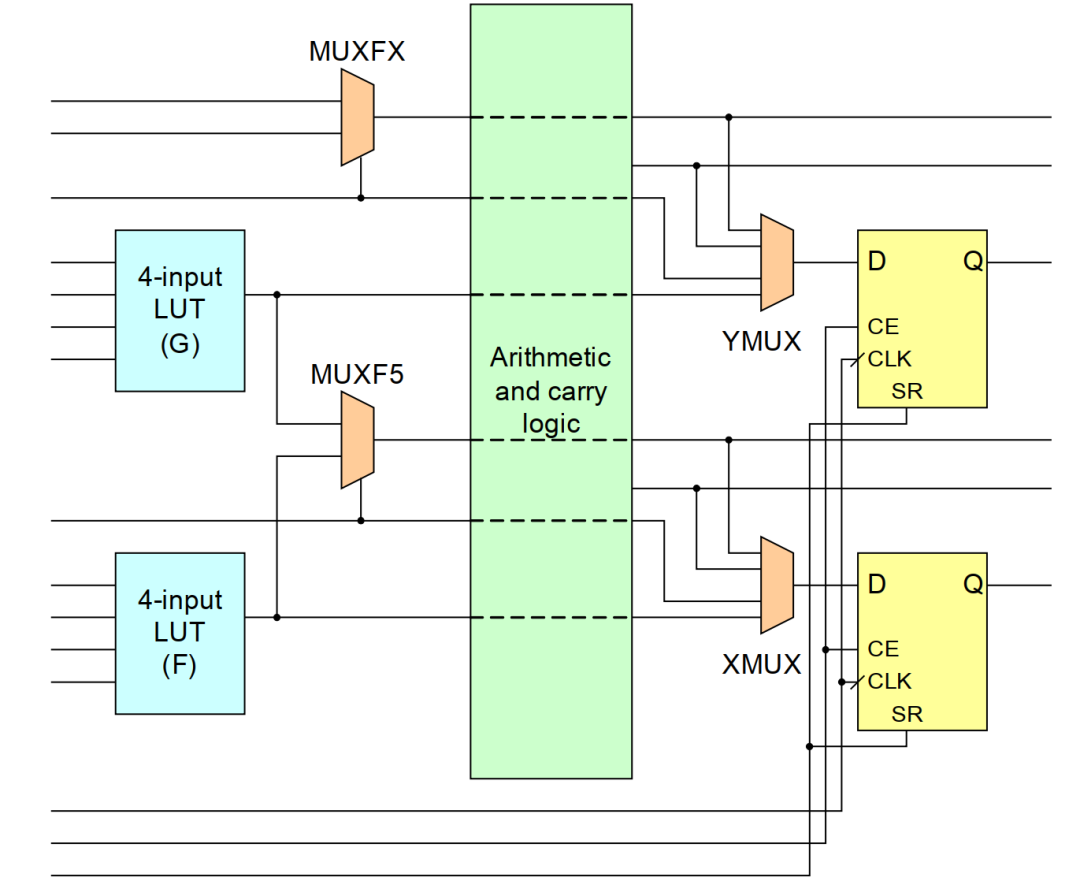

Virtex-4 (或者更早的架构) Slices

Xilinx FPGA 中的基本可编程逻辑模块称为 slice。

此架构(稍作修改)用于 Virtex-5 之前的所有 Virtex FPGA 系列和迄今为止的所有 Spartan FPGA 系列(至少,直到 Spartan-3A)。

Virtex-4 FPGA slice 包括:

-

两个 4 输入查找表(Look-Up Tables),可以实现任何 4 输入Bool函数,用作组合函数生成器(一个查找表标记为"F",另一个标记为"G")。

-

两个专用的用户控制组合逻辑复用器(MUXF5 和 MUXFX)。MUXF5 可用于组合slice的查找表(LUT)的输出,从而实现 5 输入组合电路。MUXFX 用于组合其他 MUXF5 和 MUXFX(来自其他slice)的输出。

-

专用算术逻辑(两个 1 位加法器、进位链和两个专用与门,用于快速高效的乘法)。

-

两个 1 位寄存器,可以配置为触发器或锁存器。这些寄存器的输入由 YMUX 和 XMUX 多路复用器选择。请注意,这些多路复用器不受用户控制:路径在 FPGA 编程期间选择。

Virtex-4 slice的简化图如下所示。

这种基于四输入查找表的架构可以被认为是经典的架构,也是前期国产FPGA的基本架构。

要实现一个四输入查找表(4-input LUT)需要 16 位内存。然后,我们可以通过计算查找表位的总数来测量可放入Slices 中的组合逻辑量。

| Xilinx Virtex-4 slice | |

|---|---|

| Combinational logic density (in LUT bits) | 32 |

| Register bits | 2 |

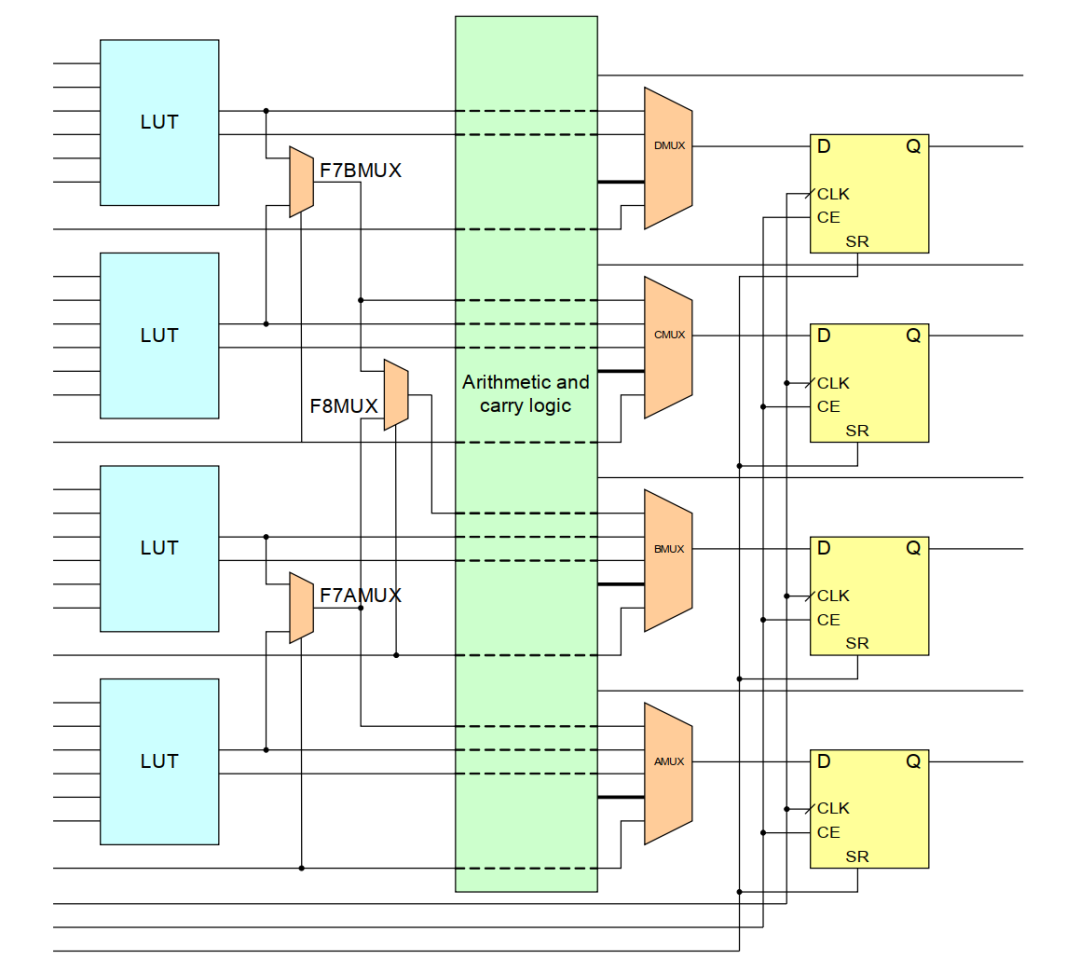

Virtex-5 Slices

Virtex-5 Slices包括:

-

四个查找表(Look-Up Tables),可以配置为具有 1 位输出的 6 输入查找表或具有 2 位输出的 5 输入查找表。

-

三个专用的用户可控制的组合逻辑复用器(F7AMUX、F7BMUX 和 F8MUX)。F7AMUX 和 F7BMUX 组合Slices的查找表的输出以实现 7 输入组合电路。F8MUX 用于组合 F7AMUX 和 F7BMUX 的输出。

-

专用算术逻辑(两个 1 位加法器和一个进位链)。

-

四个 1 位寄存器,可配置为触发器或锁存器。这些寄存器的输入由 AMUX-DMUX 多路复用器选择。请注意,这些多路复用器不受用户控制:路径在 FPGA 编程期间选择。

与之前架构的主要区别:

-

可配置的 6 对 1 或 5 对 2 查找表,而不是 4 对 1 查找表。

-

每个切片有 4 个查找表(LUT)和 4 个寄存器位。

-

专用算术逻辑电路不包括专用与门。

Virtex-5 FPGA Slices的简化图如下:

例如,在 Virtex-5 中,仅用一个查找表就可以实现一个完整的 4 选 1 多路复用器。

| Xilinx Virtex-5 slice | |

|---|---|

| Combinational logic density (in LUT bits) | 256 |

| Register bits | 4 |

Altera ALMs

Altera FPGA(Stratix 和 Cyclone 系列)使用略有不同的逻辑块,称为"自适应逻辑模块"("Adaptive Logic Modules,ALM)。

ALM 资源包括:

-

两个四输入查找表和四个三输入查找表用于组合逻辑实现。

-

专用算术和进位逻辑。

-

两个可编程寄存器。

需要注意的是,一个自适应逻辑模块(ALM)只有 8 个输入,这比查找表(LUT)的输入总数要少。这意味着一些输入信号连接到不止一个查找表。在自适应逻辑模块中有几个输入信号复用器,它们形成一种可由用户编程的互连矩阵(在配置时)。请注意,并非所有的连接都是可能的。更多细节请参考 Stratix-IV 器件手册。

Altera ALM 的架构简化图如下:

| Altera ALM | |

|---|---|

| Combinational logic density (in LUT bits) | 64 |

| Register bits | 2 |

Actel VersaTile

Actel 主要生产用于航空航天和军事应用的 FPGA。与顶级的 Xilinx 和 Altera 设备相比,Actel 的 FPGA 提供的逻辑资源较少。

Actel 基于 flash 的 FPGA(如 ProASIC-3)的基本逻辑模块称为 VersaTile。每个 VersaTile 单元可以实现以下任何一种:

- 任何三输入组合逻辑函数或 D 触发器/锁存器。

一个 VersaTile 只能实现其中之一,不能两者兼得。因此,为了进行比较,我们将查找表和寄存器位除以 2。

| Actel VersaTile | |

|---|---|

| Combinational logic density (in LUT bits) | 4 |

| Register bits | 0.5 |

总结

这些架构非常不同,所以很难客观地对它们进行比较。所以接下来的比较只能直观上进行应用,其结果只能进行参考。。

通常,对于 FPGA 设计来说,瓶颈通常是查找表(LUT)的数量(而不是寄存器的数量)。从这个角度来看,可以说一个 Virtex-5 Slices理论上可以替代 8 个 Virtex-4 Slices或 4 个自适应逻辑模块(ALM)。但在实际设计中,不可能利用所有的资源。

| Logic block | Virtex-4 slices equivalent |

|---|---|

| Xilinx Virtex-4 slice (reference) | 1 |

| Xilinx Virtex-5 slice | 2 |

| Altera ALM | 1.3 |

| Actel VersaTile | 0.25 |