文章目录

- [一、状态机思想写一个 LED流水灯的FPGA代码](#一、状态机思想写一个 LED流水灯的FPGA代码)

- [二、 CPLD和FPGA芯片的主要技术区别是什么? 它们各适用于什么场合?](#二、 CPLD和FPGA芯片的主要技术区别是什么? 它们各适用于什么场合?)

- [三、 在hdlbitsFPGA教程网站上进行学习](#三、 在hdlbitsFPGA教程网站上进行学习)

一、状态机思想写一个 LED流水灯的FPGA代码

c

module led_flow (

input clk, // 时钟(DE2-115默认50MHz)

input rst_n, // 复位信号(低有效)

output reg [7:0] led // 8位LED输出

);

// 状态定义:4个状态循环

parameter S0 = 2'b00, S1 = 2'b01, S2 = 2'b10, S3 = 2'b11;

reg [1:0] state, next_state;

// 分频计数器:控制状态切换速度(约0.5秒)

reg [24:0] cnt;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) cnt <= 0;

else cnt <= cnt + 1;

end

// 状态转移逻辑

always @(posedge clk or negedge rst_n) begin

if (!rst_n) state <= S0;

else if (cnt == 25'd25_000_000) state <= next_state;

end

// 状态转移条件

always @(*) begin

case (state)

S0: next_state = S1;

S1: next_state = S2;

S2: next_state = S3;

S3: next_state = S0;

default: next_state = S0;

endcase

end

// 输出逻辑(Moore型)

always @(*) begin

case (state)

S0: led = 8'b0000_0001;

S1: led = 8'b0000_0010;

S2: led = 8'b0000_0100;

S3: led = 8'b0000_1000;

default: led = 8'b0000_0001;

endcase

end

endmodule仿真测试代码

bash

`timescale 1ns/1ns

module tb_led_flow();

reg clk, rst_n;

wire [7:0] led;

led_flow uut (clk, rst_n, led);

initial begin

clk = 0;

forever #10 clk = ~clk;

end

initial begin

rst_n = 0;

#100 rst_n = 1; // 释放复位

#50000000 $finish; // 仿真运行约1秒(50MHz时钟)

end

initial begin

$monitor("Time=%t, led=%b", $time, led);

end

endmodule二、 CPLD和FPGA芯片的主要技术区别是什么? 它们各适用于什么场合?

1、CPLD适用场景

简单逻辑控制

接口转换(如UART、SPI协议桥接)

状态机实现(电梯控制、交通灯系统)

低复杂度信号处理

数字信号滤波

简单的时序逻辑(计数器、分频器)

快速响应系统

工业实时控制(PLC模块)

电源管理(上电时序控制)

非易失性需求

车载电子(断电后配置保留)

嵌入式系统的引导逻辑

2、FPGA适用场景

高复杂度算法加速

图像处理(HDR、边缘检测)

通信协议(5G基带处理、加密算法)

大规模并行计算

数据中心加速(AI推理、数据库优化)

科学计算(矩阵运算、FFT变换)

动态可重构系统

软件定义无线电(SDR)

自适应硬件(运行时逻辑切换)

ASIC原型验证

芯片流片前的功能验证

复杂IP核(CPU、GPU)的仿真

三、 在hdlbitsFPGA教程网站上进行学习

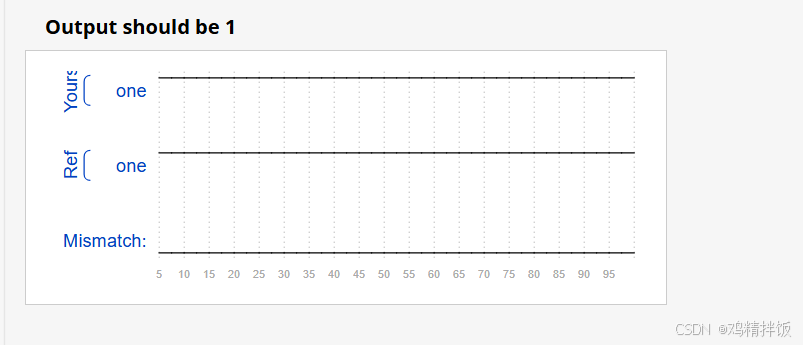

1、练习题1

构建一个没有输入和一个输出的电路。该输出应始终驱动 1 (或 logic high)。

c

module top_module( output one );

// Insert your code here

assign one = 1'b1;

endmodule

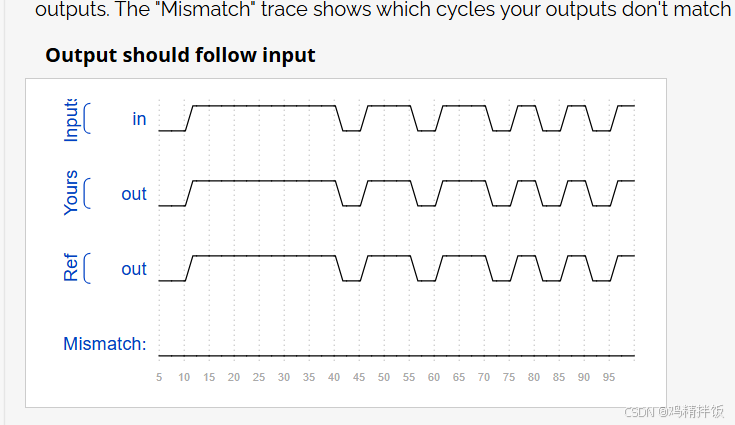

2、练习题2

创建一个具有一个 input 和一个 output 的模块,其行为类似于一条线。

bash

module top_module( input in, output out );

// 连续赋值:输出端口out始终跟随输入端口in的变化

assign out = in;

endmodule

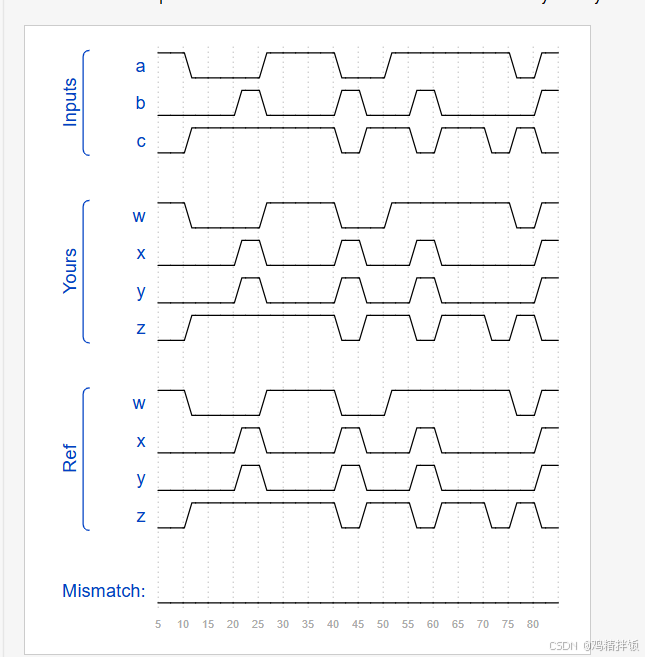

练习题3

创建一个具有 3 个输入和 4 个输出的模块,其行为类似于进行以下连接的电线:

a -> w

b -> x

b -> y

c -> z

bash

module top_module(

input a,b,c,

output w,x,y,z );

// 直接连接各个端口

assign w = a; // 输入a直连输出w

assign x = b; // 输入b直连输出x

assign y = b; // 输入b直连输出y

assign z = c; // 输入c直连输出z

endmodule

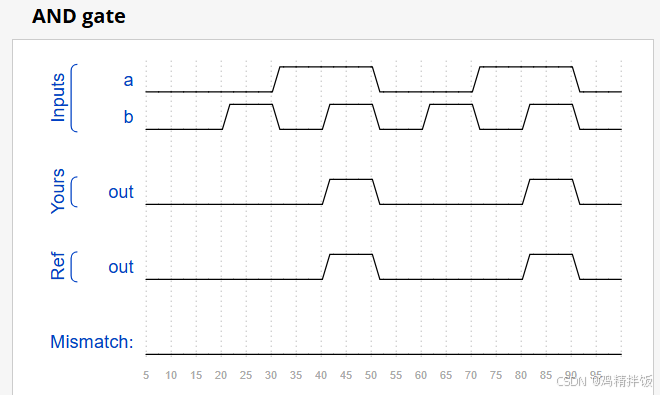

练习题4

创建一个实现 AND 门的模块。

此电路现在有三根线(、 和 )。Wires 和 already has values driven by the input ports.但 wire 目前不受任何因素驱动。编写一个使用信号 和 的 AND 驱动的语句。aboutaboutassignoutab

bash

module top_module(

input a,

input b,

output out );

// 使用连续赋值语句驱动输出

assign out = a & b; // 按位与操作符

endmodule

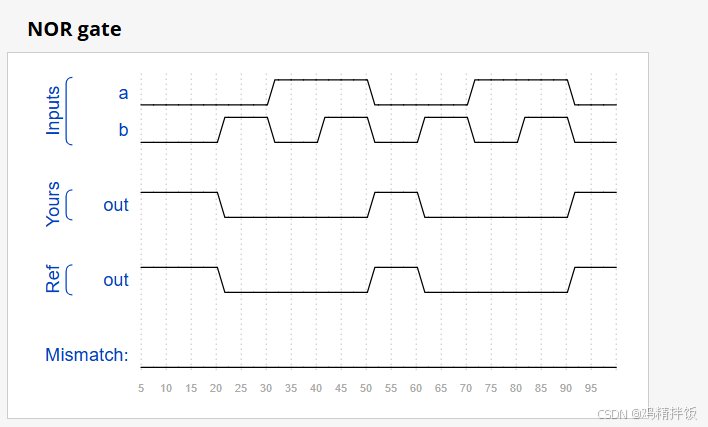

练习题5

创建一个实现 NOR 门的模块。NOR 门是输出反转的 OR 门。用 Verilog 编写 NOR 函数时需要两个运算符。

bash

module top_module(

input a,

input b,

output out );

// 使用 OR 运算符和取反运算符组合实现 NOR 门

assign out = ~(a | b); // 先执行 OR 运算再取反

endmodule