深入解析ARM与RISC-V架构的Bring-up核心流程

作者:嵌入式架构探索者 | 2023年10月

引言

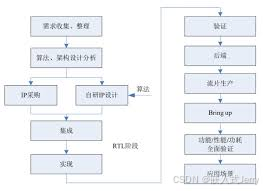

在嵌入式开发中,处理器的Bring-up(启动初始化)是系统运行的第一道门槛。ARM和RISC-V作为两大主流架构,其Bring-up流程既有共性(如基础硬件验证)又存在显著差异(如安全模型和调试机制)。本文将从底层寄存器操作到工具链实践,深入解析两者的核心知识点。

一、架构级Bring-up的本质

定义 :

架构级Bring-up是指针对特定处理器核心(如ARM Cortex-A53或RISC-V Rocket Core)的底层初始化,涉及以下核心任务:

- 复位向量(Reset Vector)配置

- 特权模式与异常处理设置

- 内存与缓存初始化

- 多核协同启动(SMP)

- 调试接口使能

与系统级Bring-up的区别:

- 架构级:聚焦CPU核心自身功能(如寄存器、流水线、中断控制器)

- 系统级:关注外设、操作系统和应用的协作

二、ARM架构Bring-up核心知识点

1. 复位与启动流程

复位向量表

- ARMv7/ARMv8复位向量地址:

- ARMv7 :固定地址

0x00000000或0xFFFF0000(通过SCTLR.V位控制) - ARMv8:分四个异常级别(EL0-EL3),复位入口由配置寄存器(如RVBAR_EL3)定义

- ARMv7 :固定地址

典型启动代码结构

assembly

/* ARMv7汇编示例:Cortex-A9启动代码 */

.section .vectors

b _reset // 复位向量

b undefined_instruction

b software_interrupt

...

_reset:

/* 1. 设置栈指针 */

ldr sp, =0x8000

/* 2. 关闭MMU和缓存 */

mrc p15, 0, r0, c1, c0, 0

bic r0, r0, #0x1 // 清除C1.M位(禁用MMU)

bic r0, r0, #0x4 // 禁用数据缓存

mcr p15, 0, r0, c1, c0, 0

/* 3. 初始化中断向量表 */

ldr r0, =vectors

mcr p15, 0, r0, c12, c0, 0 // 写入VBAR 2. 特权模式与安全扩展

ARM TrustZone安全启动

- 安全世界(Secure World)初始化流程 :

- EL3 Monitor代码配置安全状态(SCR寄存器)

- 加载安全Bootloader(如ARM TF-A的BL1/BL2)

- 隔离安全内存(TZC-400控制器配置)

多核唤醒(PSCI协议)

c

// Cortex-A72唤醒从核示例

void wakeup_core(int core_id) {

uint64_t entry = (uint64_t)&_start;

// 设置从核入口地址

mmio_write(0x1008EC000, entry); // 写入CPU Release Address寄存器

// 发送SEV指令触发唤醒

__asm__ volatile("sev");

} 3. 调试与异常处理

CoreSight调试系统

-

关键组件:

- ETM(嵌入式跟踪宏单元)

- DAP(调试访问端口)

-

调试命令示例(通过OpenOCD):

arm mcr p15 0 <reg> c1 c0 0 // 直接操作协处理器寄存器

三、RISC-V架构Bring-up核心知识点

1. 精简的启动流程设计

复位向量与机器模式

- RISC-V复位向量地址通常为

0x80000000(可自定义) - 复位后自动进入Machine模式(最高特权级)

最小启动代码示例

assembly

.section .text.init

.global _start

_start:

/* 1. 设置栈指针 */

la sp, _stack_end

/* 2. 清零BSS段 */

la a0, _bss_start

la a1, _bss_end

bss_clear_loop:

beq a0, a1, bss_clear_done

sw zero, 0(a0)

addi a0, a0, 4

j bss_clear_loop

bss_clear_done:

/* 3. 跳转到C入口 */

call main 2. 中断与异常机制

CLINT(核心本地中断器)配置

c

// RISC-V定时器中断初始化

void timer_init() {

// 设置定时器比较值

uint64_t interval = 1000000; // 1秒(假设时钟频率1MHz)

write_csr(mtimecmp, interval);

// 启用机器模式定时器中断

set_csr(mie, MIE_MTIE);

// 全局中断使能

set_csr(mstatus, MSTATUS_MIE);

} PLIC(平台级中断控制器)路由

c

// 配置UART中断

void plic_init() {

// UART中断号=3,优先级=1

volatile uint32_t *plic_priority = (uint32_t*)0x0C000000;

plic_priority[3] = 1;

// 启用目标核的中断

volatile uint32_t *plic_enable = (uint32_t*)0x0C002000;

plic_enable[0] |= (1 << 3);

} 3. 物理内存保护(PMP)

c

// 配置PMP保护区域

void pmp_config() {

// 允许0x80000000-0x8000FFFF的读写执行

pmpcfg0 = PMP_NAPOT | PMP_R | PMP_W | PMP_X;

pmpaddr0 = (0x80000000 >> 2) | 0xFFF; // NAPOT模式覆盖64KB

asm volatile("csrw pmpcfg0, %0" : : "r" (pmpcfg0));

asm volatile("csrw pmpaddr0, %0" : : "r" (pmpaddr0));

} 四、ARM vs RISC-V Bring-up对比

1. 启动复杂度

| 任务 | ARM | RISC-V |

|---|---|---|

| 复位向量配置 | 多级异常向量表(VBAR寄存器) | 单一入口地址(自由定义) |

| 特权模式切换 | 需处理EL3/EL2/EL1层级 | 仅需配置Machine/Supervisor模式 |

| 内存管理 | 必须初始化MMU | 可仅用PMP进行物理内存保护 |

2. 调试工具链

| 工具 | ARM | RISC-V |

|---|---|---|

| 硬件调试器 | J-Link、DS-5 | SiFive Freedom Debugger、FT2232 |

| 开源支持 | 有限(需商业授权) | 完善(OpenOCD + riscv-openocd) |

| 跟踪功能 | CoreSight ETM(高性能) | 自定义跟踪接口(如Nexus协议) |

五、实战案例分析

案例1:ARM Cortex-M4启动失败

现象 :执行__main()前HardFault

排查步骤:

- 检查向量表地址(VTOR寄存器)是否对齐到512字节边界

- 验证栈指针初始值是否指向有效RAM区域

- 使用

arm-none-eabi-objdump反汇编,确认复位向量跳转正确

案例2:RISC-V HiFive1开发板无法调试

现象 :OpenOCD连接超时

解决方案:

-

确认JTAG引脚连接(TCK、TMS、TDI、TDO)

-

添加复位信号控制配置:

adapter_nsrst_delay 100 reset_config srst_only

六、进阶方向与工具推荐

ARM开发者必备工具

- ARM Development Studio:全功能调试与性能分析

- Trusted Firmware-A (TF-A):官方参考启动代码库

- DS-5 Streamline:性能瓶颈分析工具

RISC-V开发者必备工具

- RISC-V GNU Toolchain:开源编译与调试套件

- Spike模拟器:指令集模拟与行为验证

- Chipyard框架:自定义RISC-V SoC生成

结语

无论是ARM还是RISC-V,架构级Bring-up的核心都在于对处理器设计哲学的深刻理解。

- ARM开发者需关注复杂的权限模型和安全扩展

- RISC-V开发者需善用其模块化设计带来的灵活性

掌握这些核心知识点,将助您在嵌入式系统的底层开发中游刃有余。