ADC简介

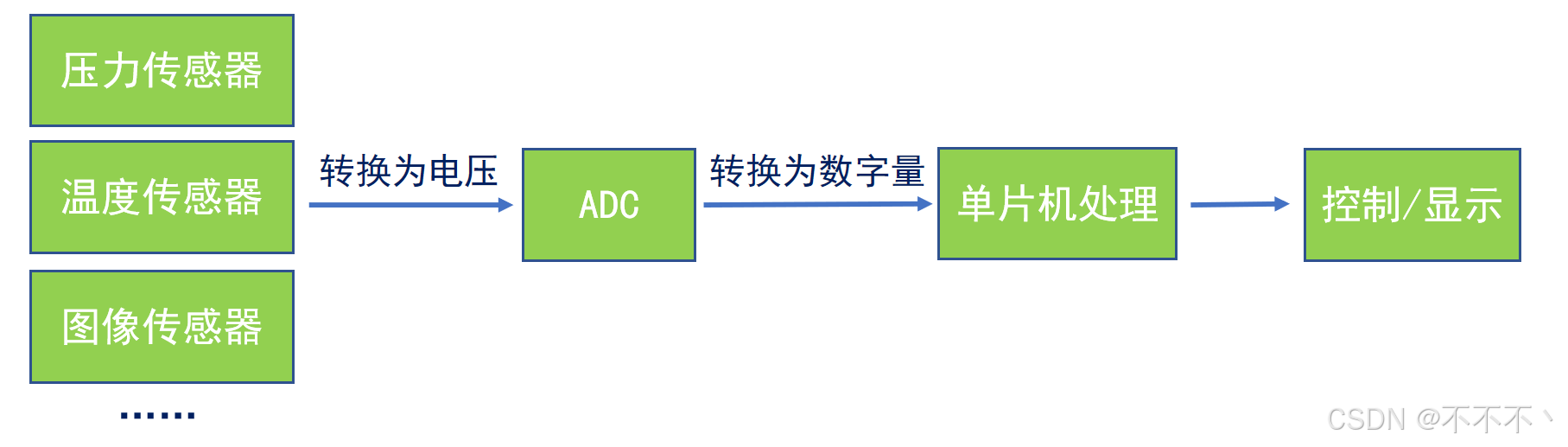

ADC,全称:Analog-to-Digita丨Converter,指模拟/数字转换器

ADC将模拟信号转换为数字信号。

基本原理

将连续时间的模拟信号转换为离散时间的数字信号。具体来说,ADC将模拟信号在时间上进行采样,然后通过量化操作将每个采样值转换为数字编码。这些数字编码可以用二进制代码表示。

ADC在转换过程中需要通过采样频率和量化精度来决定转换质量,采样频率和量化精度越高,转换质量越好,但同时也会增加转换的成本和复杂度。

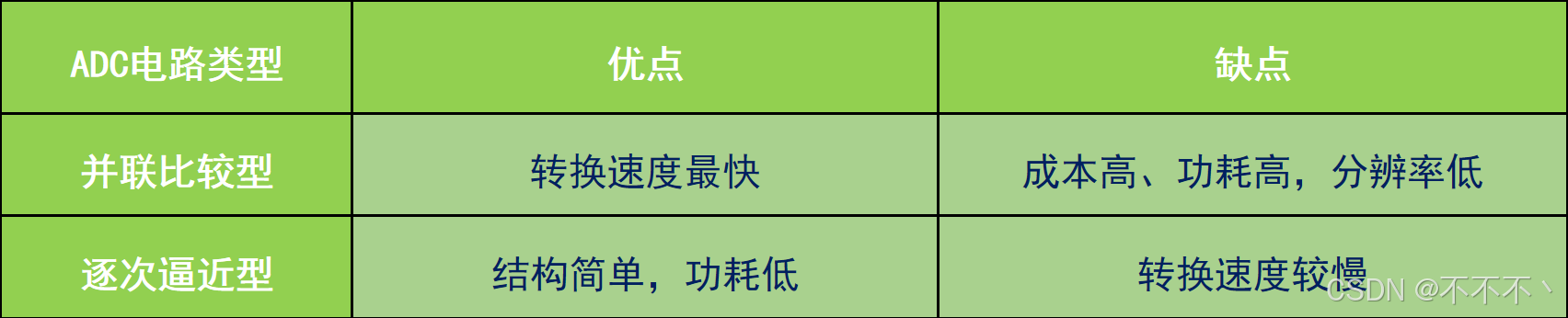

常见的ADC类型

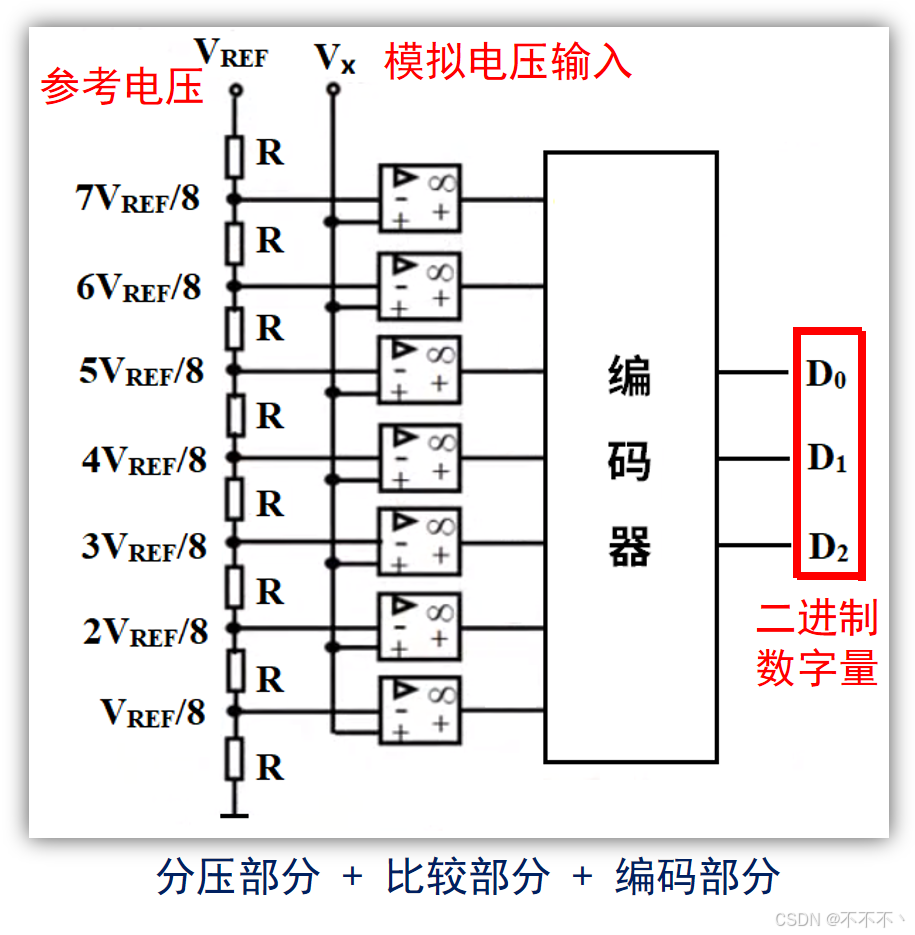

并联比较型

并联比较型 ADC 又称 Flash ADC,属于直接 ADC,能将输入的模拟电压直接转换为输出的数字量,不需要经过中间变量转换。它由一系列电压比较器组成,每个比较器将输入信号与唯一的分压后的参考电压进行比较。比较器的输出连接编码器电路的输入,产生二进制的输出。

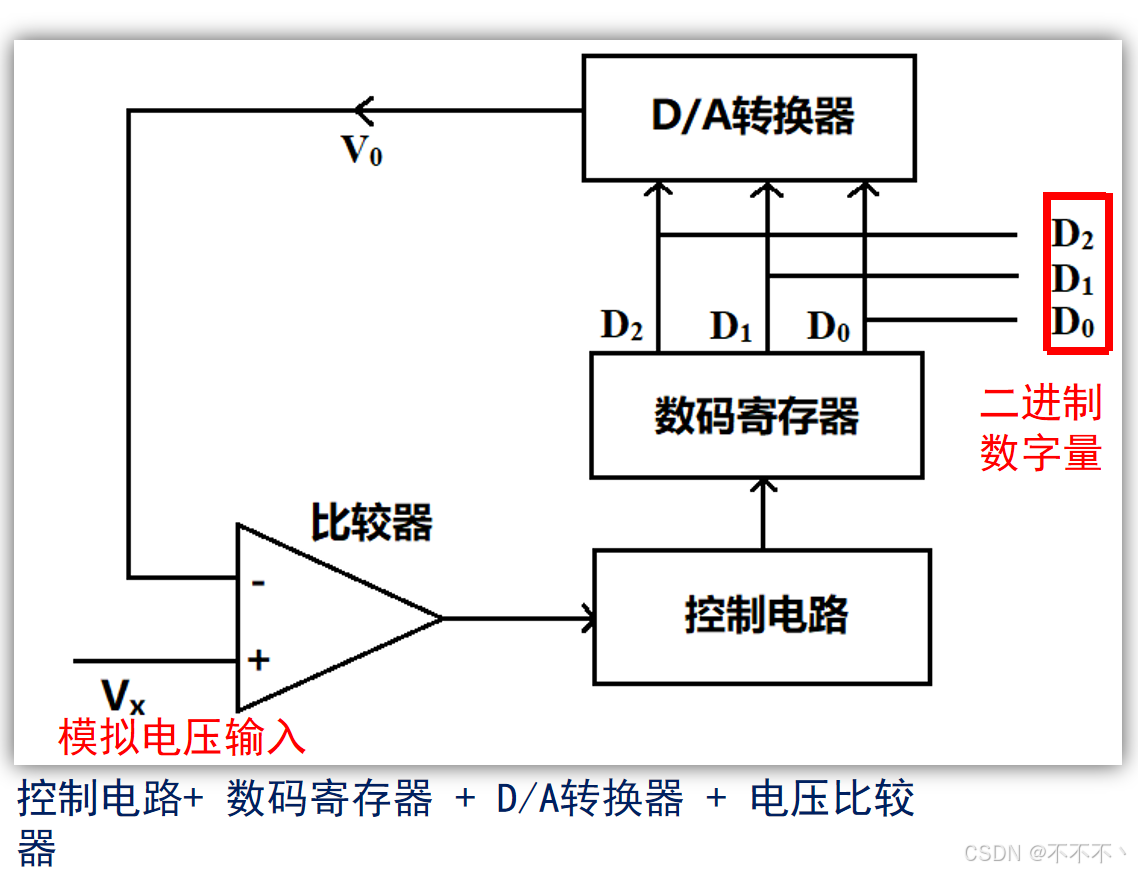

逐次逼近型

其原理是,设定一个数字量,通过 DAC 得到一个对应的输出模拟电压。将这个模拟电压和输入的模拟电压信号从最高位开始顺序地相比较,如果两者不相等,则调整所取的数字量,直到两个模拟电压相等为止,最后所取的这个数字量就是所求的转换结果。其过程像用天平去称量位置重量的物体,先加大砝码,再逐次添加或换用小砝码。

ADC特性参数

- 分辨率 表示ADC能分辨的最小模拟量,用二进制数表示,比如8、10、12、16位等。

- 转换时间 表示一次完成A/D转换所要的时间,转换时间越短,采样率越高。

- 精度 最小刻度基础上叠加各种误差的参数,精度受ADC性能、温度和气压等影响。

- 量化误差 用数字量近似表示模拟量,采用四舍五入原则,此过程产生的误差为量化误差。

ADC主要特性

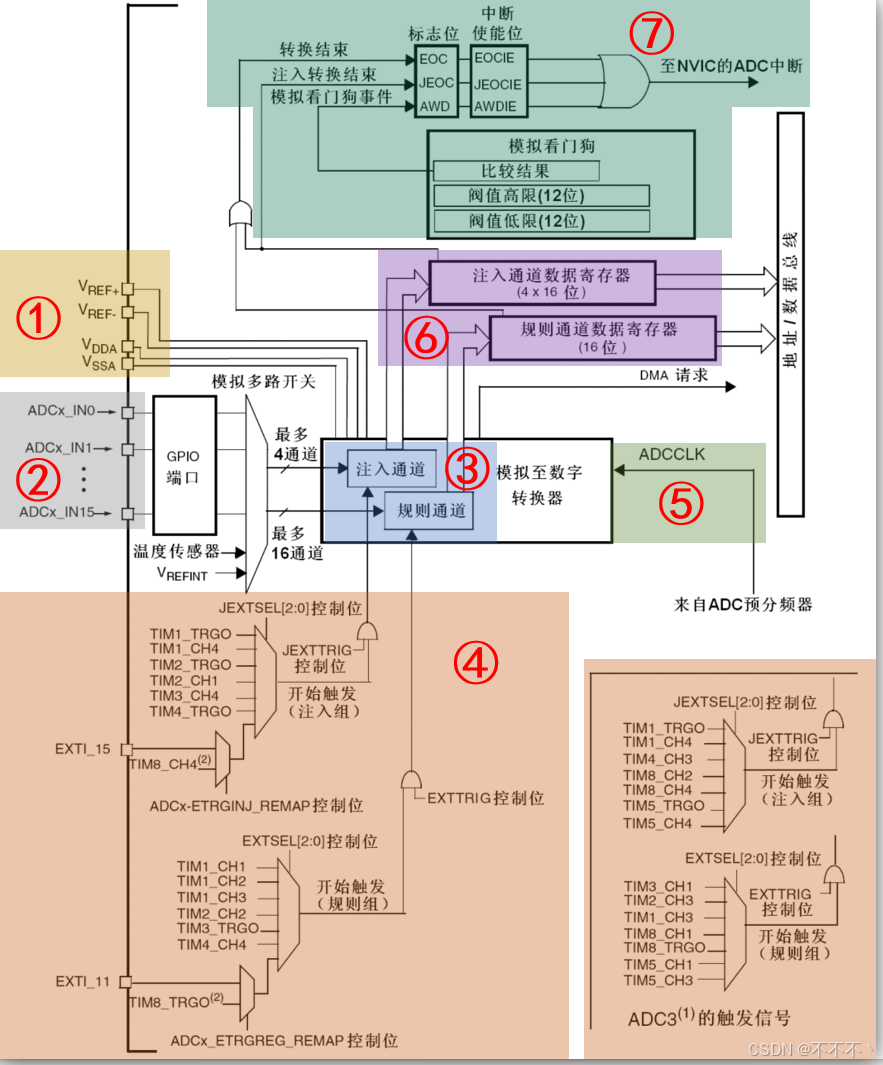

ADC内部框图

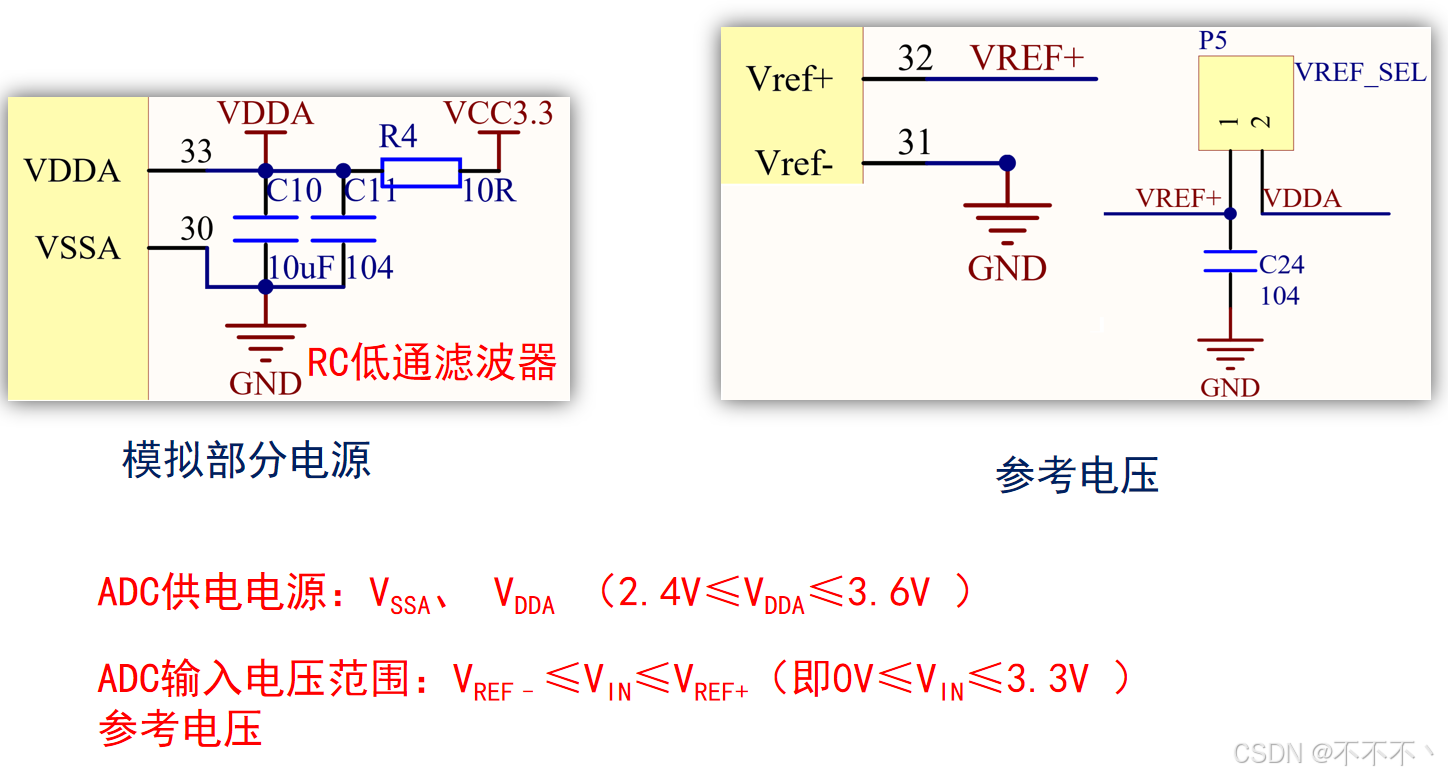

参考电压/模拟部分电压

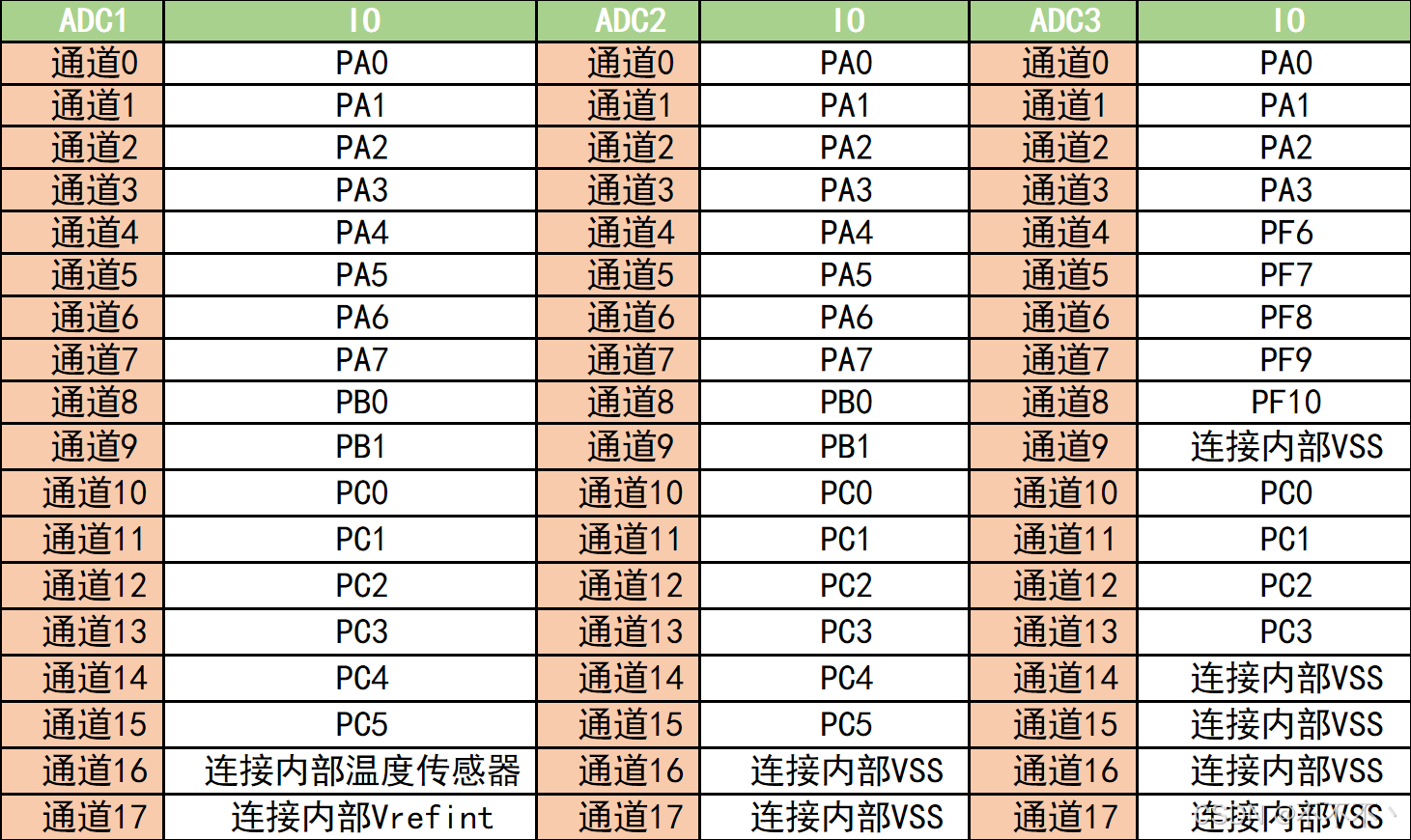

输入通道(F1系列)

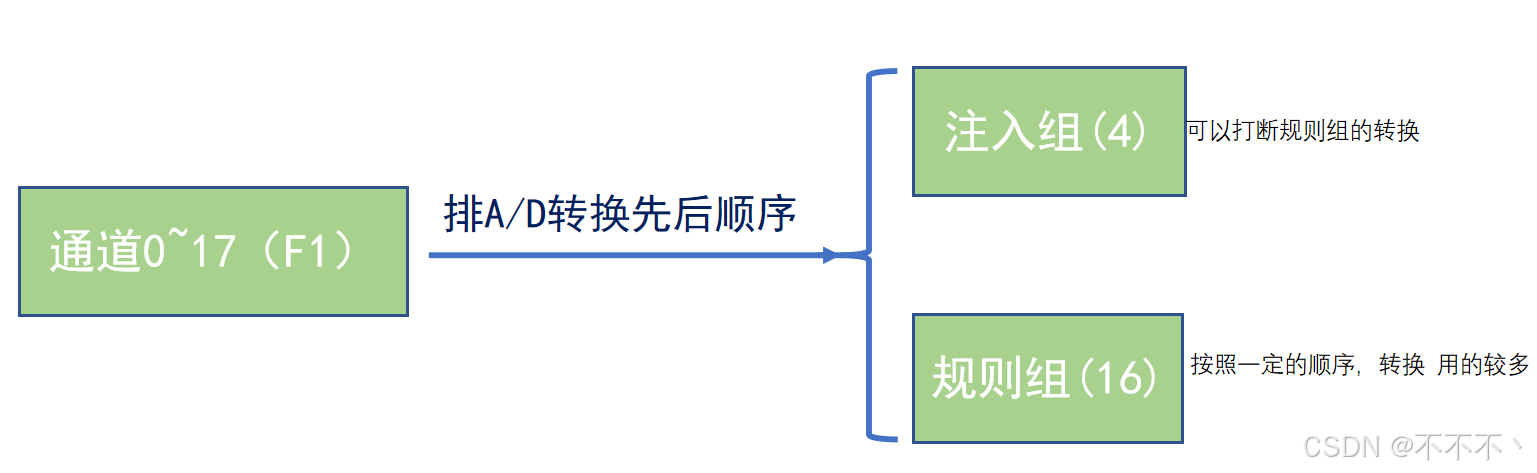

转换序列(F1系列)

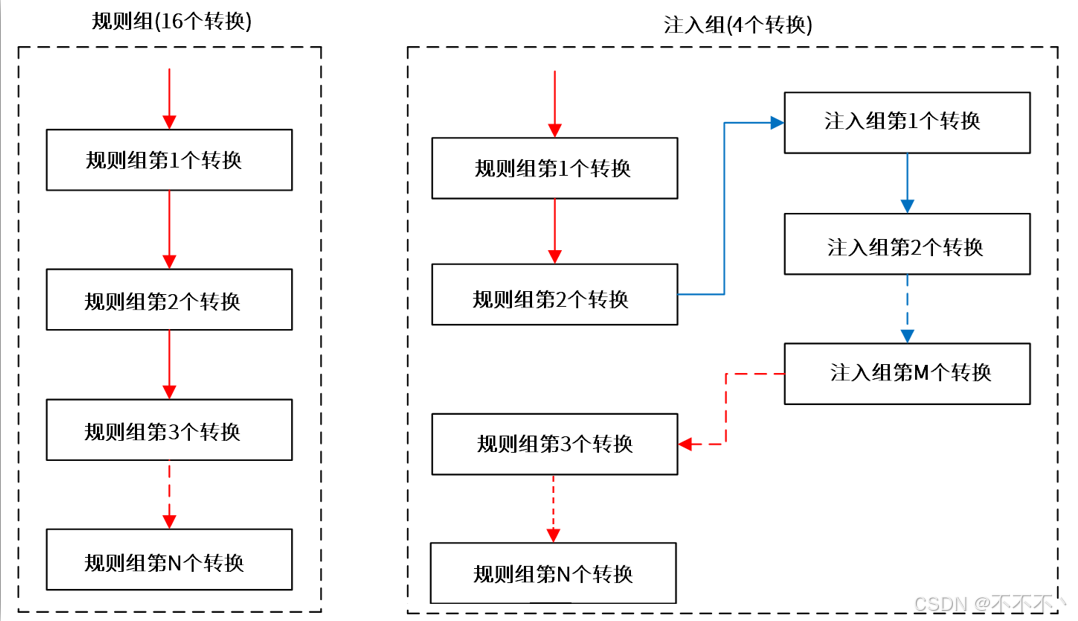

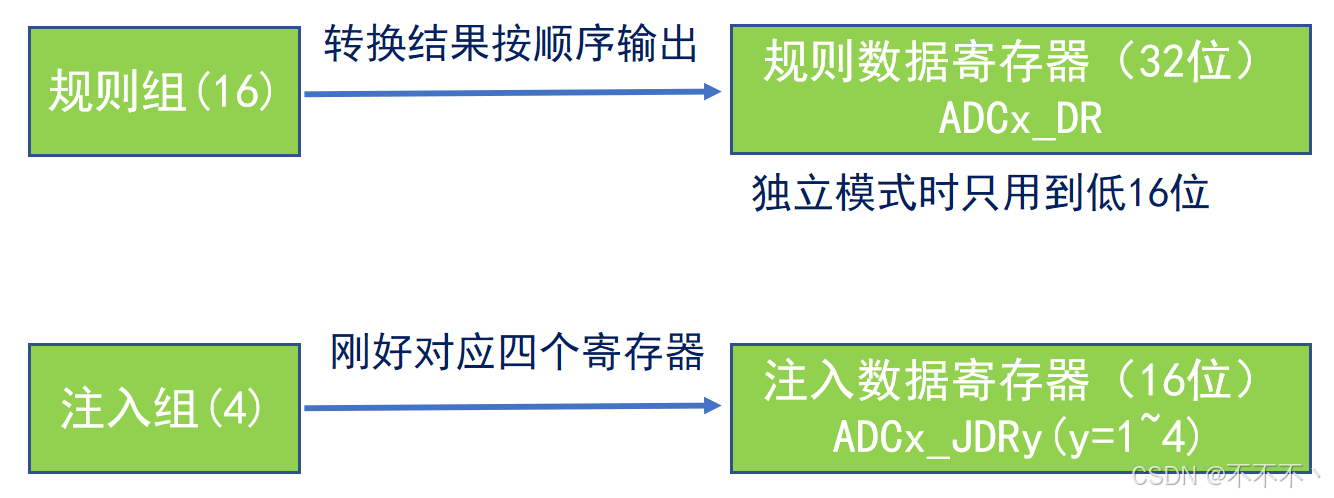

A/D转换被分为两组,规则组(常规转换组)和注入组(注入转换组)

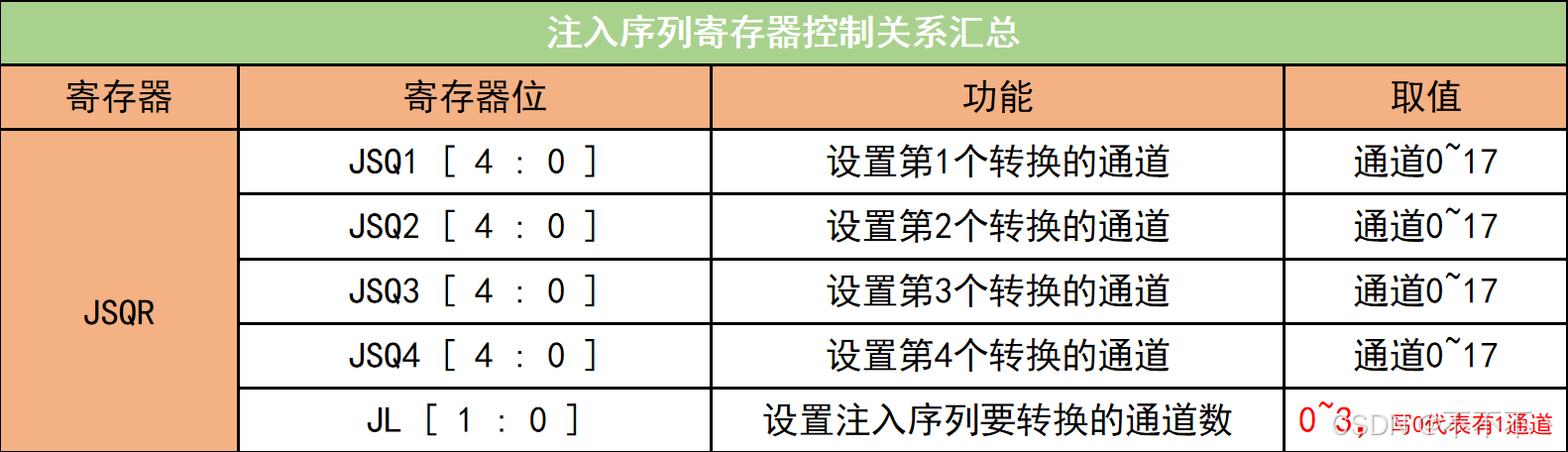

规则组最多可以有16个转换,注入组最多4个转换

注意:

注入组可以打断规则住转换。比如在规则组转换过程中,注入组启动,那么注入组被转换完成之后,规则组才得以继续转换。

执行优先级对比

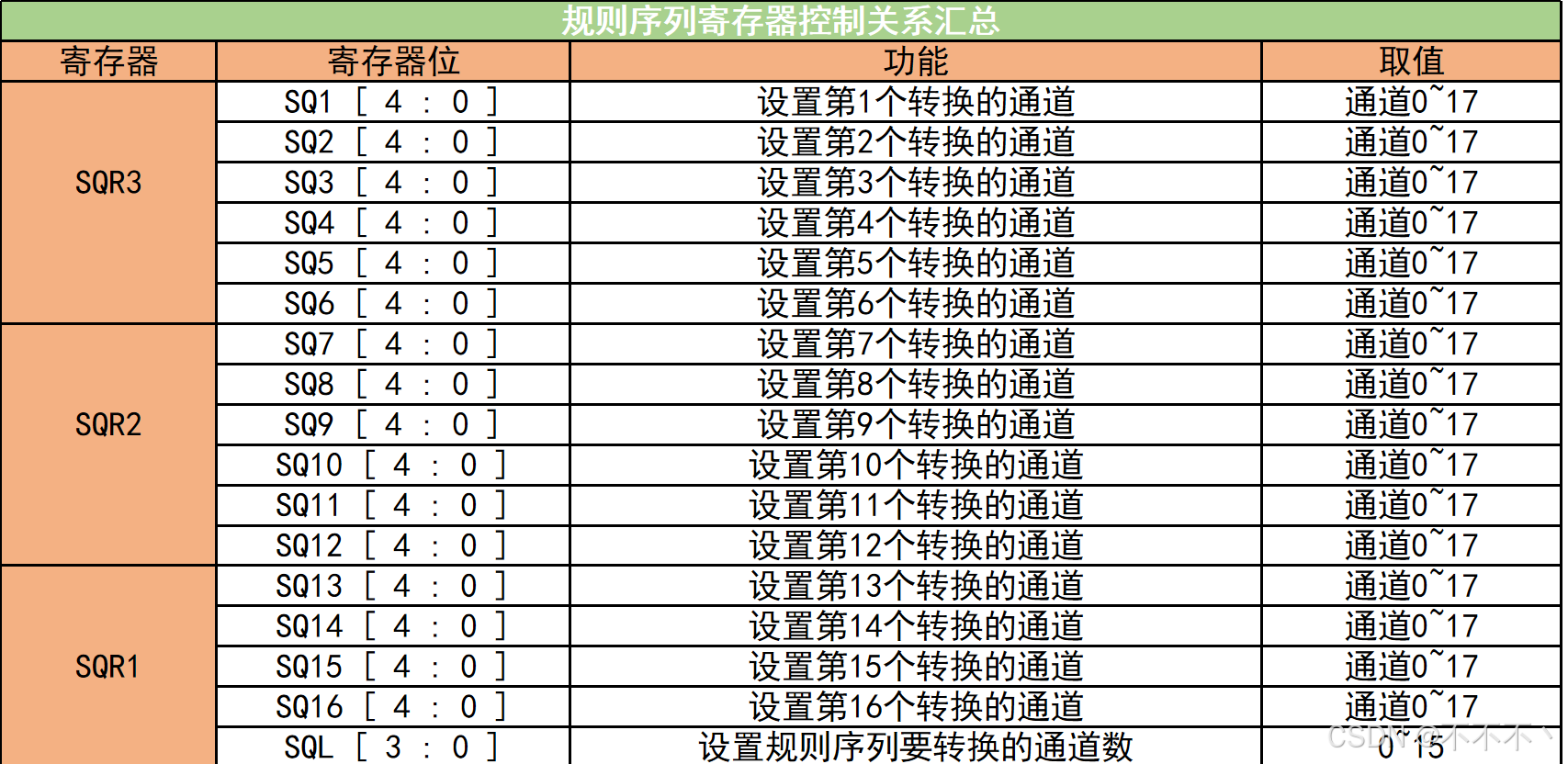

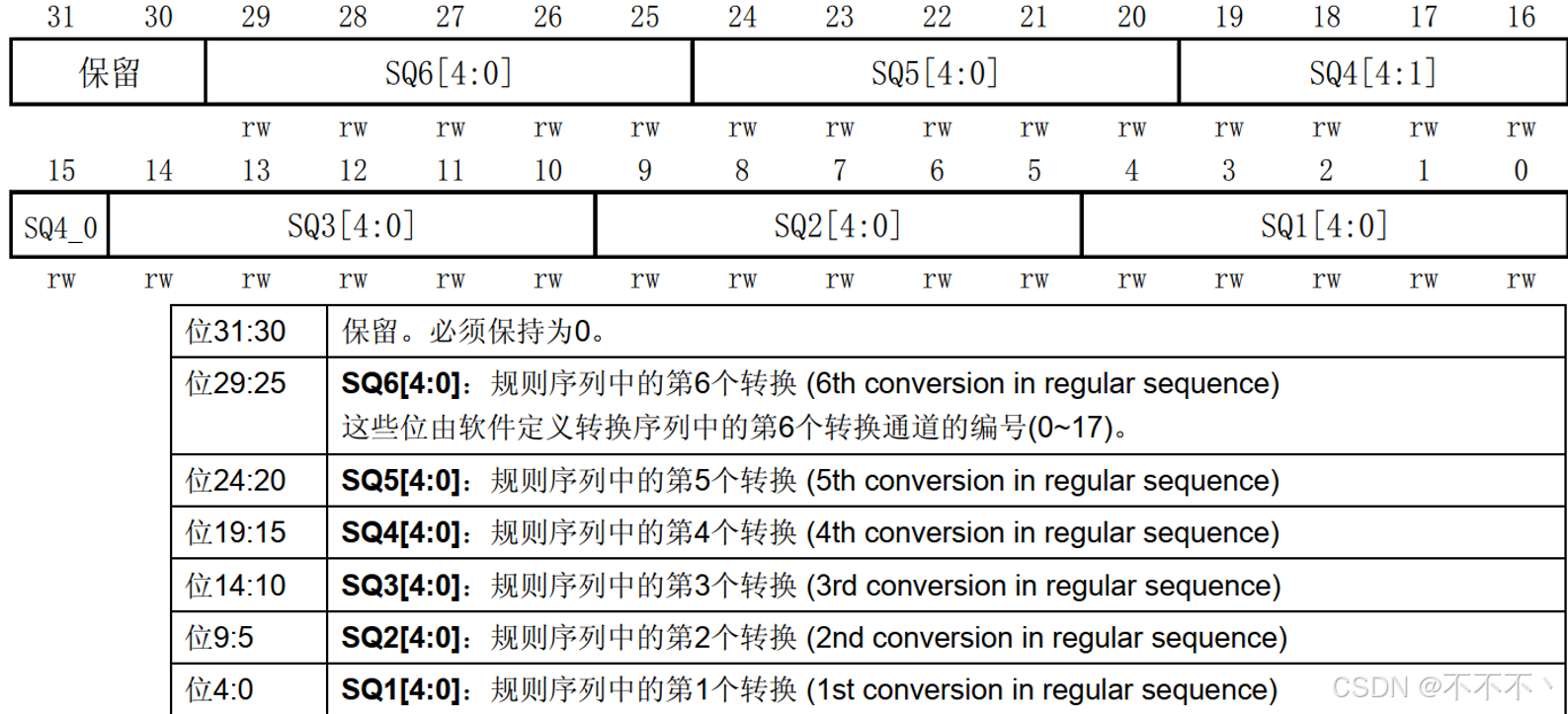

规则组序列控制寄存器

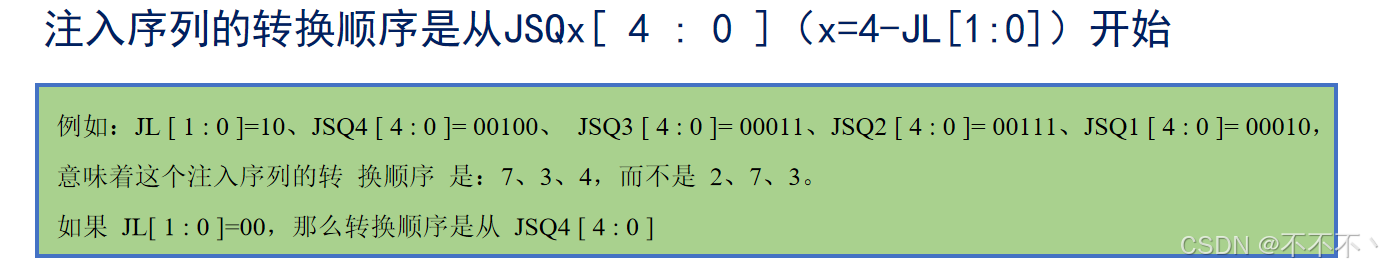

注入组序列控制寄存器

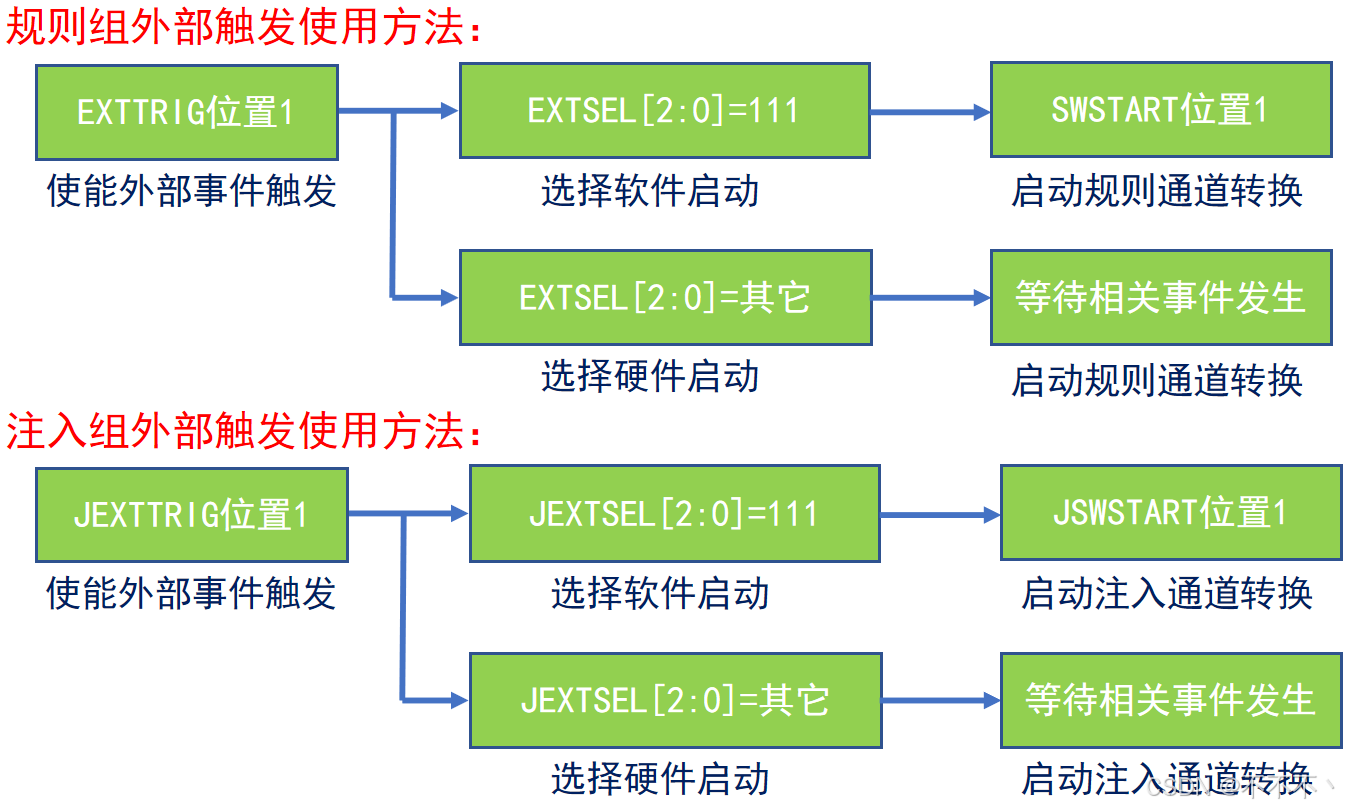

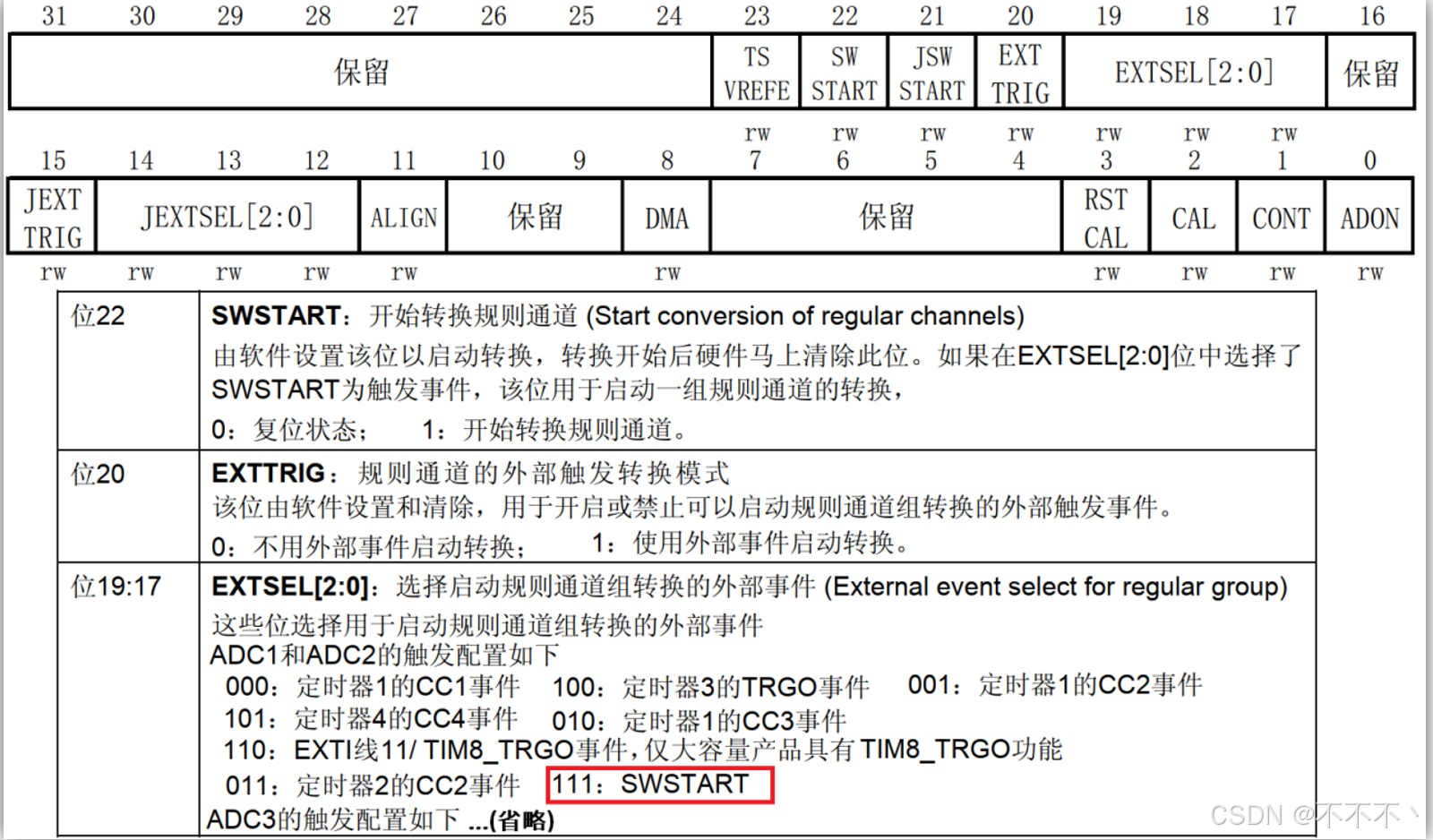

触发源

ADC触发方式有两种:

(1)ADON位触发转换(仅限F1系列)

当ADC_CR2寄存器的ADON位为1时,再单独给ADON位写1,只能启动规则组转换

(2)外部事件触发转换

外部事件触发转换分为:规则组外部触发和注入组外部触发

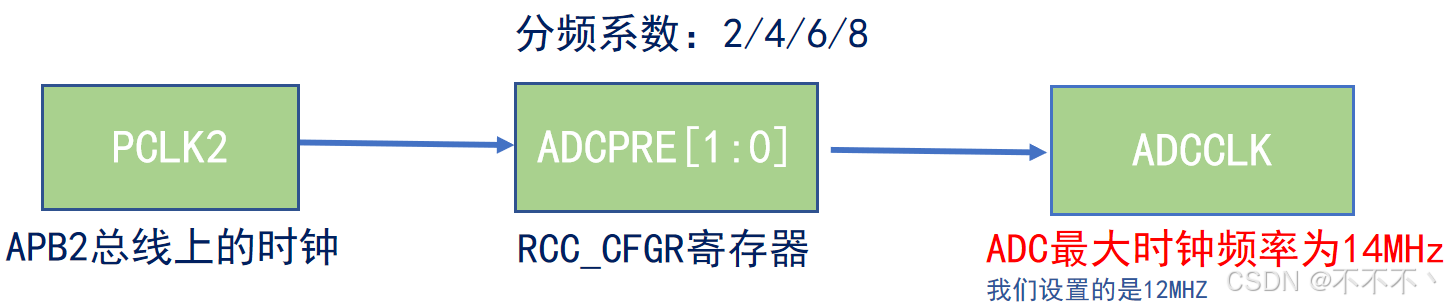

转换时间(F1系列)

1.设置ADC时钟

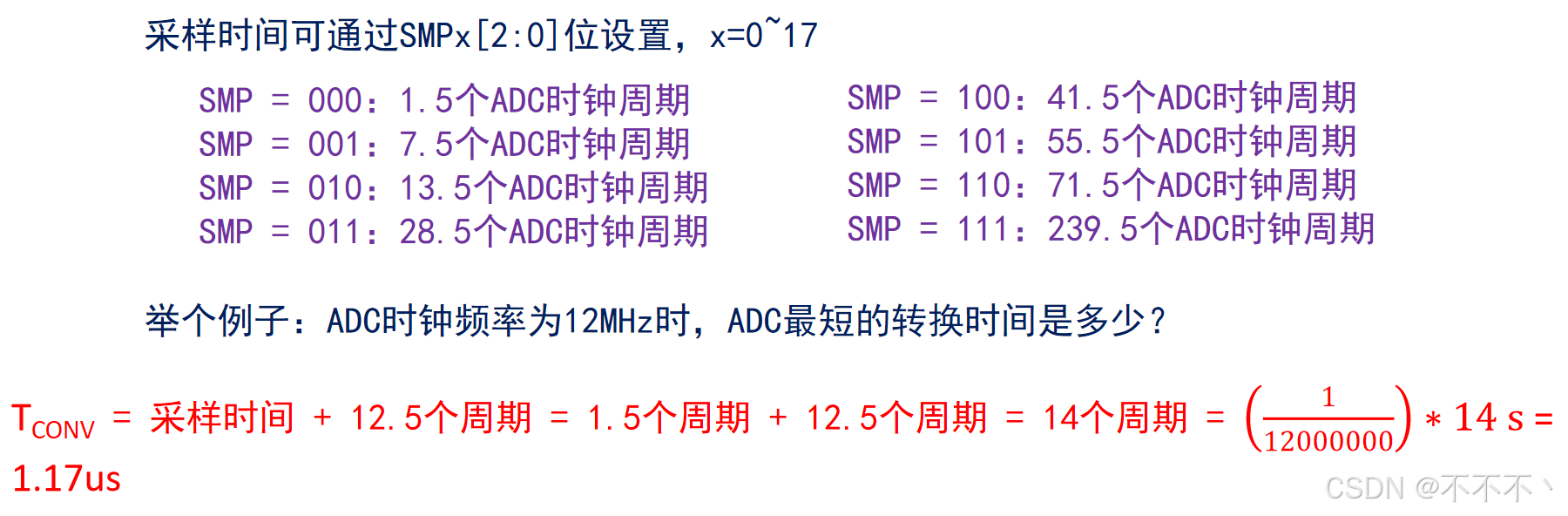

2.设置转换时间

ADC转换时间:T= 采样时间+12.5个周期

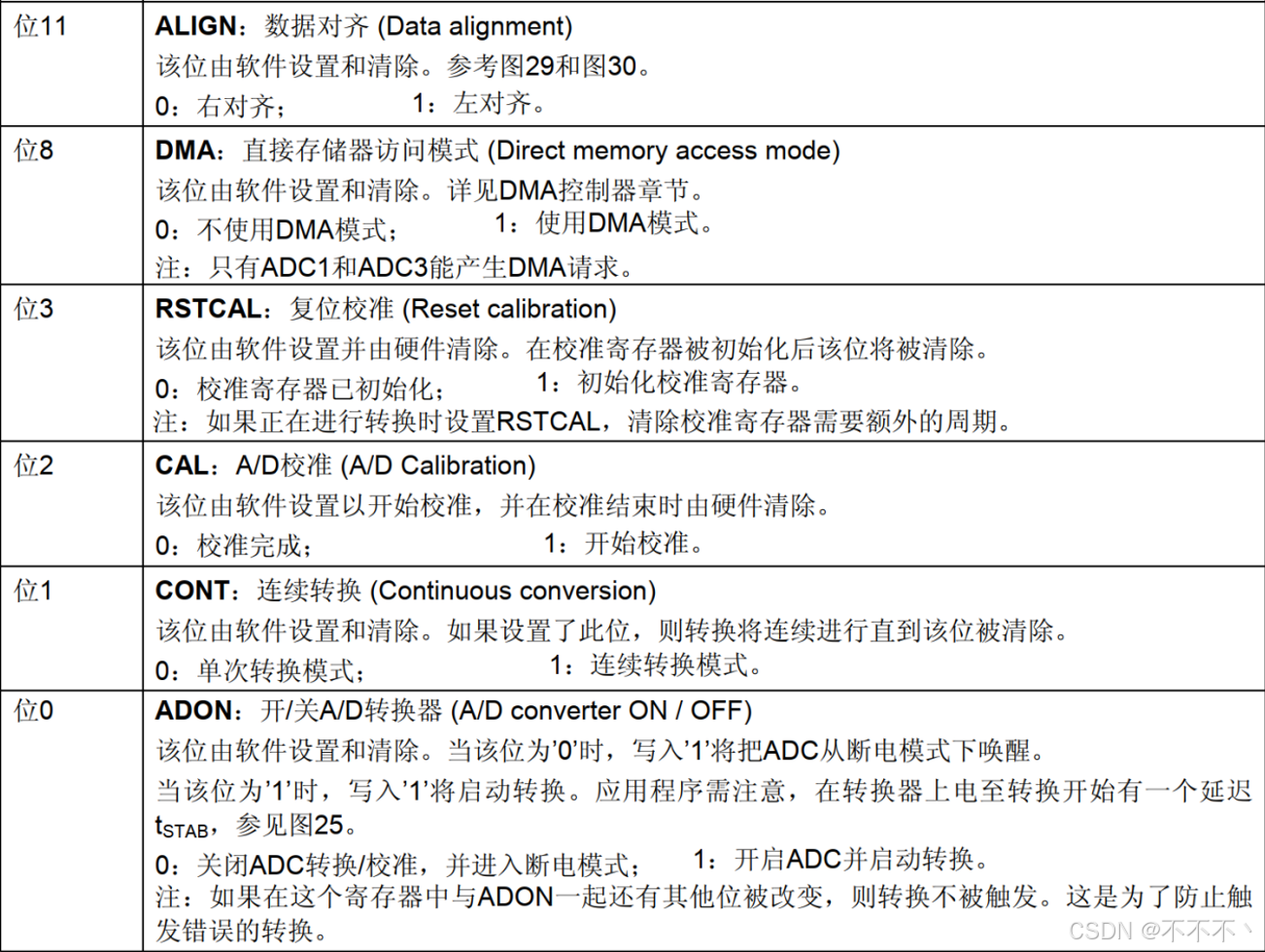

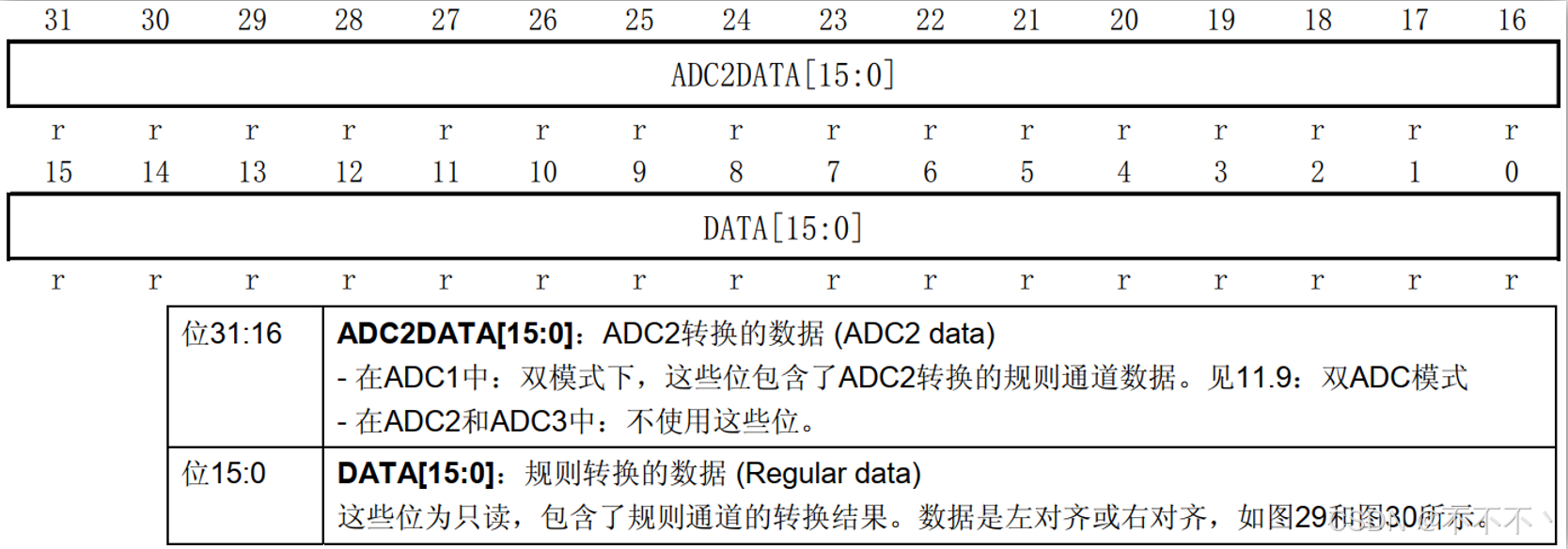

数据寄存器

由ADCx_CR2寄存器的ALIGN位设置数据对齐方式,可选择:右对齐或者左对齐

注意:

ADC 规则数据寄存器只有一个,如果使用多通道转换,那久区能用首时数糖也会存放在DR里面,1按照规则组的顺序,上一个通道转换的数据,会被下一个通道转换的数据覆盖掉,所以当通道转换完成后要及时把数据取走。

比较常用的方法是使用DMA模式。

当规则组的通道转换结束时,就会产生 DMA请求,这样就可以及时把转换的数据搬运到用户指定的目的地址存放。

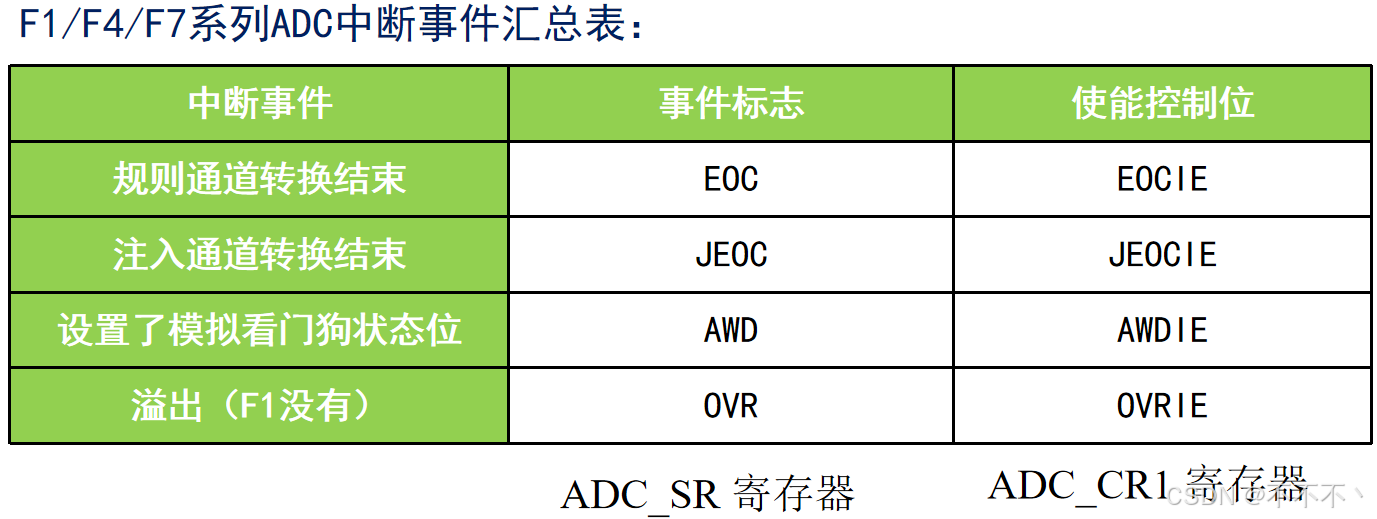

中断

DMA请求(只适用于规则组)

DMA请求(只适用于规则组)

规则组每个通道转换结束后,除了可以产生中断外,还可以产生DMA请求,

我们利用DMA及时把转换好的数据传输到指定的内存里,防止数据被覆盖。

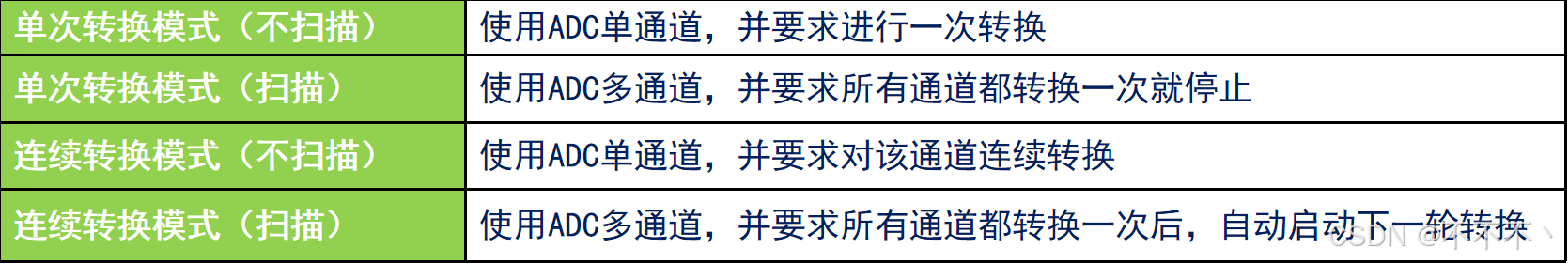

转换模式和扫描模式

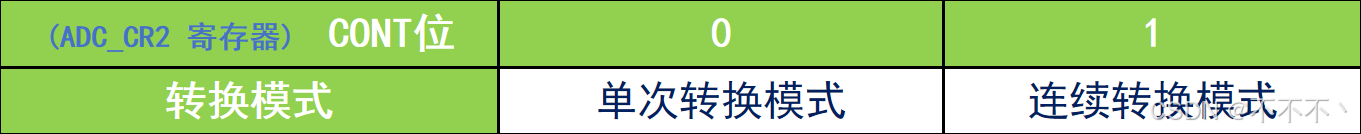

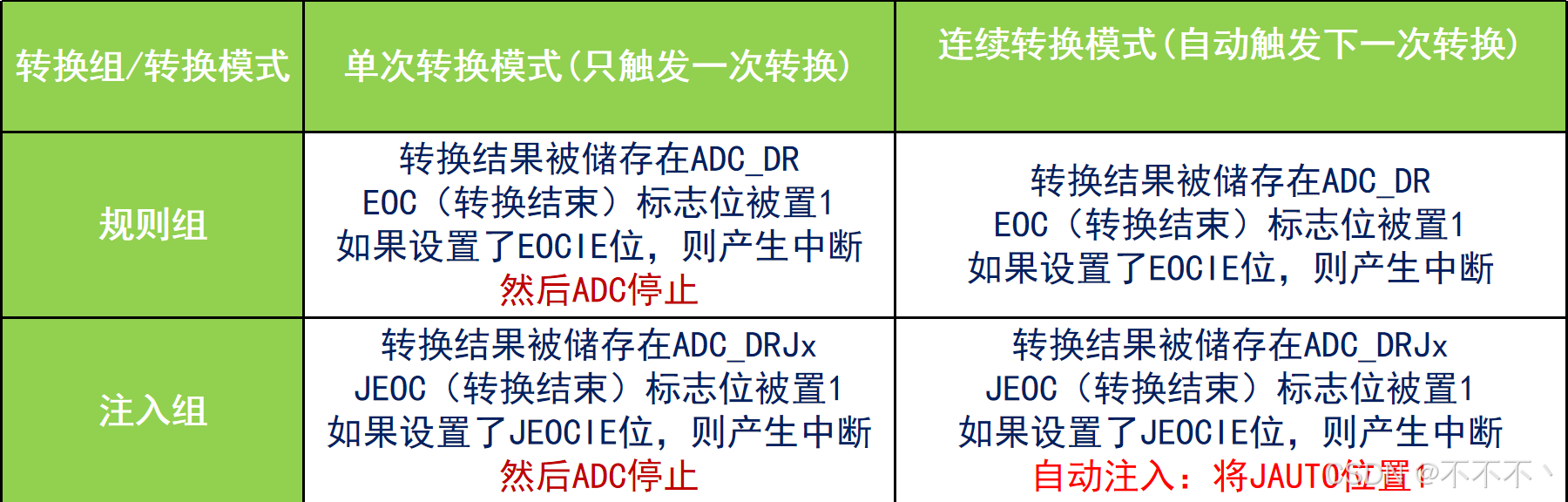

转换模式

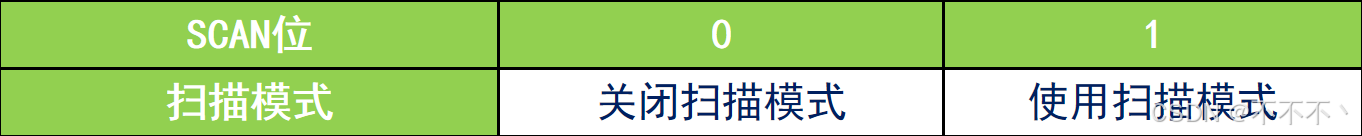

扫描模式

不同组合模式

一种比较少用的模式:不连续采样模式式(F1手册称为:间断模式),只适用在扫描模式下。

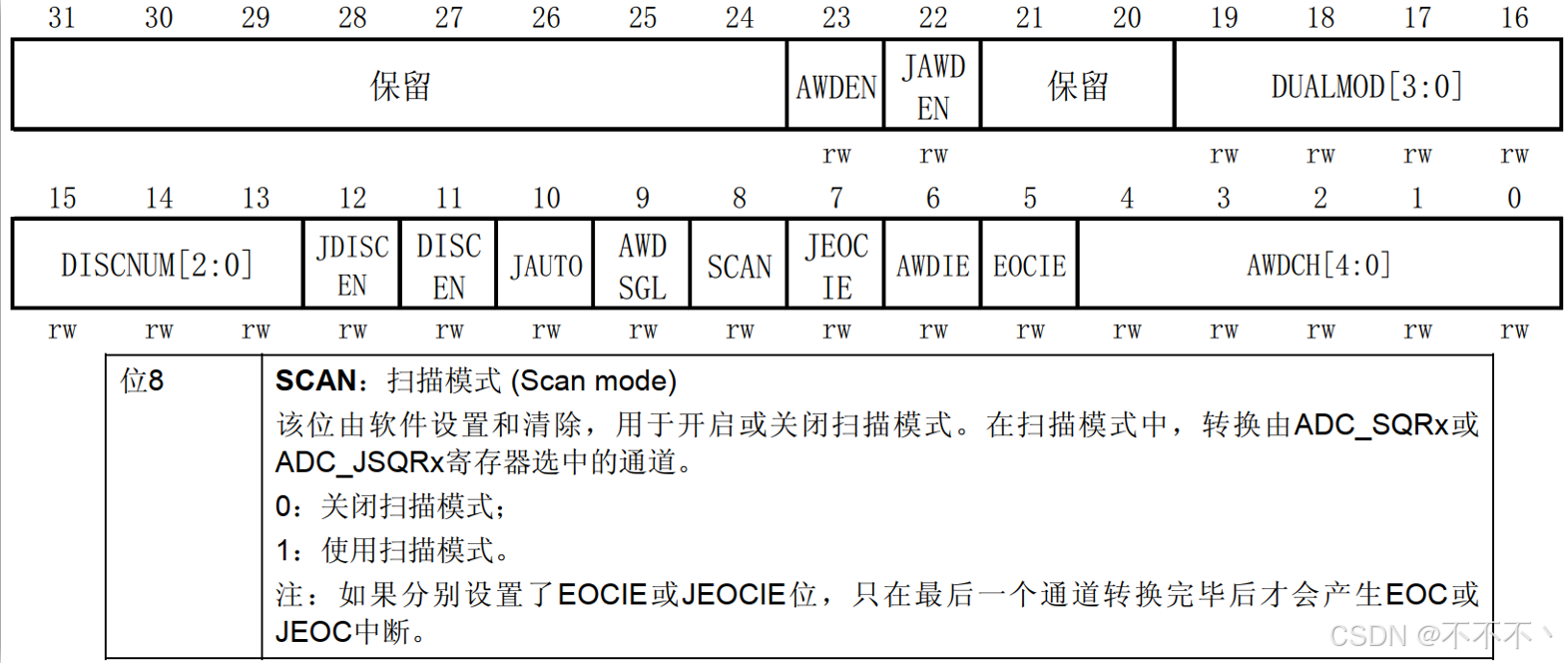

ADC寄存器(F1系列)

ADC控制寄存器 1(ADC_CR1)

ADC控制寄存器 2(ADC_CR2)

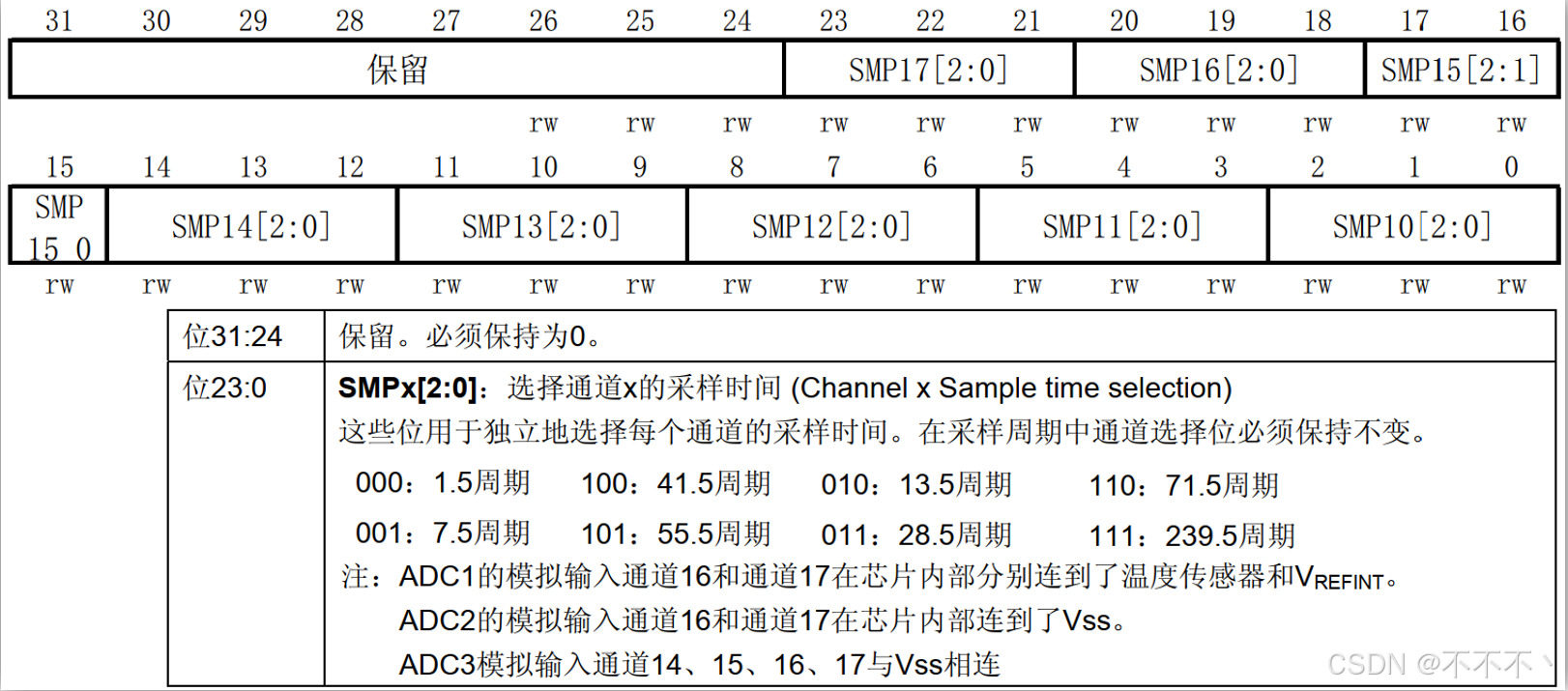

ADC采样时间寄存器1(ADC_SMPR1)

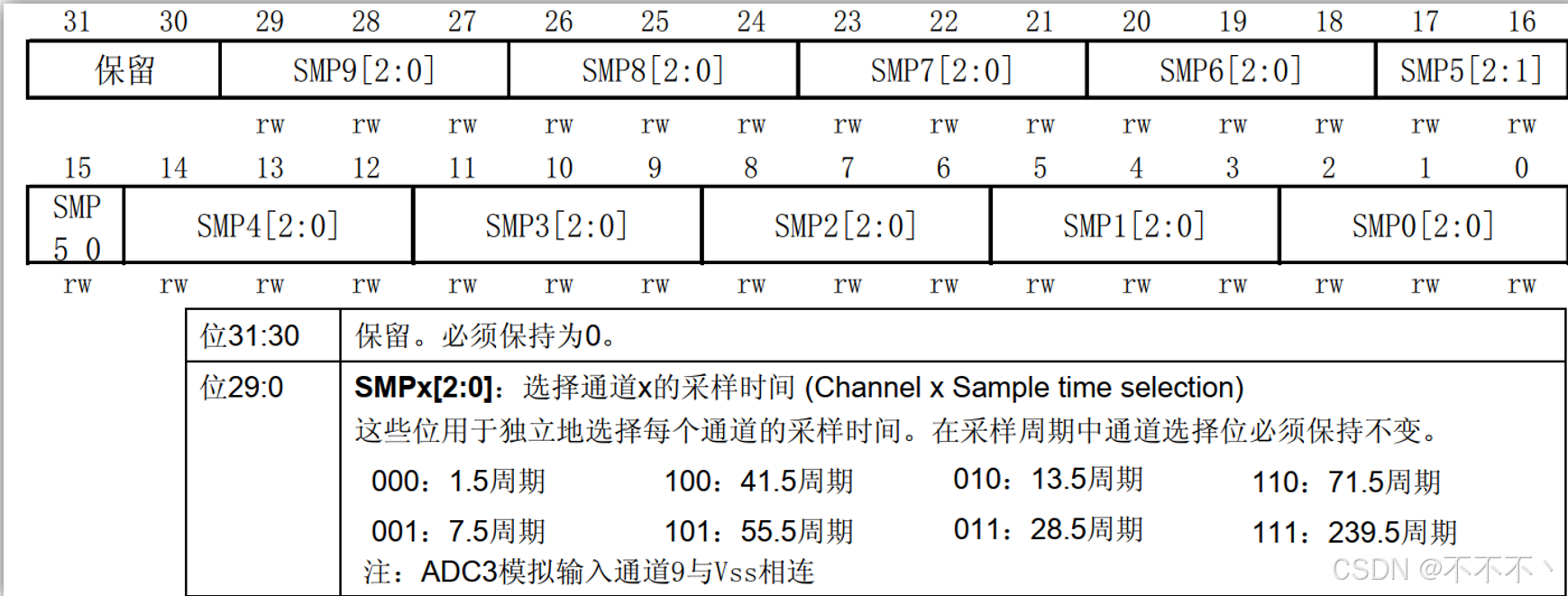

ADC采样时间寄存器2(ADC_SMPR2)

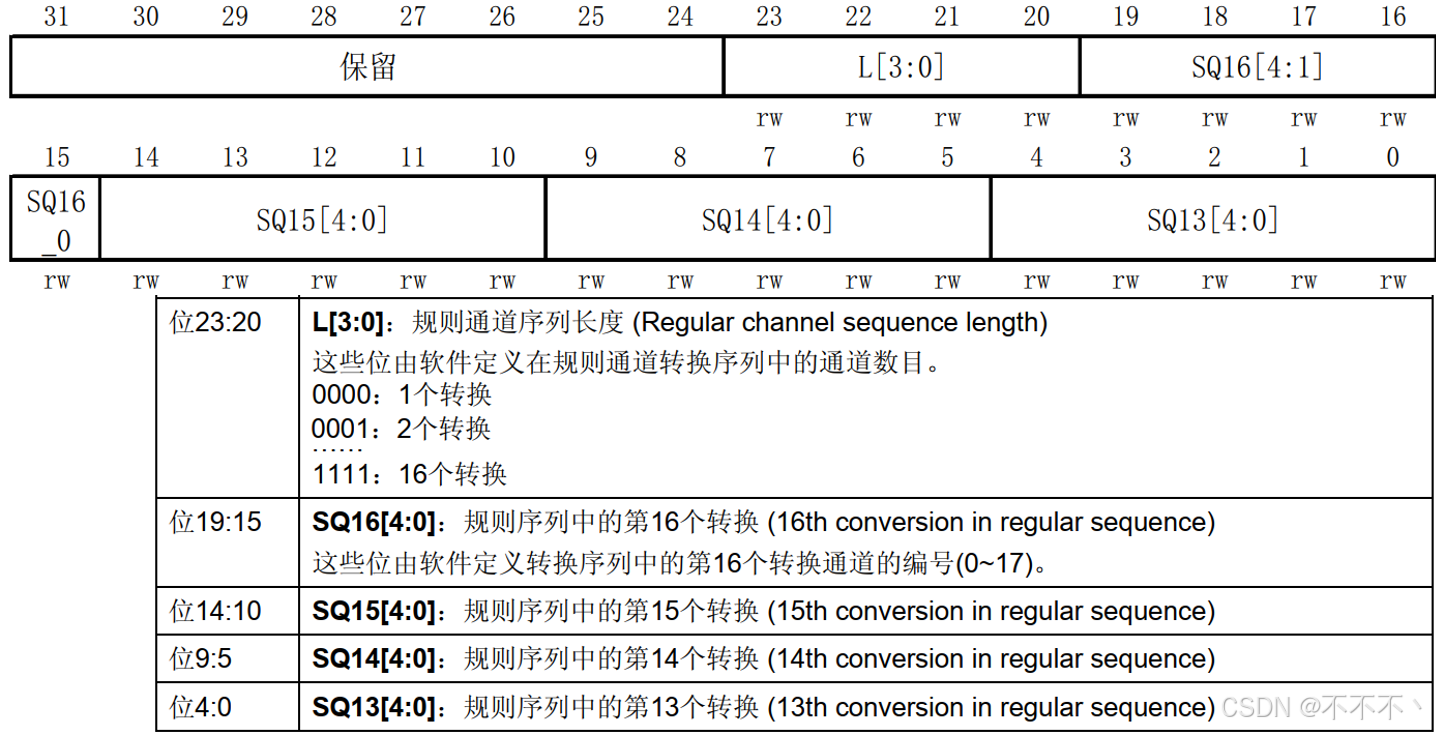

ADC规则序列寄存器 1(ADC_SQR1)

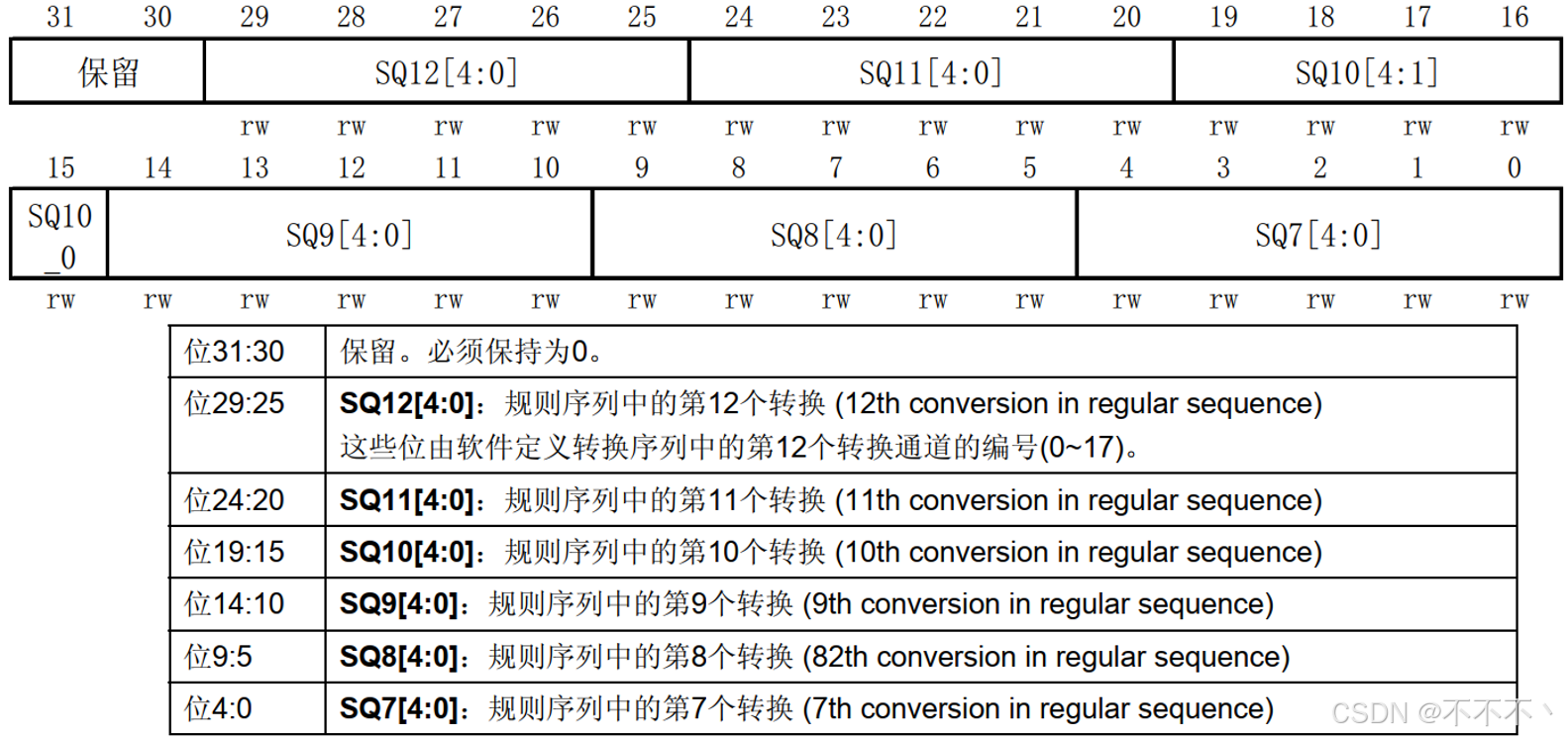

ADC规则序列寄存器 2(ADC_SQR2)

ADC规则序列寄存器 3(ADC_SQR3)

ADC规则数据寄存器 (ADC_DR)

相关HAL库函数介绍