硬件平台搭建1-评估板与上位机

第一阶段,先使用评估板配套的上位机软件进行控制,学习一下各种功能的实现方式和寄存器配置方式。

硬件连接

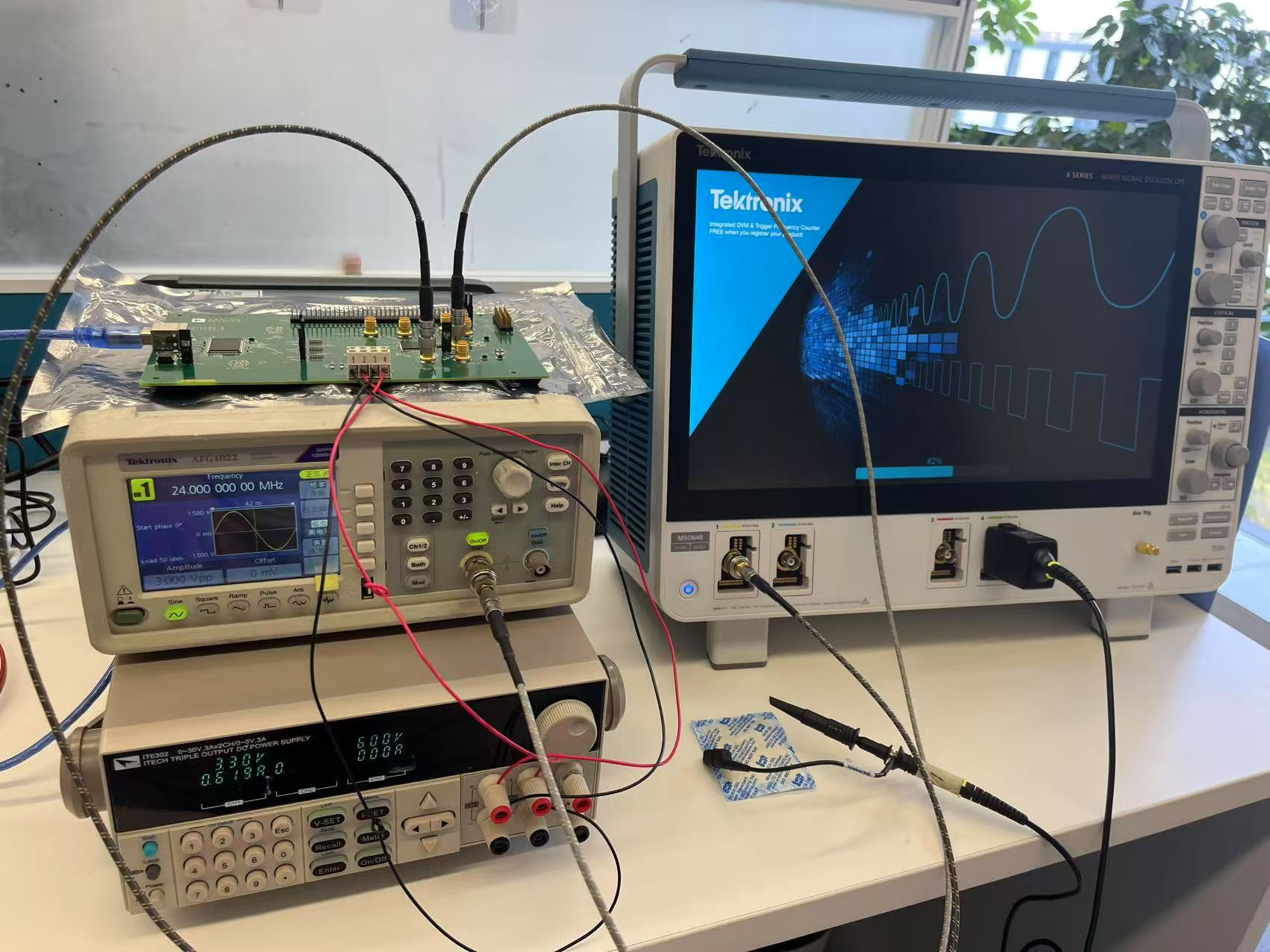

需要的设备仪器包括:多路直流稳压电源、信号发生器、示波器、电脑。

按照图中的方式进行连接:

- 直流稳压电源提供3.3V和1.8V,电流均设置为1A

- 信号发生器提供系统时钟,设置为24MHz,3Vpp

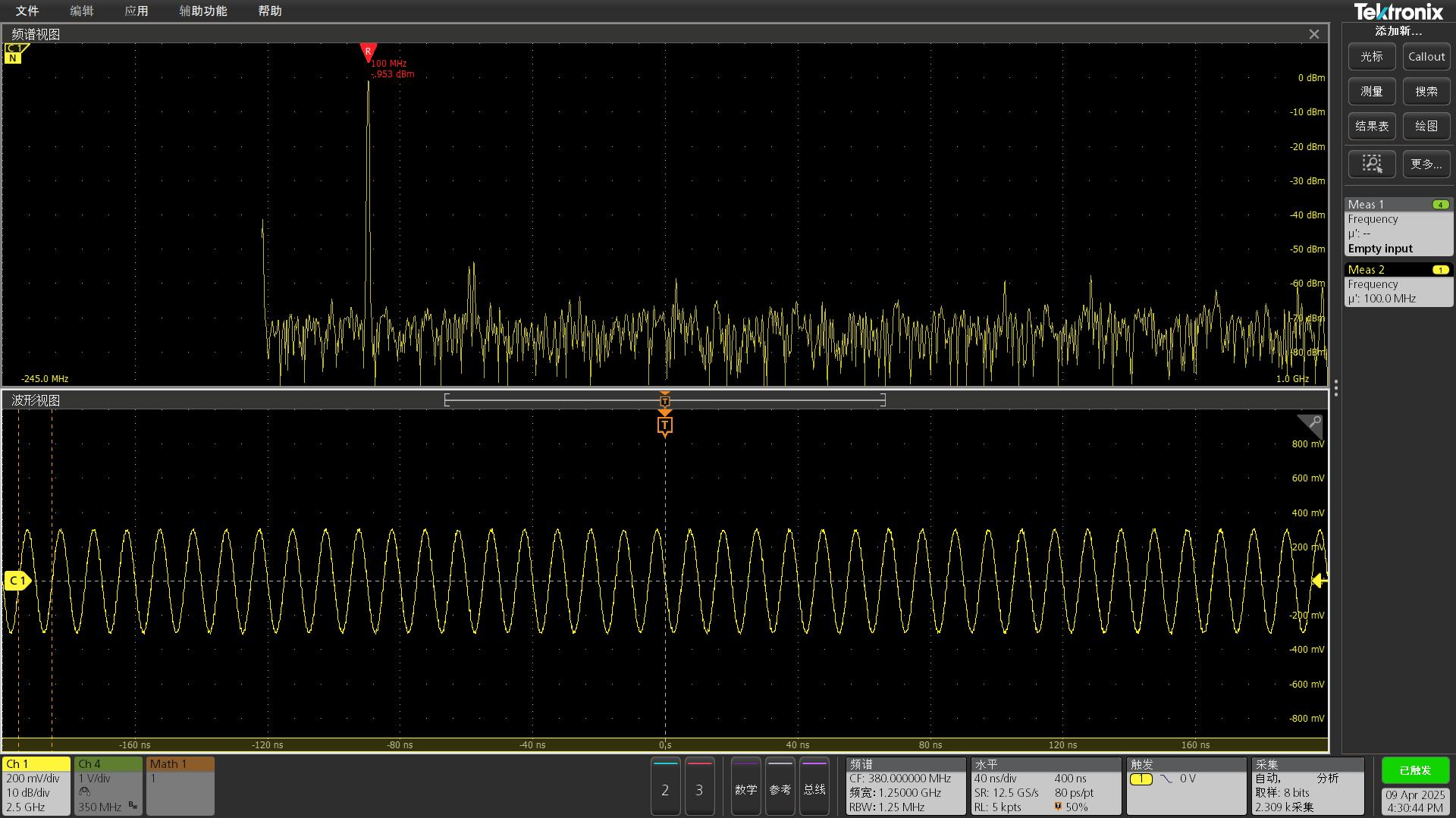

- 示波器查看DAC输出的信号和SYNC_CLK信号

- 电脑通过USB连接评估板,进行配置操作

上位机界面

打开上位机软件,连接评估板后,点击复位

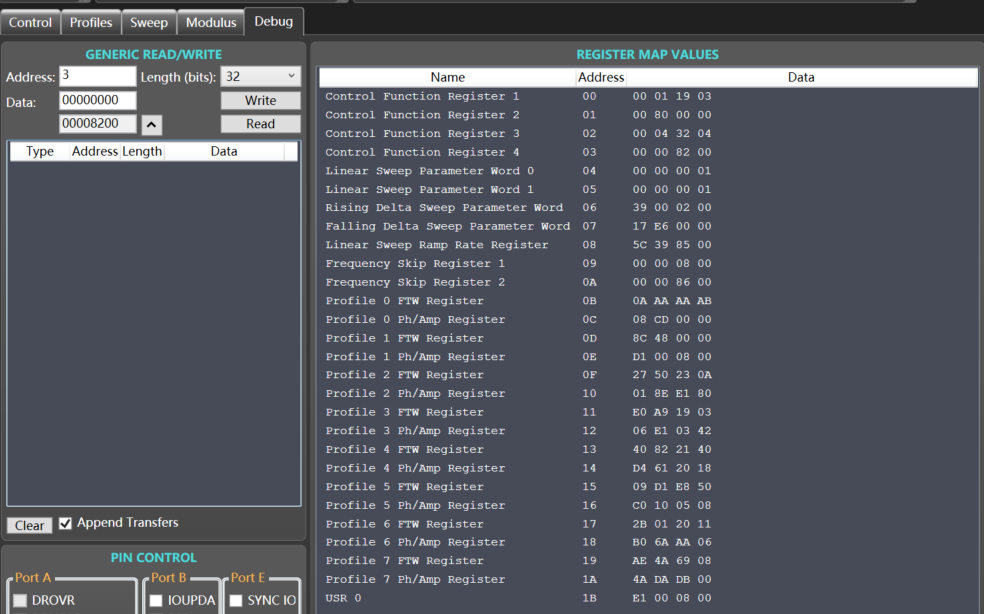

打开PLL使能功能,输入时钟频率及倍频系数

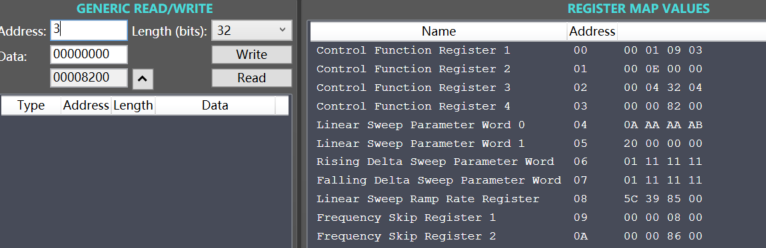

此时的状态,就是一种使用PLL功能的初始状态,再进行FPGA控制时,也需要确保读回的所有寄存器的值与初始状态的值相同。

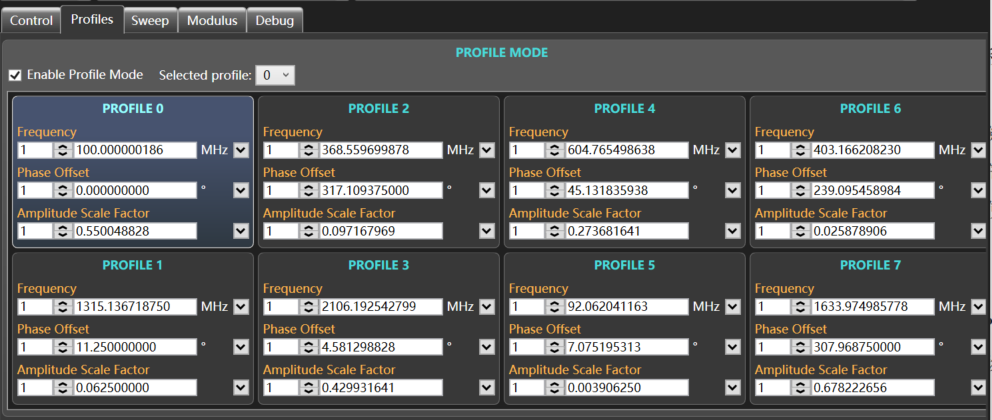

单频功能

使用Profile功能实现。

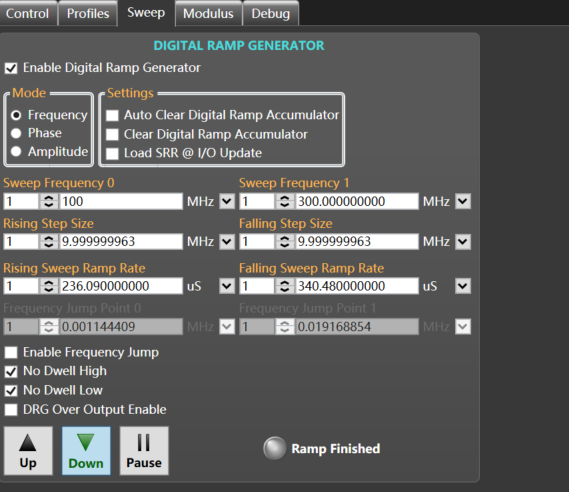

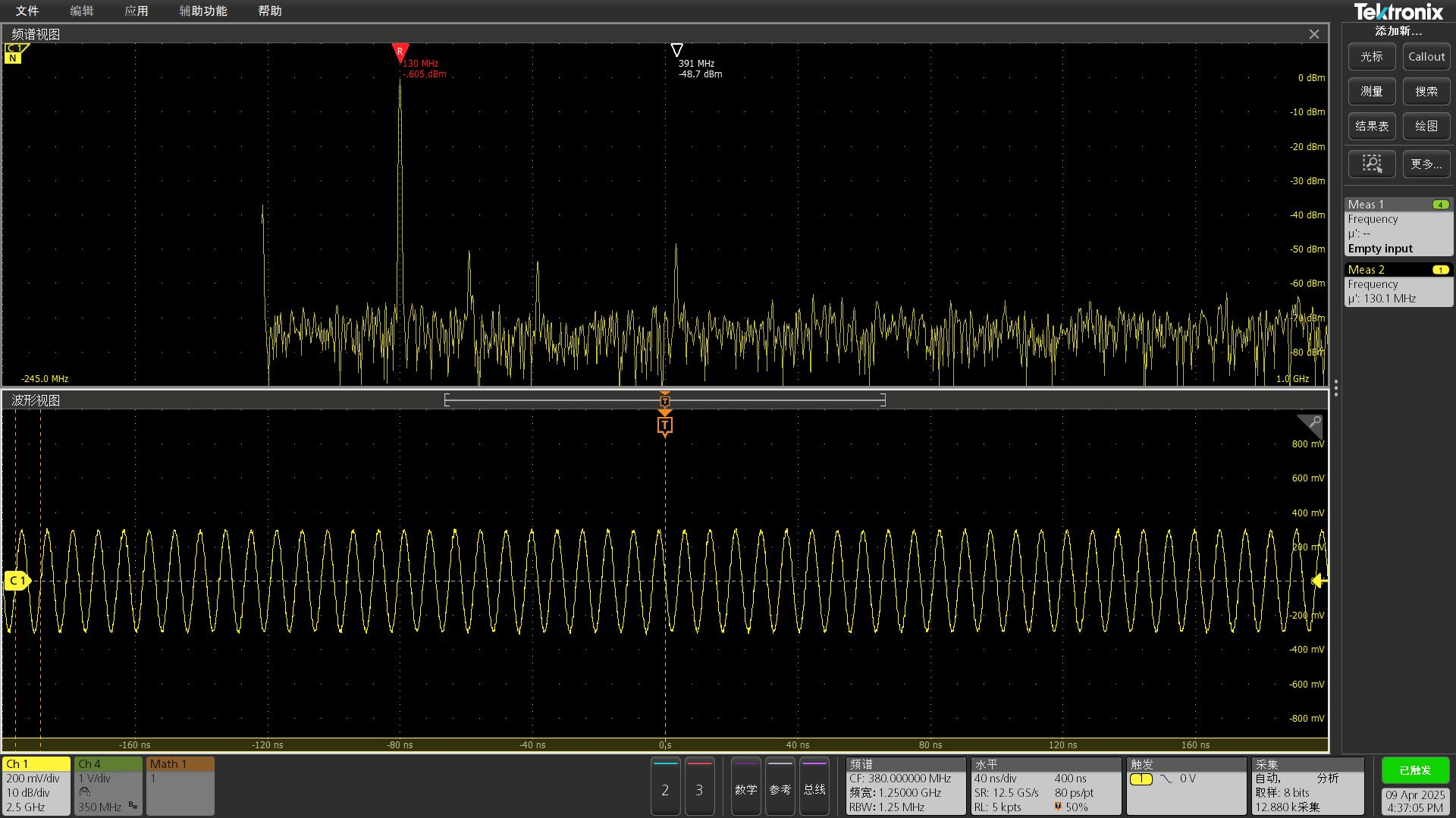

扫频功能

下一步就搭建FPGA与评估板的平台。