提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

前言

这是对B站傅里叶的猫视频时钟约束的笔记

一、主时钟约束

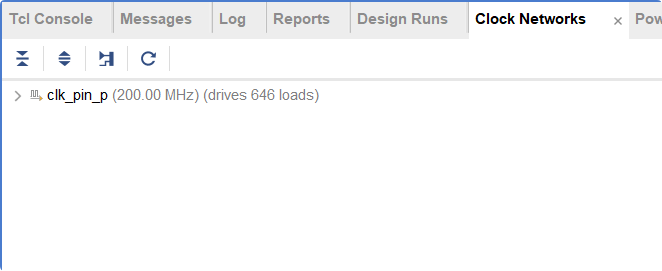

report_clock_networks -name main可以显示Vivado识别的主时钟。

可以看出,Vivado会自动设别出两个主时钟,其中clk_pin_p是200MHz,这个是直接输入到了MMCM中,因此会自动约束;另一个输入时钟clk_in2没有约束,需要我们手动进行约束。

但是我这里没有两个时钟,应该是up在工程里添加了代码。

MMCM就是 Xilinx(现 AMD)FPGA 中用于时钟生成、调整和管理的专用硬件模块,比传统的 PLL(锁相环)功能更强大,适用于高精度时钟需求。

也可以使用check_timing -override_defaults no_clock命令。

那么如何对主时钟进行约束呢,可以在tcl里输入

create_clock -name clk2 -period 25 [get_ports clk_in2]

对主时钟clk_in2进行约束。

使用tcl命令进行约束后,需要点击run implementation然后进行保存。