**Q:**DE1-SoC_Computer系统的ARM A9处理器和FPGA端I/O怎样进行数据传输?

**A:**DE1-SoC_Computer系统包含了连接FPGA端I/O外设的并行端口,例如LEDR并行端口,该端口通过Lightweight HPS-to-FPGA桥接器映射到地址始于0xFF200000的ARM内存映区域。并行I/O端口以不同的偏移量映射到桥接器的地址空间,任何端口的物理地址是0xFF20000+偏移量。LEDR端口的偏移量为0,物理地址就是0xFF20000+0x0=0xFF200000。LEDR并行端口寄存器接口只有data寄存器,对该寄存器进行读写即可控制LEDR的状态(亮与熄灭)、读取LEDR状态。

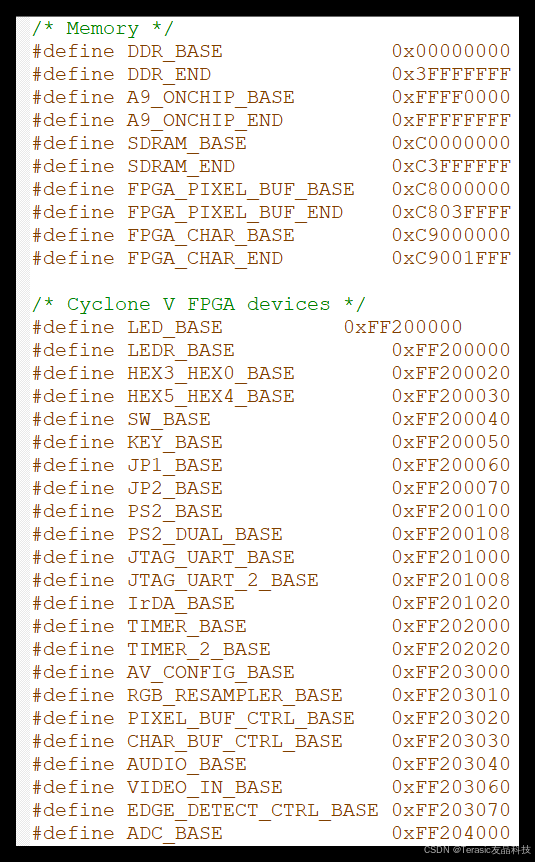

可以参考intelFPGA\18.1\University_Program\Computer_Systems\DE1-SoC\DE1-SoC_Computer\doc_ARM里的DE1-SoC_Computer_ARM文档的2.9 Parallel Ports了解更多FPGA I/O外设端口;\DE1-SoC_Computer\software里的address_map_arm.h头文件列出了DE1-SoC Computer系统的内存和FPGA I/O外设的地址。