作者:Hello,Panda

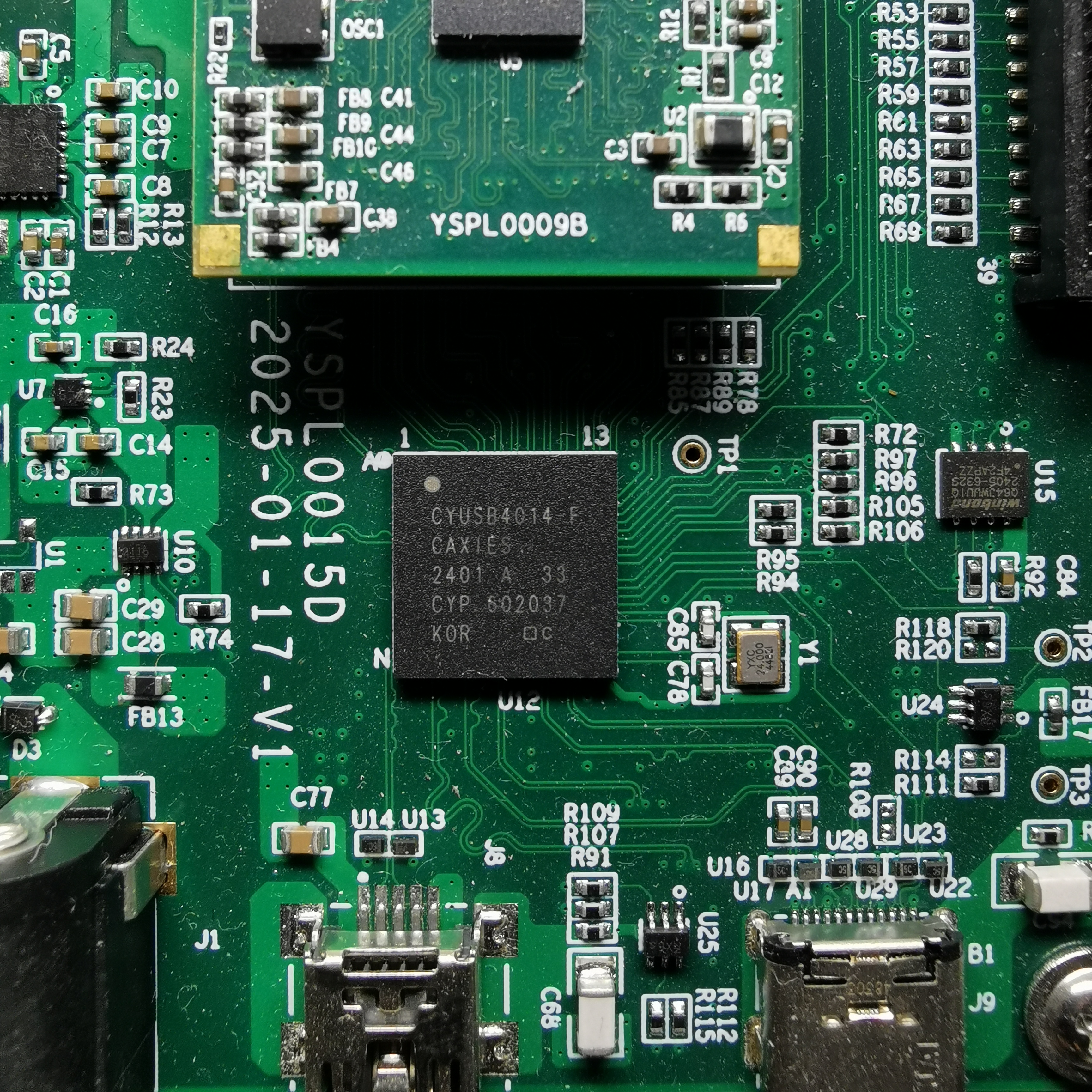

大家早上好,中午好,下午好,晚上好,熊猫君又来了。这次计划做一个连载,大概6期左右,主要介绍英飞凌最新的FX5/10/20的器件应用。目前,熊猫君手上调试的是一个Sensor(IMX586)+Crosslink-NX FPGA(LIFCL-40)+ FX10(CYUSB4014)的一套板子,调试FPGA采集Bayer图像经USB3.2(10Gbps)传输到计算机。

一、器件介绍

因为拿到的是FX10系列的器件,那么介绍就以CYUSB4014为例。(有消息人士传FX5/10/20都是基于同一个Die,熊猫君这里没有得到官方信息,不予置评)。

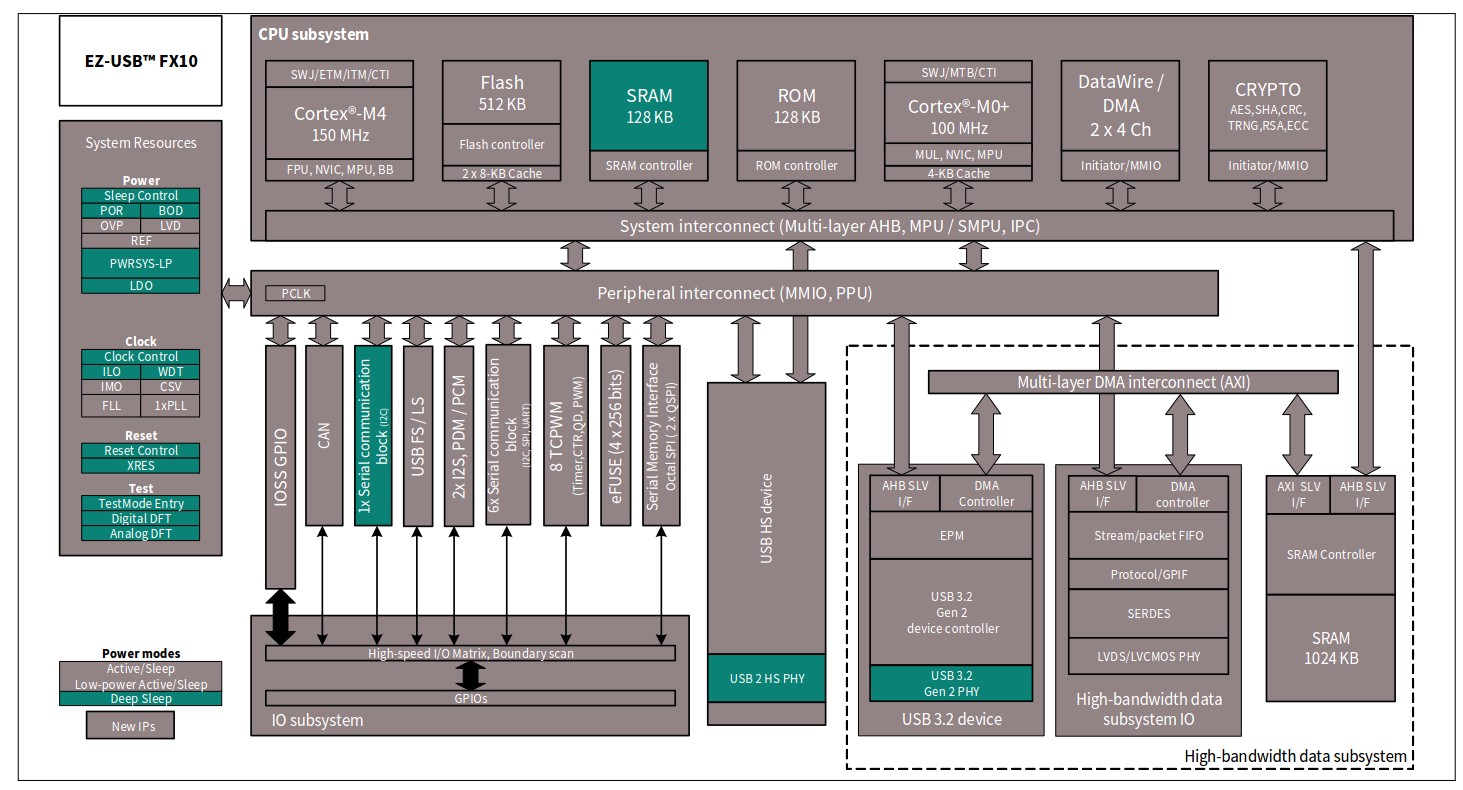

(1)支持USB3.2Gen2,兼容10/5GBps和480Mbps PHY;支持USB Type-C,最高32个USB Endpoint;

(2)SoC内置1个150MHz的Cortex-M4F核和1个100MHz的M0+核;

(3)内部存储资源如下:

a)512KB的应用程序Flash空间,用于存储用户应用程序;

b)128KB SRAM,可以配置为4个32KB区域,在在Deep Sleep模式下,这些区域能够配置为Retain Data模式;

c)128KB ROM,内置ROM Boot启动代码,包含设备初始化、写Flash、安全、eFuse编程和其他系统级的函数功能。ROM代码由CM0+ CPU执行;

d)1MB数据缓存SRAM,用做LVSD/LVCMOS到USB的数据缓冲区;

e)1024位的OTP eFuse,其中648bit用于存储系统的Die ID、设备ID、初始化的Trim设置、设备生命周期和安全设置等。其它区域用于存储秘钥、hash值、unique ID等等。在编程eFuse时,VDDD必须是2.5V。

(4)GPIF III接口

支持LVDS/SubLVDS和LVCMOS两种类型的接口输入:

a)两组LVDS接口,每组由8对数据、1对时钟、1对控制和7根单端LVCMOS控制信号构成,两组可合并为16对数据的链路使用。最高LVDS速率为1.25Gbps/Lane(FX10是接收端时);

b)两个port,每个port由16根数据线,1个时钟和10根控制线构成,2个port可合并为32bit的数据总线,FX10是接收端时,可支持最高160MHz的DDR/SDR数据,是发送端时,最高100MHz。

(5)外设

支持最高48个GPIO:可用作QSPI,7个可配置的I2C、UART或SPI接口,2通道音频接口(I2S或PDM转PCM),一个全速USB2.0 FS用于VCOM通信,8个PWM输出和1个CAN FD接口。

(6)时钟资源

内置了8MHz振荡器,32KHz振荡器,可接入24MHz的外部晶振;内置PLL和FLL,多个时钟分频器。

(7)加密与安全

支持"Secure Boot",仅允许可执行(execute-only)的代码安全模式,秘钥和TRNG功能。

(8)封装:BGA-169 Ball,10×10mm,0.75mm球间距。

下图是FX10的体系架构框图。

图1 FX10 架构框图

二、硬件设计

硬件设计主要考虑供电、启动和接口,PCB Layout时重点考虑信号完整性。本例中将FX10的输入接口设计为LVDS以减少IO使用量。

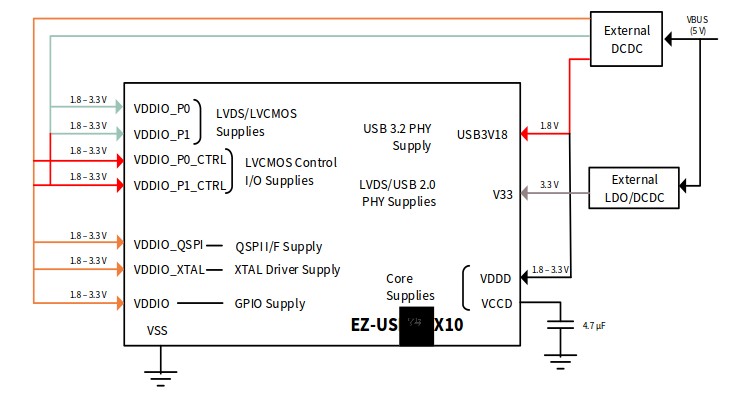

(1)供电设计

如下图2所示是FX10的供电系统:

图2 FX10 供电系统

设计电源系统的两大要点:其一是必须满足功能性能要求,其二是将系统功耗降到最低。将系统功耗降低有两层考虑,一层是使用效率高的电源芯片,第二层就是使FX10工作在最佳最省电的状态。从数据手册上可以看到,在内核电压VDDD工作在1.8V使,能效比最高,因此,各路电轨可设计如下:

a)VDDD:内核供电,设计为1.8V。但需要注意的是,在编程efuse时,需要配置为2.5V;

b) VCCD:FX10内部转换器,将VDDD变为1.1V电压,外接退耦电容即可;

c)VDDIO_X:给外设IO供电,全部设计为1.8V;

d)USB3V18:给USB3.2物理层供电,1.8V;

e)V33:给USB2 HS PHY供电,3.3V;

f)VDDIO_P0/1:LVDS/LVCMOS接口模块,因为选择的是LVDS接口,该处必须使用3.3V供电;

g)VDDIO_Px_CTRL:单端控制信号供电,选择1.8V。

由上可知:需要3.3V、2.5V和1.8V三组供电,如无需使用efuse功能或3.3V为可在线编程电源,则只需3.3V和1.8V两组供电即可。

(2)启动模式

BOOT模式通过GPIO PMODE_13.0选择,该IO低电平时从内部Flash启动,高电平时从USB启动。

(3)Layout设计

FX10器件Layout设计请参见官方文档AN238422《EZ-USB FX5/FX10 hardware design Guidelines and schematic checklist》。

三、开发环境

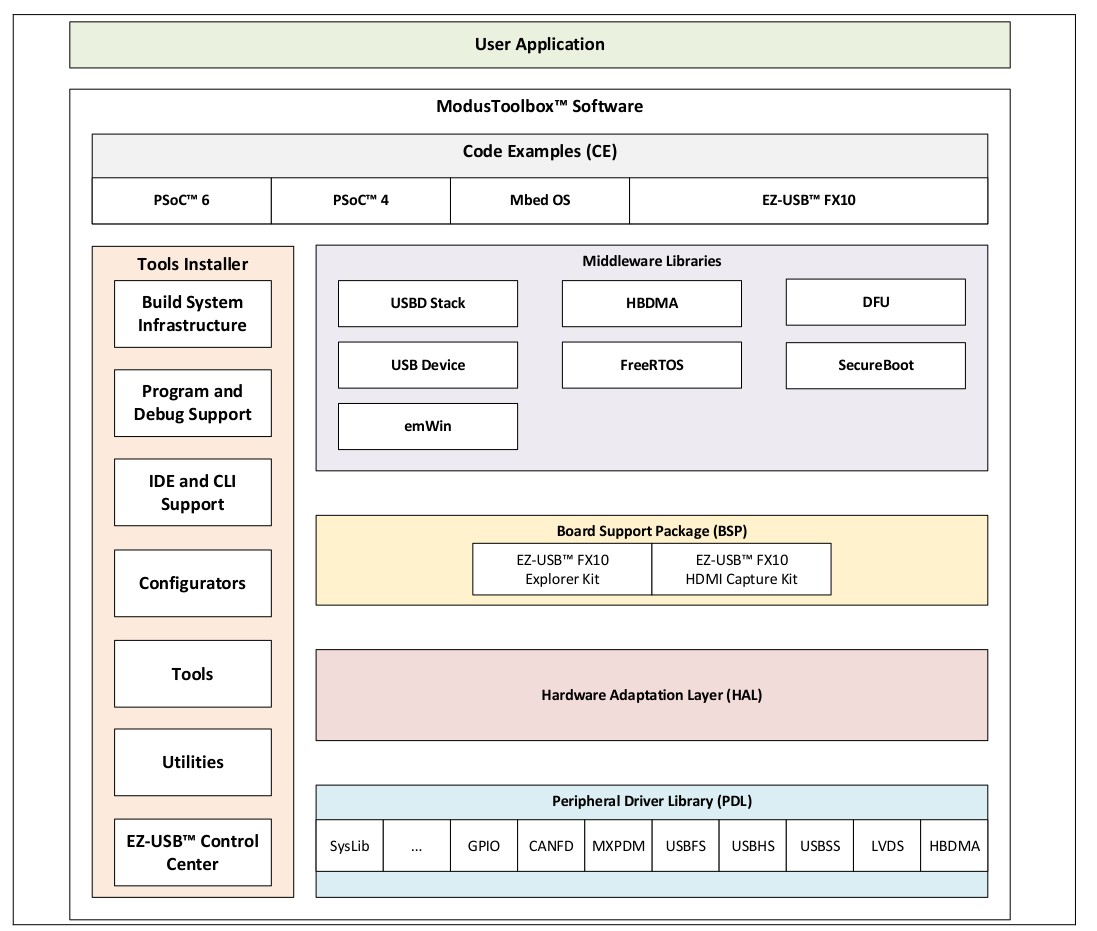

(1)开发环境和编译器

FX10 SoC端开发环境使用Modus ToolBox交叉环境+Visual Studio Code IDE(或IAR、ARM MDK等)编译器实现。官方提供的SDK基于FreeRTOS(当前基于内核版本version 10.4.6),SDK提供外设驱动库、LVDS IP驱动、USB协议栈和DMA管理等等。

官方提供了若干个例程,包括UAC、UVC、USB3 Vision等音视频流协议,使用LVCMOS接口的Slave FIFO协议等。用户可以基于例程修改开发自己的应用。需要特别注意的是Slave FIFO例程仅支持LVCMOS接口输入。

根据所选的编译器IDE,可以支持GUN、ARMCC或IAR。建议用户选择自己熟悉的IDE和编译工具链。官方给的例程是基于Modus ToolBox 3.1.0及以上版本+Visual Studio Code IDE+OpenOCD KitProg3调试。

下图3是Modus ToolBox支持EZ-USB FX10开发框架。

图3 ModusToolbox For EZ-USB FX10

(2)在线调试

在线调试支持SWD接口和JTAG接口。FX10支持OpenOCD和GDB调试协议,对应的调试器分别是KitProg3和Segger J-Link。所有的官方开发套件都搭载KitProg3调试器,这个调试器原厂的1千多,第三方贰佰来块。对国内用户而言,似乎更加熟悉J-LINK。

(3)计算机端

与上一代的CyUSB3014类似,提供了一个EZ-USB Control Center实现一些基本的功能,如编程、查看设备信息。UVC、U3V等协议可以直接使用第三方工具播放,Slave FIFO也是老办法,自己写客户端软件接收数据和解析、保存、播放。

好了,今天算是起了个头。对FX10的器件特点、硬件设计和开发调试环境的搭建做了一个简要介绍。下一期是修改、编译和调试SDK软件的内容。各位晚安。Good Night。