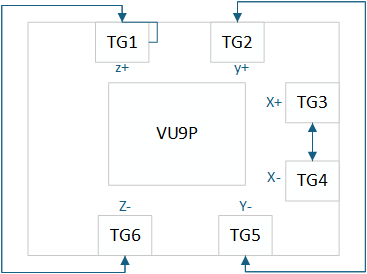

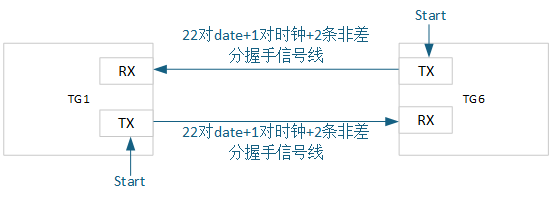

本次实验的目的是通过VU9P开发板的6个TG接口,采用固定连接的方式,即X+和X-维度互联,其框图如下所示:

IP参数配置

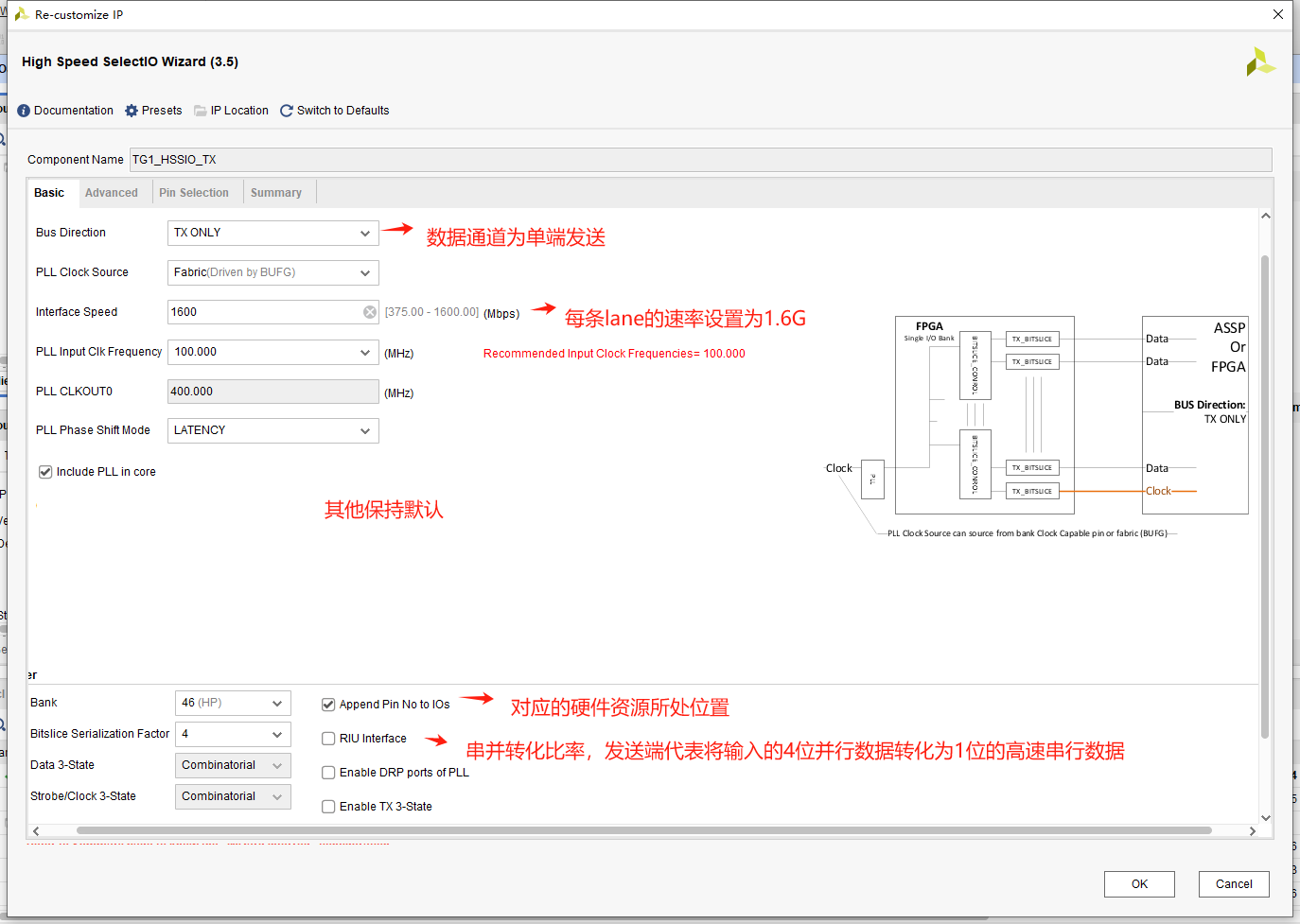

通过调用High Speed SelectIO Wizard来实现数据通路,High Speed SelectIO Wizard ip有24对数据通道,且其数据通路方向(BUS Direction)可以是 单向发送(TX ONLY),单向接受(RX ONLY),双向分时复用(BIDIR),独立收发(TX + RX),由于一个TG接口由48对LVDS lane 组成,其中24对用于发送数据,24对用于接收数据,所以本次实验将例化两个High Speed SelectIO Wizard分别用于发送和接受,因此一个IP的数据通路方向为单向发送,另一个为单向接收。

TX模块配置

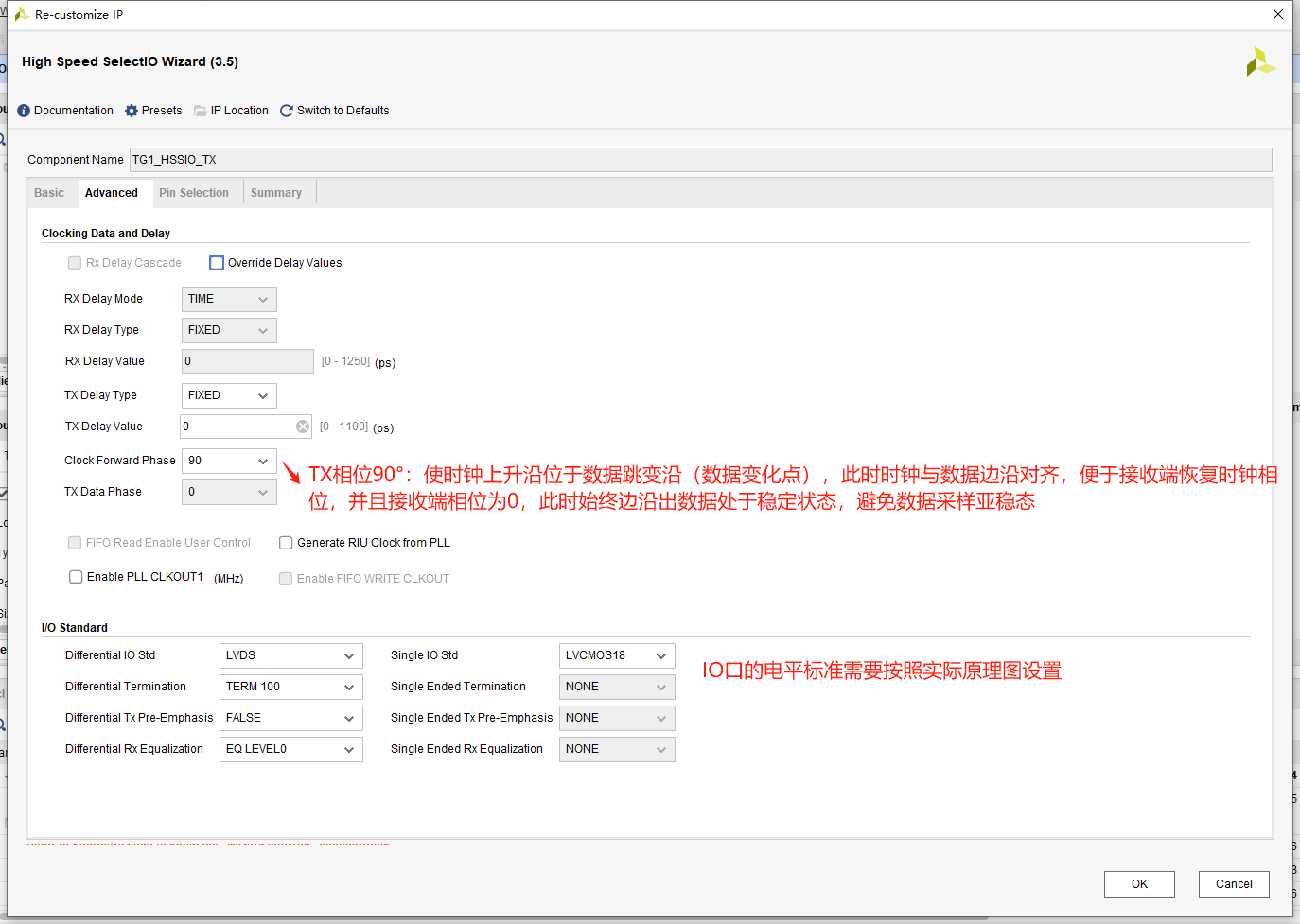

要求单条lane的速率跑到最高1600Mbps,即1.6G bps,因此其IP的TX模块基本配置如下:

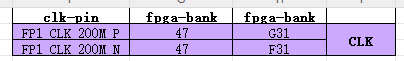

而对于Pin Selection部分的参数配置,需注意以下几个点:

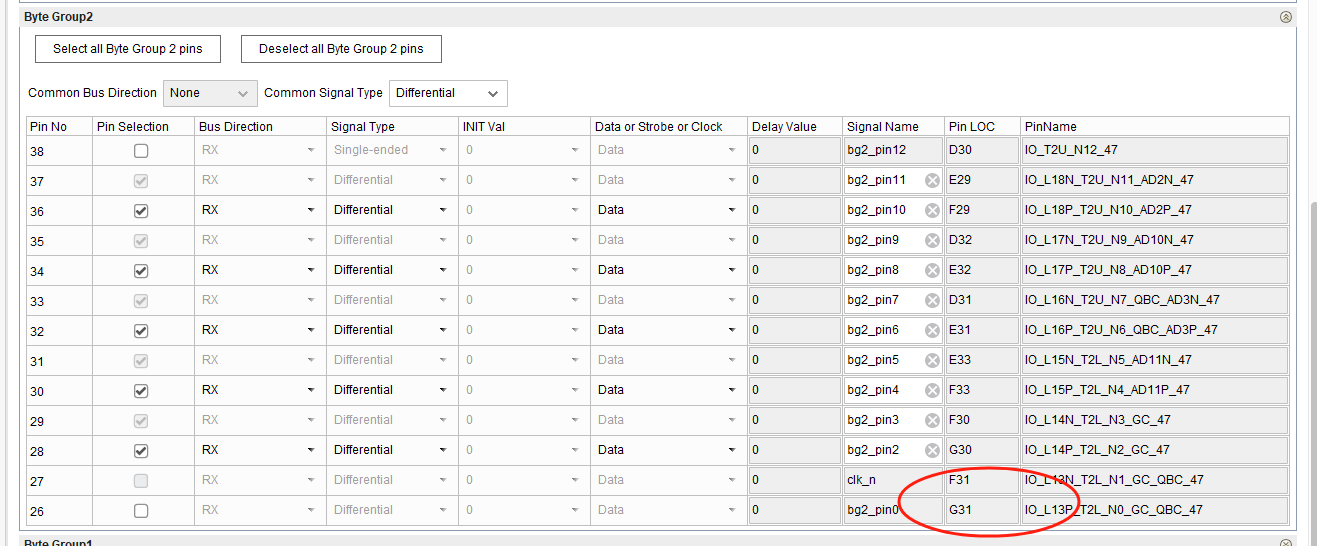

对于ip的24对LVDS lane,需要选择一对lane作为时钟通道,而由于引脚G31,F31是一对差分时钟引脚,不能作为数据通道,也不能作为ip的时钟通道,所以对于某个该引脚对所在的TG不能使用这一对lane,那么其数据通道就只能使用22对。为方便其他TG使用同一逻辑,那么都只使用22对数据lane,一对时钟lane。

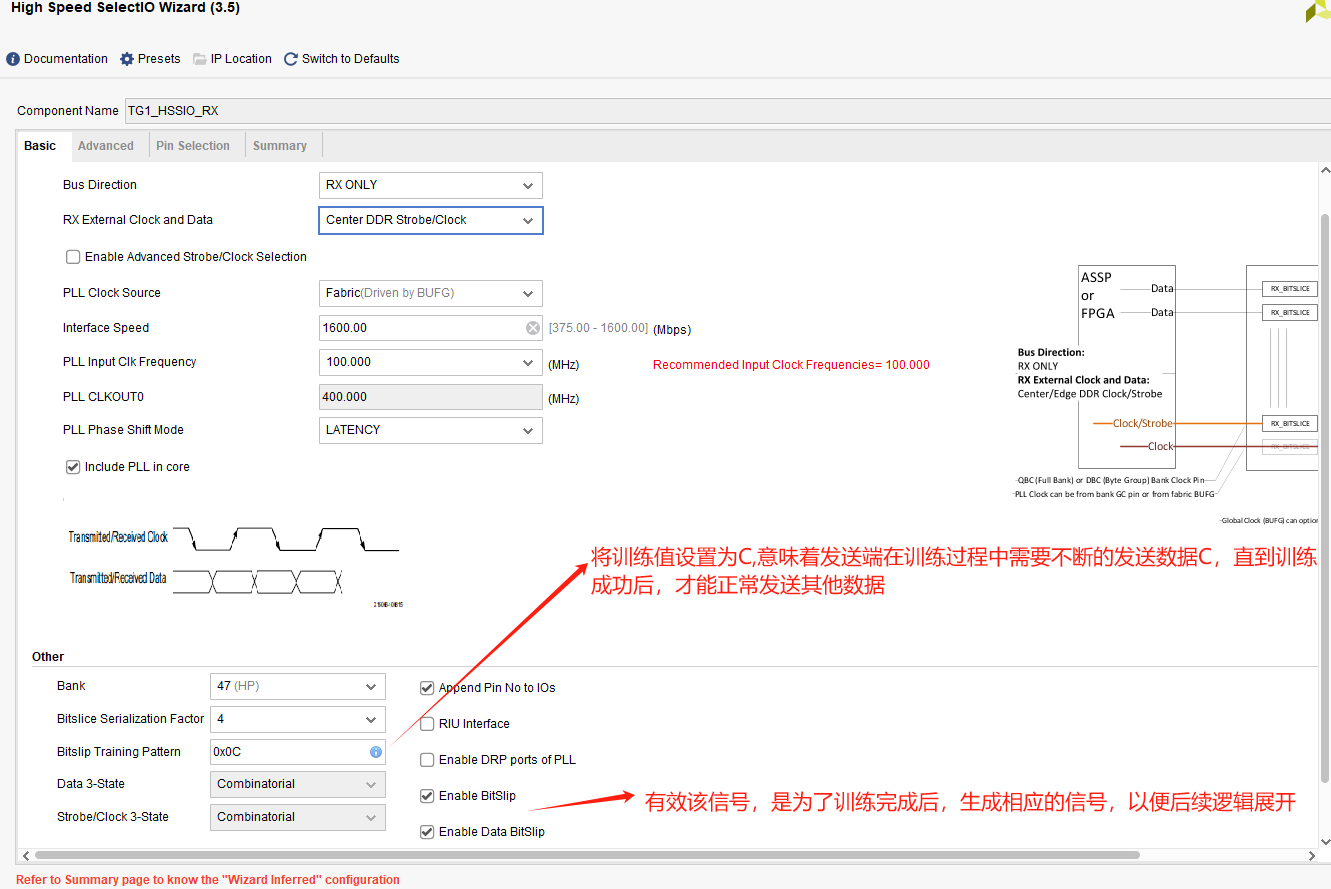

虽然G31所在的lane并没有勾选,但是ip生成后,还是会生成一个特殊的信号,bg2_pin0_nc,需要将这个信号例化到顶层文件中,并且需要将引脚绑上,如此才能正确编译。

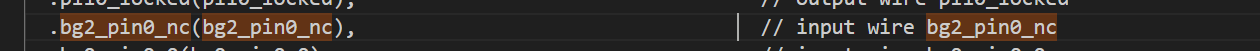

RX模块配置之前,需要先了解一个itslip Training Pattern的原理,并了解其训练原理。在Xilinx High Speed SelectIO Wizard IP中,当配置为RX ONLY模式时,Bitslip Training Pattern参数用于接收端的数据边界校准,其核心作用是通过预定义的比特序列实现串行数据到并行数据的精确对齐。以下是详细解析:

Bitslip Training Pattern的作用原理

-

解决相位不确定性

在高速串行接口中,接收端(RX)需将串行数据流转换为并行数据,但初始采样相位可能未对齐数据边界(如8:1解串时,1位偏移会导致整个字节错位)。Bitslip机制通过移位操作逐步调整数据边界,直至检测到预置的Training Pattern(训练序列)表明对齐成功。

-

校准流程

-

步骤1:发送端(TX)连续发送固定的训练序列(如

0x0C)。 -

步骤2:接收端对并行输出数据应用

BITSLIP脉冲,每次移位1位(SDR模式)或按DDR模式交替移位。 -

步骤3:当接收数据与预设的

Bitslip Training Pattern匹配时,停止移位并锁定边界。

-

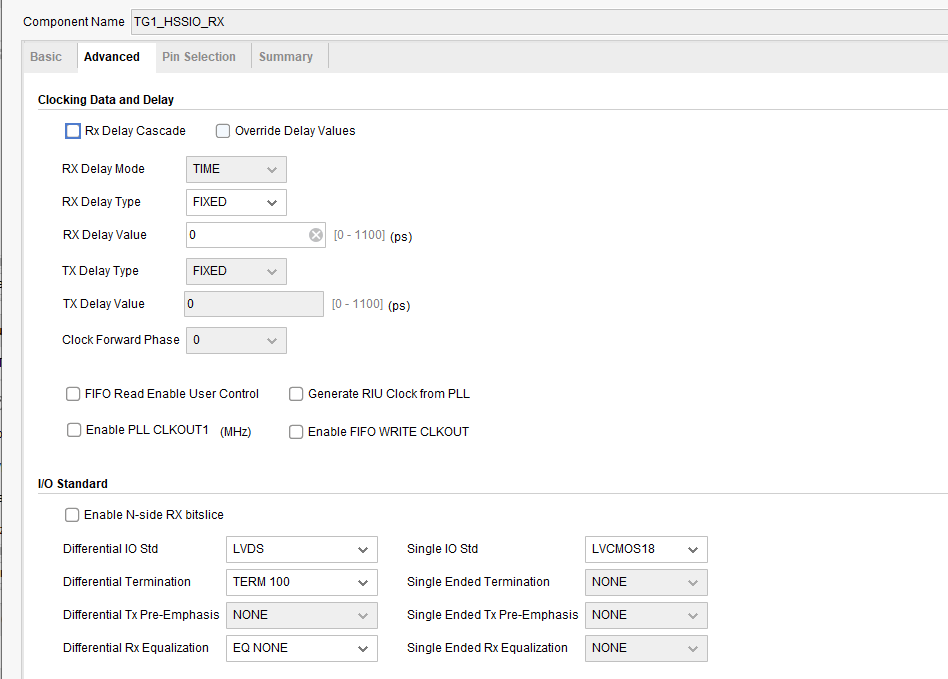

RX模块配置

Advanced界面配置其他默认,电平配置跟随开发板实际情况配置:

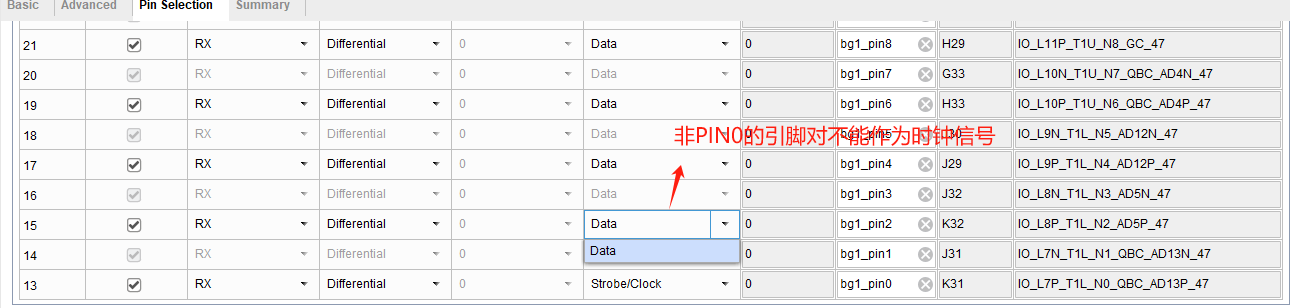

而在配置Pin seltion界面时,需注意一点,其时钟信号只能是选择每一个Group的PIN0位置的一对lane,所以对于时钟信号的选择,推荐先对RX的ip进行设置,然后根据原理图找到TX实际与之相连的IO所对应的lane作为时钟信号。如下图所示:

其他中间的信号有些可选为时钟信号,但是编译会报错。

设计方案

整体设计方案:

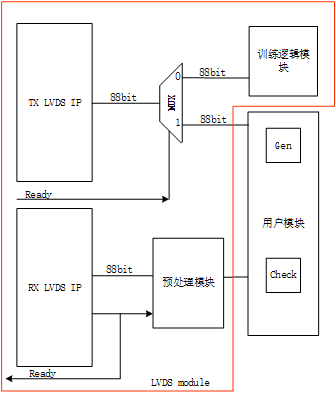

下面是LVDS_module部分的框图:

上图展示的是一条LVDS通路中的信号构成,其中22对data差分信号线用于传递数据,1对时钟差分信号线,加上两条非差分信号线用于传递握手信号。

start信号:通过vio控制,其用于TX复位标识,便于人为控制训练的开始。

对于握手信号的解释:

flag_to_rx :发送模块生成,传递到接收模块,其定义为:当发送模块的初始化序列完成标志rst_seq_done为1后,flag_to_rx 为1,发送模块的rst_seq_done有效后变回0,其余时刻都为0。

flag_from_tx:接收来自发送模块传递过来的 "flag_to_rx "信号。且需要对其进行上升沿下降沿定位。

当其上升沿出现,代表与之连接的TX模块的IP复位完成,并且该上升沿可以作为RX IP的复位信号标志。及其上升沿出现后,对RX IP复位有效。

而下降沿出现,代表与之连接的RX模块的IP复位完成,那么该信号可作为发送数据包发送训练数据0x0C和正常数据的一个分割点,出现之前一直发0x0C,出现之后正常发数据。

TX模块信号解析

对于TX模块的IP的其他信号需要注意,其中需要注意的一些信号:

1. 控制与状态信号

| 信号名 | 方向 | 位宽 | 功能说明 |

|---|---|---|---|

rst |

Input | 1-bit | 全局复位信号(高有效) |

riu_clk |

Input | 1-bit | RIU(Reconfigurable I/O)配置接口时钟(典型值100MHz) |

pll0_locked |

Output | 1-bit | PLL锁定状态指示(1=锁定,0=失锁) |

rst_seq_done |

Output | 1-bit | 初始化序列完成标志(1=就绪) |

vtc_rdy_bscX |

Output | 1-bit*8 | 各Bank的VTU(Voltage/Timing Unit)校准完成信号(X=0~7) |

en_vtc_bscX |

Input | 1-bit*8 | VTU校准使能信号(需拉高以激活延时控制) |

dly_rdy_bscX |

Output | 1-bit*7 | Bank内延时单元校准完成信号(索引1~7) |

TX的ip操作流程:上电后拉高en_vtc_bscX → 等待vtc_rdy_bscX和dly_rdy_bscX变高 → 最终rst_seq_done有效 → 开始发送数据。所以一般将en_vtc_bscX直接置为1。

2. 时钟管理信号

| 信号名 | 方向 | 功能说明 |

|---|---|---|

clk |

Input | 用户逻辑数据时钟(频率需匹配PLL设置) |

shared_pll0_clkoutphy_out |

Output | PLL输出的高速串行时钟(连接至IO引脚或下一级IP) |

pll0_clkout0 |

Output | PLL分频后的并行参考时钟(用户逻辑同步时钟) |

3. 数据通道信号(按Bank分组)

| 信号格式 | 方向 | 位宽 | 功能说明 |

|---|---|---|---|

bgX_pinY_Z |

Output | 1-bit | Bank X(0~3)的引脚 Y(0~11)输出数据(直连FPGA物理引脚) |

data_from_fabric_bgX_pinY_Z |

Input | 4-bit | 用户逻辑输入数据 (与bgX_pinY_Z关联,发送时IP将4位并转1位串行) |

数据流示例 (Bank 0 Pin 0):

用户逻辑 →

data_from_fabric_bg0_pin0_0[3:0]→ HSSIO IP → 串行化为单比特流 →bg0_pin0_0输出

下面代码块为High Speed SelectIO Wizard设置为单向发送模块生成的.veo文件内容:

TG1_HSSIO_TX your_instance_name (

.vtc_rdy_bsc0(vtc_rdy_bsc0), // output wire vtc_rdy_bsc0

.en_vtc_bsc0(en_vtc_bsc0), // input wire en_vtc_bsc0

.vtc_rdy_bsc1(vtc_rdy_bsc1), // output wire vtc_rdy_bsc1

.en_vtc_bsc1(en_vtc_bsc1), // input wire en_vtc_bsc1

.vtc_rdy_bsc2(vtc_rdy_bsc2), // output wire vtc_rdy_bsc2

.en_vtc_bsc2(en_vtc_bsc2), // input wire en_vtc_bsc2

.vtc_rdy_bsc3(vtc_rdy_bsc3), // output wire vtc_rdy_bsc3

.en_vtc_bsc3(en_vtc_bsc3), // input wire en_vtc_bsc3

.vtc_rdy_bsc4(vtc_rdy_bsc4), // output wire vtc_rdy_bsc4

.en_vtc_bsc4(en_vtc_bsc4), // input wire en_vtc_bsc4

.vtc_rdy_bsc5(vtc_rdy_bsc5), // output wire vtc_rdy_bsc5

.en_vtc_bsc5(en_vtc_bsc5), // input wire en_vtc_bsc5

.vtc_rdy_bsc6(vtc_rdy_bsc6), // output wire vtc_rdy_bsc6

.en_vtc_bsc6(en_vtc_bsc6), // input wire en_vtc_bsc6

.vtc_rdy_bsc7(vtc_rdy_bsc7), // output wire vtc_rdy_bsc7

.en_vtc_bsc7(en_vtc_bsc7), // input wire en_vtc_bsc7

.dly_rdy_bsc0(dly_rdy_bsc0), // output wire dly_rdy_bsc0

.dly_rdy_bsc1(dly_rdy_bsc1), // output wire dly_rdy_bsc1

.dly_rdy_bsc2(dly_rdy_bsc2), // output wire dly_rdy_bsc2

.dly_rdy_bsc3(dly_rdy_bsc3), // output wire dly_rdy_bsc3

.dly_rdy_bsc4(dly_rdy_bsc4), // output wire dly_rdy_bsc4

.dly_rdy_bsc5(dly_rdy_bsc5), // output wire dly_rdy_bsc5

.dly_rdy_bsc6(dly_rdy_bsc6), // output wire dly_rdy_bsc6

.dly_rdy_bsc7(dly_rdy_bsc7), // output wire dly_rdy_bsc7

.rst_seq_done(rst_seq_done), // output wire rst_seq_done

.shared_pll0_clkoutphy_out(shared_pll0_clkoutphy_out), // output wire shared_pll0_clkoutphy_out

.pll0_clkout0(pll0_clkout0), // output wire pll0_clkout0

.rst(rst), // input wire rst

.clk(clk), // input wire clk

.riu_clk(riu_clk), // input wire riu_clk

.pll0_locked(pll0_locked), // output wire pll0_locked

.bg0_pin0_0(bg0_pin0_0), // output wire bg0_pin0_0

.data_from_fabric_bg0_pin0_0(data_from_fabric_bg0_pin0_0), // input wire [3 : 0] data_from_fabric_bg0_pin0_0

.bg0_pin1_1(bg0_pin1_1), // output wire bg0_pin1_1

.bg0_pin2_2(bg0_pin2_2), // output wire bg0_pin2_2

.data_from_fabric_bg0_pin2_2(data_from_fabric_bg0_pin2_2), // input wire [3 : 0] data_from_fabric_bg0_pin2_2

.bg0_pin3_3(bg0_pin3_3), // output wire bg0_pin3_3

.bg0_pin4_4(bg0_pin4_4), // output wire bg0_pin4_4

.data_from_fabric_bg0_pin4_4(data_from_fabric_bg0_pin4_4), // input wire [3 : 0] data_from_fabric_bg0_pin4_4

.bg0_pin5_5(bg0_pin5_5), // output wire bg0_pin5_5

.bg0_pin6_6(bg0_pin6_6), // output wire bg0_pin6_6

.data_from_fabric_bg0_pin6_6(data_from_fabric_bg0_pin6_6), // input wire [3 : 0] data_from_fabric_bg0_pin6_6

.bg0_pin7_7(bg0_pin7_7), // output wire bg0_pin7_7

.bg0_pin8_8(bg0_pin8_8), // output wire bg0_pin8_8

.data_from_fabric_bg0_pin8_8(data_from_fabric_bg0_pin8_8), // input wire [3 : 0] data_from_fabric_bg0_pin8_8

.bg0_pin9_9(bg0_pin9_9), // output wire bg0_pin9_9

.bg0_pin10_10(bg0_pin10_10), // output wire bg0_pin10_10

.data_from_fabric_bg0_pin10_10(data_from_fabric_bg0_pin10_10), // input wire [3 : 0] data_from_fabric_bg0_pin10_10

.bg0_pin11_11(bg0_pin11_11), // output wire bg0_pin11_11

.bg1_pin0_13(bg1_pin0_13), // output wire bg1_pin0_13

.data_from_fabric_bg1_pin0_13(data_from_fabric_bg1_pin0_13), // input wire [3 : 0] data_from_fabric_bg1_pin0_13

.bg1_pin1_14(bg1_pin1_14), // output wire bg1_pin1_14

.bg1_pin2_15(bg1_pin2_15), // output wire bg1_pin2_15

.data_from_fabric_bg1_pin2_15(data_from_fabric_bg1_pin2_15), // input wire [3 : 0] data_from_fabric_bg1_pin2_15

.bg1_pin3_16(bg1_pin3_16), // output wire bg1_pin3_16

.bg1_pin4_17(bg1_pin4_17), // output wire bg1_pin4_17

.data_from_fabric_bg1_pin4_17(data_from_fabric_bg1_pin4_17), // input wire [3 : 0] data_from_fabric_bg1_pin4_17

.bg1_pin5_18(bg1_pin5_18), // output wire bg1_pin5_18

.bg1_pin6_19(bg1_pin6_19), // output wire bg1_pin6_19

.data_from_fabric_bg1_pin6_19(data_from_fabric_bg1_pin6_19), // input wire [3 : 0] data_from_fabric_bg1_pin6_19

.bg1_pin7_20(bg1_pin7_20), // output wire bg1_pin7_20

.bg1_pin8_21(bg1_pin8_21), // output wire bg1_pin8_21

.data_from_fabric_bg1_pin8_21(data_from_fabric_bg1_pin8_21), // input wire [3 : 0] data_from_fabric_bg1_pin8_21

.bg1_pin9_22(bg1_pin9_22), // output wire bg1_pin9_22

.bg1_pin10_23(bg1_pin10_23), // output wire bg1_pin10_23

.data_from_fabric_bg1_pin10_23(data_from_fabric_bg1_pin10_23), // input wire [3 : 0] data_from_fabric_bg1_pin10_23

.bg1_pin11_24(bg1_pin11_24), // output wire bg1_pin11_24

.bg2_pin2_28(bg2_pin2_28), // output wire bg2_pin2_28

.data_from_fabric_bg2_pin2_28(data_from_fabric_bg2_pin2_28), // input wire [3 : 0] data_from_fabric_bg2_pin2_28

.bg2_pin3_29(bg2_pin3_29), // output wire bg2_pin3_29

.bg2_pin4_30(bg2_pin4_30), // output wire bg2_pin4_30

.data_from_fabric_bg2_pin4_30(data_from_fabric_bg2_pin4_30), // input wire [3 : 0] data_from_fabric_bg2_pin4_30

.bg2_pin5_31(bg2_pin5_31), // output wire bg2_pin5_31

.bg2_pin6_32(bg2_pin6_32), // output wire bg2_pin6_32

.data_from_fabric_bg2_pin6_32(data_from_fabric_bg2_pin6_32), // input wire [3 : 0] data_from_fabric_bg2_pin6_32

.bg2_pin7_33(bg2_pin7_33), // output wire bg2_pin7_33

.bg2_pin8_34(bg2_pin8_34), // output wire bg2_pin8_34

.data_from_fabric_bg2_pin8_34(data_from_fabric_bg2_pin8_34), // input wire [3 : 0] data_from_fabric_bg2_pin8_34

.bg2_pin9_35(bg2_pin9_35), // output wire bg2_pin9_35

.bg2_pin10_36(bg2_pin10_36), // output wire bg2_pin10_36

.data_from_fabric_bg2_pin10_36(data_from_fabric_bg2_pin10_36), // input wire [3 : 0] data_from_fabric_bg2_pin10_36

.bg2_pin11_37(bg2_pin11_37), // output wire bg2_pin11_37

.bg3_pin0_39(bg3_pin0_39), // output wire bg3_pin0_39

.data_from_fabric_bg3_pin0_39(data_from_fabric_bg3_pin0_39), // input wire [3 : 0] data_from_fabric_bg3_pin0_39

.bg3_pin1_40(bg3_pin1_40), // output wire bg3_pin1_40

.bg3_pin2_41(bg3_pin2_41), // output wire bg3_pin2_41

.data_from_fabric_bg3_pin2_41(data_from_fabric_bg3_pin2_41), // input wire [3 : 0] data_from_fabric_bg3_pin2_41

.bg3_pin3_42(bg3_pin3_42), // output wire bg3_pin3_42

.bg3_pin4_43(bg3_pin4_43), // output wire bg3_pin4_43

.data_from_fabric_bg3_pin4_43(data_from_fabric_bg3_pin4_43), // input wire [3 : 0] data_from_fabric_bg3_pin4_43

.bg3_pin5_44(bg3_pin5_44), // output wire bg3_pin5_44

.bg3_pin6_45(bg3_pin6_45), // output wire bg3_pin6_45

.data_from_fabric_bg3_pin6_45(data_from_fabric_bg3_pin6_45), // input wire [3 : 0] data_from_fabric_bg3_pin6_45

.bg3_pin7_46(bg3_pin7_46), // output wire bg3_pin7_46

.bg3_pin8_47(bg3_pin8_47), // output wire bg3_pin8_47

.data_from_fabric_bg3_pin8_47(data_from_fabric_bg3_pin8_47), // input wire [3 : 0] data_from_fabric_bg3_pin8_47

.bg3_pin9_48(bg3_pin9_48), // output wire bg3_pin9_48

.bg3_pin10_49(bg3_pin10_49), // output wire bg3_pin10_49

.data_from_fabric_bg3_pin10_49(data_from_fabric_bg3_pin10_49), // input wire [3 : 0] data_from_fabric_bg3_pin10_49

.bg3_pin11_50(bg3_pin11_50) // output wire bg3_pin11_50

);RX模块信号解析

1. 控制与状态信号

| 信号名 | 方向 | 功能说明 |

|---|---|---|

rst |

Input | 全局复位信号(高有效) |

riu_clk |

Input | RIU配置接口时钟(100-200MHz) |

pll0_locked |

Output | 内置PLL锁定状态(1=锁定) |

rst_seq_done |

Output | RX初始化序列完成标志(1=就绪) |

vtc_rdy_bscX |

Output | Bank X的VTU时序单元校准完成信号 |

en_vtc_bscX |

Input | Bank X的VTU校准使能信号(需拉高,例化直接置1) |

dly_rdy_bscX |

Output | Bank X的IDELAY延时单元校准完成信号 |

2. Bitslip数据对齐控制

| 信号名 | 功能说明 |

|---|---|

start_bitslip |

输入:启动Bitslip校准序列(脉冲触发) |

rx_bitslip_sync_done |

输出:所有通道Bitslip对齐完成标志 |

bitslip_error_XX |

输出:通道XX的对齐错误指示(1=检测到错误,如超时或训练序列不匹配) |

fifo_rd_data_valid |

输出:解串后的并行数据有效标志 |

Bitslip工作流程 :

拉高

start_bitslip→ IP自动发送训练序列 → 移位检测匹配 →rx_bitslip_sync_done变高若超时未对齐 →

bitslip_error_XX报错本次实验中,由于在配置RX的时候,

Bitslip Training Pattern参数配置的是0x0C,意味着RX的IP在"拉高start_bitslip→ IP自动发送训练序列 → 移位检测匹配 →rx_bitslip_sync_done变高"这个流程中,从外界也就是TX模块传递进来的数据要一直稳定的为C,直到训练结束后,才能发送其他数据。

3. 数据时钟管理

| 信号名 | 方向 | 功能说明 |

|---|---|---|

clk |

Input | 用户逻辑参考时钟(需与PLL输入同源) |

shared_pll0_clkoutphy_out |

Output | 高速串行采样时钟(供其他模块使用) |

pll0_clkout0 |

Output | PLL生成的并行输出时钟(用于同步data_to_fabric_*) |

fifo_rd_clk_XX |

Input | 通道XX的FIFO读取时钟(用户自定义) |

4. 数据通道信号(按Bank分组)

| 信号格式 | 方向 | 位宽 | 功能说明 |

|---|---|---|---|

bgX_pinY_Z |

Input | 1-bit | Bank X的引脚Y输入数据(直连FPGA物理引脚) |

data_to_fabric_bgX_pinY_Z |

Output | 4-bit | 解串后的并行数据(ISERDES将1位串行数据转换为4位并行输出至用户逻辑) |

数据流示例 (Bank 0 Pin 0):

外部引脚输入 →

bg0_pin0_0→ ISERDES解串 →data_to_fabric_bg0_pin0_0[3:0]→ 用户逻辑

5. FIFO状态信号

| 信号名 | 方向 | 功能说明 |

|---|---|---|

fifo_empty_XX |

Output | 通道XX的FIFO空标志(1=无数据可读) |

fifo_rd_data_valid |

Output | FIFO读取数据有效标志 |

下面代码块为High Speed SelectIO Wizard设置为单向接收模块生成的.veo文件内容:

TG1_HSSIO_RX your_instance_name (

.fifo_rd_data_valid(fifo_rd_data_valid), // output wire fifo_rd_data_valid

.start_bitslip(start_bitslip), // input wire start_bitslip

.rx_bitslip_sync_done(rx_bitslip_sync_done), // output wire rx_bitslip_sync_done

.bitslip_error_0(bitslip_error_0), // output wire bitslip_error_0

.bitslip_error_2(bitslip_error_2), // output wire bitslip_error_2

.bitslip_error_4(bitslip_error_4), // output wire bitslip_error_4

.bitslip_error_6(bitslip_error_6), // output wire bitslip_error_6

.bitslip_error_8(bitslip_error_8), // output wire bitslip_error_8

.bitslip_error_10(bitslip_error_10), // output wire bitslip_error_10

.bitslip_error_13(bitslip_error_13), // output wire bitslip_error_13

.bitslip_error_15(bitslip_error_15), // output wire bitslip_error_15

.bitslip_error_17(bitslip_error_17), // output wire bitslip_error_17

.bitslip_error_19(bitslip_error_19), // output wire bitslip_error_19

.bitslip_error_21(bitslip_error_21), // output wire bitslip_error_21

.bitslip_error_23(bitslip_error_23), // output wire bitslip_error_23

.bitslip_error_28(bitslip_error_28), // output wire bitslip_error_28

.bitslip_error_30(bitslip_error_30), // output wire bitslip_error_30

.bitslip_error_32(bitslip_error_32), // output wire bitslip_error_32

.bitslip_error_34(bitslip_error_34), // output wire bitslip_error_34

.bitslip_error_36(bitslip_error_36), // output wire bitslip_error_36

.bitslip_error_39(bitslip_error_39), // output wire bitslip_error_39

.bitslip_error_41(bitslip_error_41), // output wire bitslip_error_41

.bitslip_error_43(bitslip_error_43), // output wire bitslip_error_43

.bitslip_error_45(bitslip_error_45), // output wire bitslip_error_45

.bitslip_error_47(bitslip_error_47), // output wire bitslip_error_47

.bitslip_error_49(bitslip_error_49), // output wire bitslip_error_49

.fifo_rd_clk_0(fifo_rd_clk_0), // input wire fifo_rd_clk_0

.fifo_rd_clk_2(fifo_rd_clk_2), // input wire fifo_rd_clk_2

.fifo_rd_clk_4(fifo_rd_clk_4), // input wire fifo_rd_clk_4

.fifo_rd_clk_6(fifo_rd_clk_6), // input wire fifo_rd_clk_6

.fifo_rd_clk_8(fifo_rd_clk_8), // input wire fifo_rd_clk_8

.fifo_rd_clk_10(fifo_rd_clk_10), // input wire fifo_rd_clk_10

.fifo_rd_clk_13(fifo_rd_clk_13), // input wire fifo_rd_clk_13

.fifo_rd_clk_15(fifo_rd_clk_15), // input wire fifo_rd_clk_15

.fifo_rd_clk_17(fifo_rd_clk_17), // input wire fifo_rd_clk_17

.fifo_rd_clk_19(fifo_rd_clk_19), // input wire fifo_rd_clk_19

.fifo_rd_clk_21(fifo_rd_clk_21), // input wire fifo_rd_clk_21

.fifo_rd_clk_23(fifo_rd_clk_23), // input wire fifo_rd_clk_23

.fifo_rd_clk_28(fifo_rd_clk_28), // input wire fifo_rd_clk_28

.fifo_rd_clk_30(fifo_rd_clk_30), // input wire fifo_rd_clk_30

.fifo_rd_clk_32(fifo_rd_clk_32), // input wire fifo_rd_clk_32

.fifo_rd_clk_34(fifo_rd_clk_34), // input wire fifo_rd_clk_34

.fifo_rd_clk_36(fifo_rd_clk_36), // input wire fifo_rd_clk_36

.fifo_rd_clk_39(fifo_rd_clk_39), // input wire fifo_rd_clk_39

.fifo_rd_clk_41(fifo_rd_clk_41), // input wire fifo_rd_clk_41

.fifo_rd_clk_43(fifo_rd_clk_43), // input wire fifo_rd_clk_43

.fifo_rd_clk_45(fifo_rd_clk_45), // input wire fifo_rd_clk_45

.fifo_rd_clk_47(fifo_rd_clk_47), // input wire fifo_rd_clk_47

.fifo_rd_clk_49(fifo_rd_clk_49), // input wire fifo_rd_clk_49

.fifo_empty_0(fifo_empty_0), // output wire fifo_empty_0

.fifo_empty_2(fifo_empty_2), // output wire fifo_empty_2

.fifo_empty_4(fifo_empty_4), // output wire fifo_empty_4

.fifo_empty_6(fifo_empty_6), // output wire fifo_empty_6

.fifo_empty_8(fifo_empty_8), // output wire fifo_empty_8

.fifo_empty_10(fifo_empty_10), // output wire fifo_empty_10

.fifo_empty_13(fifo_empty_13), // output wire fifo_empty_13

.fifo_empty_15(fifo_empty_15), // output wire fifo_empty_15

.fifo_empty_17(fifo_empty_17), // output wire fifo_empty_17

.fifo_empty_19(fifo_empty_19), // output wire fifo_empty_19

.fifo_empty_21(fifo_empty_21), // output wire fifo_empty_21

.fifo_empty_23(fifo_empty_23), // output wire fifo_empty_23

.fifo_empty_28(fifo_empty_28), // output wire fifo_empty_28

.fifo_empty_30(fifo_empty_30), // output wire fifo_empty_30

.fifo_empty_32(fifo_empty_32), // output wire fifo_empty_32

.fifo_empty_34(fifo_empty_34), // output wire fifo_empty_34

.fifo_empty_36(fifo_empty_36), // output wire fifo_empty_36

.fifo_empty_39(fifo_empty_39), // output wire fifo_empty_39

.fifo_empty_41(fifo_empty_41), // output wire fifo_empty_41

.fifo_empty_43(fifo_empty_43), // output wire fifo_empty_43

.fifo_empty_45(fifo_empty_45), // output wire fifo_empty_45

.fifo_empty_47(fifo_empty_47), // output wire fifo_empty_47

.fifo_empty_49(fifo_empty_49), // output wire fifo_empty_49

.vtc_rdy_bsc0(vtc_rdy_bsc0), // output wire vtc_rdy_bsc0

.en_vtc_bsc0(en_vtc_bsc0), // input wire en_vtc_bsc0

.vtc_rdy_bsc1(vtc_rdy_bsc1), // output wire vtc_rdy_bsc1

.en_vtc_bsc1(en_vtc_bsc1), // input wire en_vtc_bsc1

.vtc_rdy_bsc2(vtc_rdy_bsc2), // output wire vtc_rdy_bsc2

.en_vtc_bsc2(en_vtc_bsc2), // input wire en_vtc_bsc2

.vtc_rdy_bsc3(vtc_rdy_bsc3), // output wire vtc_rdy_bsc3

.en_vtc_bsc3(en_vtc_bsc3), // input wire en_vtc_bsc3

.vtc_rdy_bsc4(vtc_rdy_bsc4), // output wire vtc_rdy_bsc4

.en_vtc_bsc4(en_vtc_bsc4), // input wire en_vtc_bsc4

.vtc_rdy_bsc5(vtc_rdy_bsc5), // output wire vtc_rdy_bsc5

.en_vtc_bsc5(en_vtc_bsc5), // input wire en_vtc_bsc5

.vtc_rdy_bsc6(vtc_rdy_bsc6), // output wire vtc_rdy_bsc6

.en_vtc_bsc6(en_vtc_bsc6), // input wire en_vtc_bsc6

.vtc_rdy_bsc7(vtc_rdy_bsc7), // output wire vtc_rdy_bsc7

.en_vtc_bsc7(en_vtc_bsc7), // input wire en_vtc_bsc7

.dly_rdy_bsc0(dly_rdy_bsc0), // output wire dly_rdy_bsc0

.dly_rdy_bsc1(dly_rdy_bsc1), // output wire dly_rdy_bsc1

.dly_rdy_bsc2(dly_rdy_bsc2), // output wire dly_rdy_bsc2

.dly_rdy_bsc3(dly_rdy_bsc3), // output wire dly_rdy_bsc3

.dly_rdy_bsc4(dly_rdy_bsc4), // output wire dly_rdy_bsc4

.dly_rdy_bsc5(dly_rdy_bsc5), // output wire dly_rdy_bsc5

.dly_rdy_bsc6(dly_rdy_bsc6), // output wire dly_rdy_bsc6

.dly_rdy_bsc7(dly_rdy_bsc7), // output wire dly_rdy_bsc7

.rst_seq_done(rst_seq_done), // output wire rst_seq_done

.shared_pll0_clkoutphy_out(shared_pll0_clkoutphy_out), // output wire shared_pll0_clkoutphy_out

.pll0_clkout0(pll0_clkout0), // output wire pll0_clkout0

.rst(rst), // input wire rst

.clk(clk), // input wire clk

.riu_clk(riu_clk), // input wire riu_clk

.pll0_locked(pll0_locked), // output wire pll0_locked

.bg2_pin0_nc(bg2_pin0_nc), // input wire bg2_pin0_nc

.bg0_pin0_0(bg0_pin0_0), // input wire bg0_pin0_0

.data_to_fabric_bg0_pin0_0(data_to_fabric_bg0_pin0_0), // output wire [3 : 0] data_to_fabric_bg0_pin0_0

.bg0_pin1_1(bg0_pin1_1), // input wire bg0_pin1_1

.bg0_pin2_2(bg0_pin2_2), // input wire bg0_pin2_2

.data_to_fabric_bg0_pin2_2(data_to_fabric_bg0_pin2_2), // output wire [3 : 0] data_to_fabric_bg0_pin2_2

.bg0_pin3_3(bg0_pin3_3), // input wire bg0_pin3_3

.bg0_pin4_4(bg0_pin4_4), // input wire bg0_pin4_4

.data_to_fabric_bg0_pin4_4(data_to_fabric_bg0_pin4_4), // output wire [3 : 0] data_to_fabric_bg0_pin4_4

.bg0_pin5_5(bg0_pin5_5), // input wire bg0_pin5_5

.bg0_pin6_6(bg0_pin6_6), // input wire bg0_pin6_6

.data_to_fabric_bg0_pin6_6(data_to_fabric_bg0_pin6_6), // output wire [3 : 0] data_to_fabric_bg0_pin6_6

.bg0_pin7_7(bg0_pin7_7), // input wire bg0_pin7_7

.bg0_pin8_8(bg0_pin8_8), // input wire bg0_pin8_8

.data_to_fabric_bg0_pin8_8(data_to_fabric_bg0_pin8_8), // output wire [3 : 0] data_to_fabric_bg0_pin8_8

.bg0_pin9_9(bg0_pin9_9), // input wire bg0_pin9_9

.bg0_pin10_10(bg0_pin10_10), // input wire bg0_pin10_10

.data_to_fabric_bg0_pin10_10(data_to_fabric_bg0_pin10_10), // output wire [3 : 0] data_to_fabric_bg0_pin10_10

.bg0_pin11_11(bg0_pin11_11), // input wire bg0_pin11_11

.bg1_pin0_13(bg1_pin0_13), // input wire bg1_pin0_13

.data_to_fabric_bg1_pin0_13(data_to_fabric_bg1_pin0_13), // output wire [3 : 0] data_to_fabric_bg1_pin0_13

.bg1_pin1_14(bg1_pin1_14), // input wire bg1_pin1_14

.bg1_pin2_15(bg1_pin2_15), // input wire bg1_pin2_15

.data_to_fabric_bg1_pin2_15(data_to_fabric_bg1_pin2_15), // output wire [3 : 0] data_to_fabric_bg1_pin2_15

.bg1_pin3_16(bg1_pin3_16), // input wire bg1_pin3_16

.bg1_pin4_17(bg1_pin4_17), // input wire bg1_pin4_17

.data_to_fabric_bg1_pin4_17(data_to_fabric_bg1_pin4_17), // output wire [3 : 0] data_to_fabric_bg1_pin4_17

.bg1_pin5_18(bg1_pin5_18), // input wire bg1_pin5_18

.bg1_pin6_19(bg1_pin6_19), // input wire bg1_pin6_19

.data_to_fabric_bg1_pin6_19(data_to_fabric_bg1_pin6_19), // output wire [3 : 0] data_to_fabric_bg1_pin6_19

.bg1_pin7_20(bg1_pin7_20), // input wire bg1_pin7_20

.bg1_pin8_21(bg1_pin8_21), // input wire bg1_pin8_21

.data_to_fabric_bg1_pin8_21(data_to_fabric_bg1_pin8_21), // output wire [3 : 0] data_to_fabric_bg1_pin8_21

.bg1_pin9_22(bg1_pin9_22), // input wire bg1_pin9_22

.bg1_pin10_23(bg1_pin10_23), // input wire bg1_pin10_23

.data_to_fabric_bg1_pin10_23(data_to_fabric_bg1_pin10_23), // output wire [3 : 0] data_to_fabric_bg1_pin10_23

.bg1_pin11_24(bg1_pin11_24), // input wire bg1_pin11_24

.bg2_pin2_28(bg2_pin2_28), // input wire bg2_pin2_28

.data_to_fabric_bg2_pin2_28(data_to_fabric_bg2_pin2_28), // output wire [3 : 0] data_to_fabric_bg2_pin2_28

.bg2_pin3_29(bg2_pin3_29), // input wire bg2_pin3_29

.bg2_pin4_30(bg2_pin4_30), // input wire bg2_pin4_30

.data_to_fabric_bg2_pin4_30(data_to_fabric_bg2_pin4_30), // output wire [3 : 0] data_to_fabric_bg2_pin4_30

.bg2_pin5_31(bg2_pin5_31), // input wire bg2_pin5_31

.bg2_pin6_32(bg2_pin6_32), // input wire bg2_pin6_32

.data_to_fabric_bg2_pin6_32(data_to_fabric_bg2_pin6_32), // output wire [3 : 0] data_to_fabric_bg2_pin6_32

.bg2_pin7_33(bg2_pin7_33), // input wire bg2_pin7_33

.bg2_pin8_34(bg2_pin8_34), // input wire bg2_pin8_34

.data_to_fabric_bg2_pin8_34(data_to_fabric_bg2_pin8_34), // output wire [3 : 0] data_to_fabric_bg2_pin8_34

.bg2_pin9_35(bg2_pin9_35), // input wire bg2_pin9_35

.bg2_pin10_36(bg2_pin10_36), // input wire bg2_pin10_36

.data_to_fabric_bg2_pin10_36(data_to_fabric_bg2_pin10_36), // output wire [3 : 0] data_to_fabric_bg2_pin10_36

.bg2_pin11_37(bg2_pin11_37), // input wire bg2_pin11_37

.bg3_pin0_39(bg3_pin0_39), // input wire bg3_pin0_39

.data_to_fabric_bg3_pin0_39(data_to_fabric_bg3_pin0_39), // output wire [3 : 0] data_to_fabric_bg3_pin0_39

.bg3_pin1_40(bg3_pin1_40), // input wire bg3_pin1_40

.bg3_pin2_41(bg3_pin2_41), // input wire bg3_pin2_41

.data_to_fabric_bg3_pin2_41(data_to_fabric_bg3_pin2_41), // output wire [3 : 0] data_to_fabric_bg3_pin2_41

.bg3_pin3_42(bg3_pin3_42), // input wire bg3_pin3_42

.bg3_pin4_43(bg3_pin4_43), // input wire bg3_pin4_43

.data_to_fabric_bg3_pin4_43(data_to_fabric_bg3_pin4_43), // output wire [3 : 0] data_to_fabric_bg3_pin4_43

.bg3_pin5_44(bg3_pin5_44), // input wire bg3_pin5_44

.bg3_pin6_45(bg3_pin6_45), // input wire bg3_pin6_45

.data_to_fabric_bg3_pin6_45(data_to_fabric_bg3_pin6_45), // output wire [3 : 0] data_to_fabric_bg3_pin6_45

.bg3_pin7_46(bg3_pin7_46), // input wire bg3_pin7_46

.bg3_pin8_47(bg3_pin8_47), // input wire bg3_pin8_47

.data_to_fabric_bg3_pin8_47(data_to_fabric_bg3_pin8_47), // output wire [3 : 0] data_to_fabric_bg3_pin8_47

.bg3_pin9_48(bg3_pin9_48), // input wire bg3_pin9_48

.bg3_pin10_49(bg3_pin10_49), // input wire bg3_pin10_49

.data_to_fabric_bg3_pin10_49(data_to_fabric_bg3_pin10_49), // output wire [3 : 0] data_to_fabric_bg3_pin10_49

.bg3_pin11_50(bg3_pin11_50) // input wire bg3_pin11_50

);用户逻辑设计

用户逻辑分为两个部分,其一为给发送模块构造数据包,其二为比对模块,用于检测接收到的包是否和发送的包一致。

TX_GEN造包模块

该模块的作用是,在RX模块训练阶段,构造值为0x0C的数据,当RX模块训练结束后,生成正常递增或者其他要求的88位数据(22对数据通道,每条通道构造的数据包位宽为4)。

RX_MON比对模块

该模块的作用是:将收到的22对4位数据重新组合成88位的数据,并通过判断其是否与发送数据相同,输出检测结果。