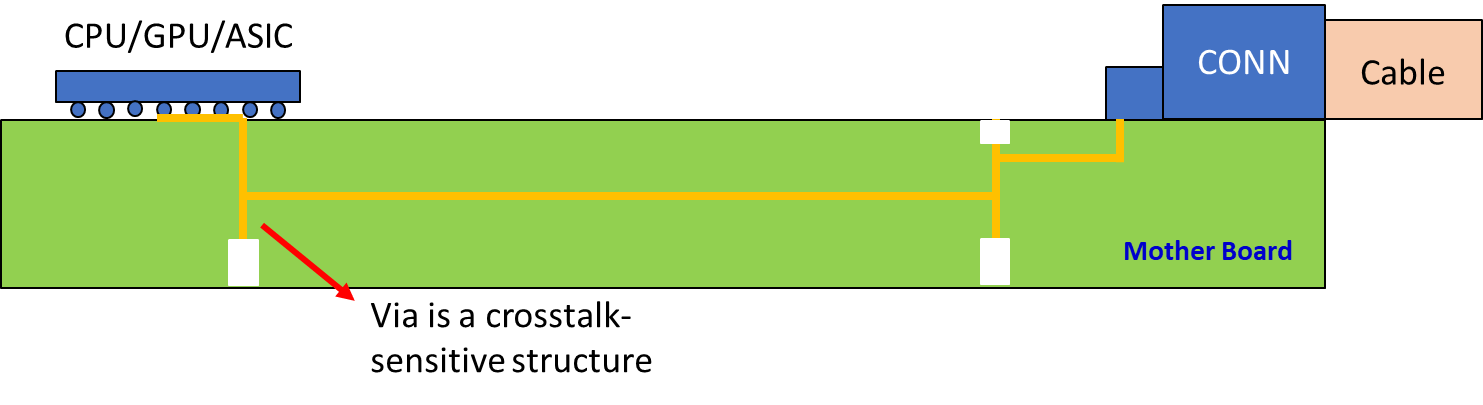

一个高速PCB通道通常包含芯片SerDes IP、走线、穿层Via、连接器和Cable。 其中内层走线对于Crosstalk影响甚微(请参考什么? Stripline的FEXT为0! Why?),而Via与连接器由于其参考路径较差的关系,所以耦合干扰比较严重。 (Cable也不是没有Crosstalk,只是种类繁杂,这边先不提)

在PCB里的Via是垂直结构,因为不像走线有完整的参考路径,所以Crosstalk往往比较差。 所以在系统层级SI设计流程里,Via的模拟分析将会是第一要务。 这边会试着提出一些常见的结构,来探讨一些Via设计的结果。 (主要针对10Gbps以下的讯号,所以带宽控制在20GHz)

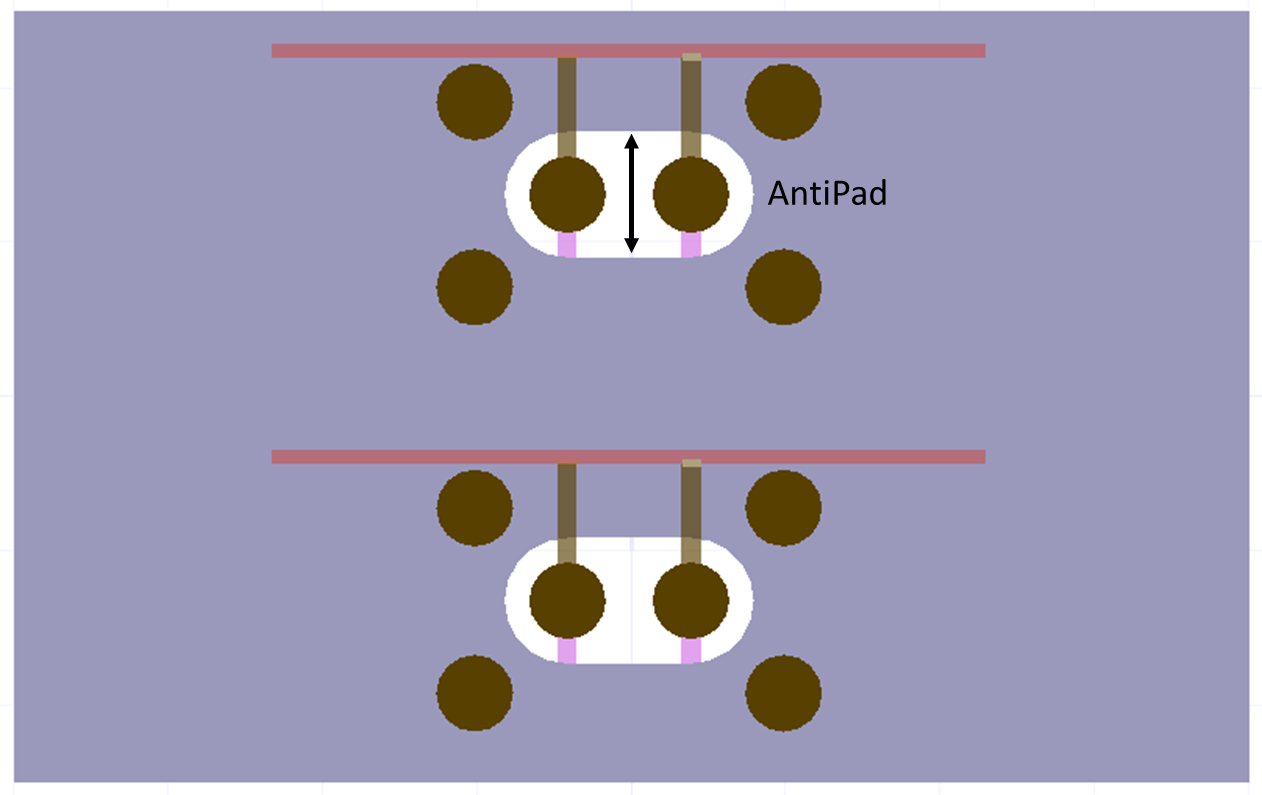

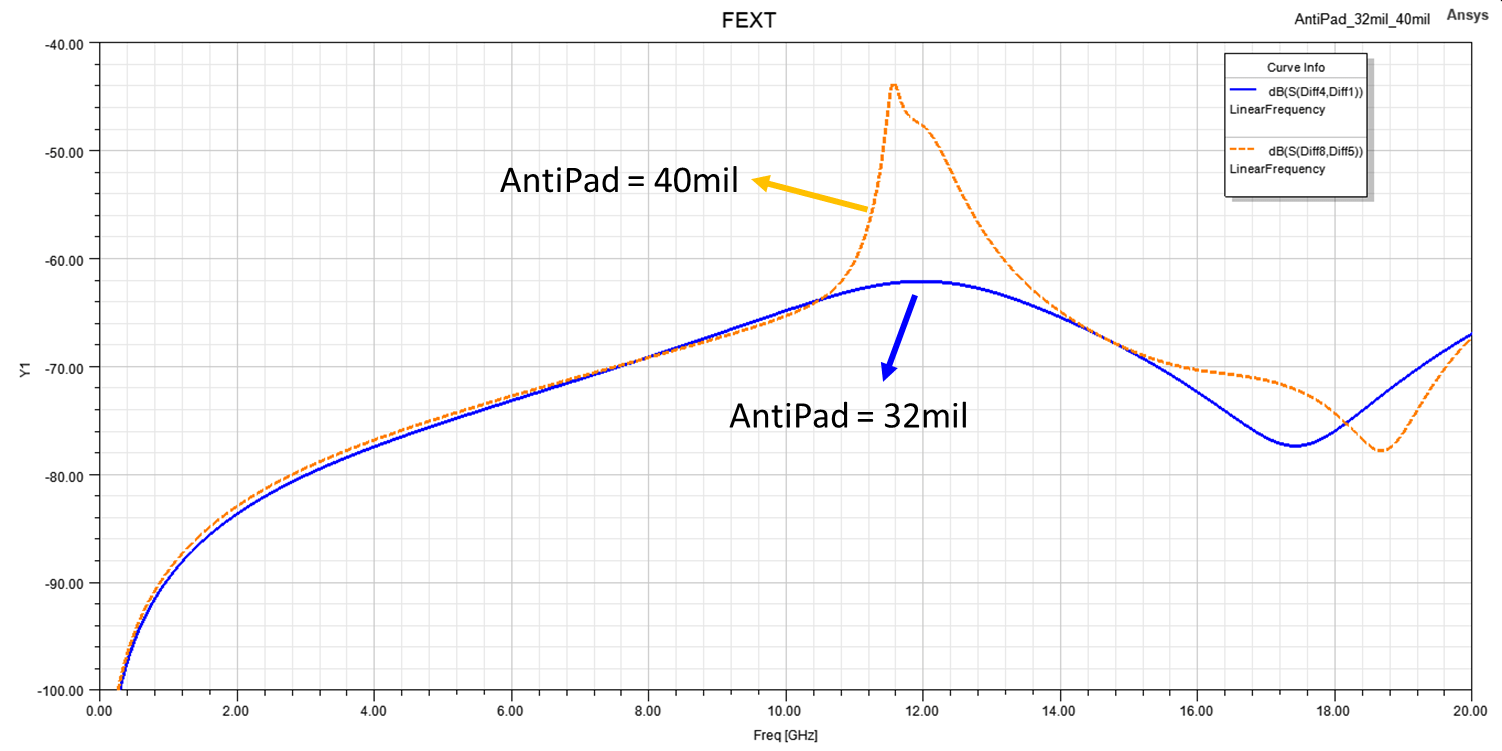

Anti-Pad Design

AntiPad指的是信号的Via为了闪过Power/GND plane避免短路所隔离出的区域,往往会利用隔离的尺寸控制Via的阻抗。 不过其实这个尺寸也会影响Crosstalk,因为如果隔离区越大,会造成某些频率的电磁波没办法被锁在GND的范围内。 从结果来看,40mil的AntiPad造成12GHz这个频带有较大的共振,造成Crosstalk变大。

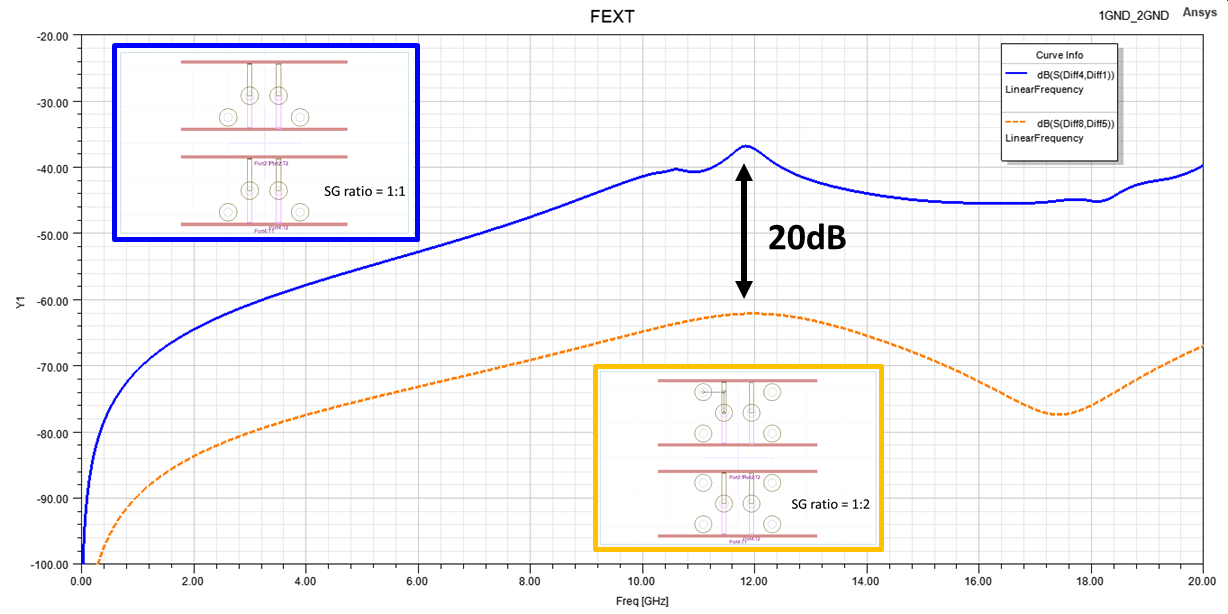

SG Ratio

所谓S:G ratio是指信号via跟GND via的比例,GND via的数量直接决定了这个Via的带宽以及抗干扰的能力。 从结果来看,多了1个GND via,可以有效地将Crosstalk level从-40dB降到-60dB,总共少了20dB。 其实-40dB是大多数FEXT的需求值,也就是说1V的输入电压,只会耦合10mV,这算是SI一个比较基本的criteria,所以其实如果是++从++ ++Crosstalk的角度来看++,1:1的SG ratio在Anti-pad = 32mil的设计内,已经算是很可以了。

SG Ratio = 1: 1,GND Via 位置相反

除了数量外,GND via的位置也相当重要,如果摆放位置不对也会影响其抗干扰效应。 从结果来看,将Via反过来摆放,也就是俩俩信号Via中间并没有GND via的情形下,Crosstalk会较差,不过如果通道损耗控制得好,其实这个差值也还是可以被接受。

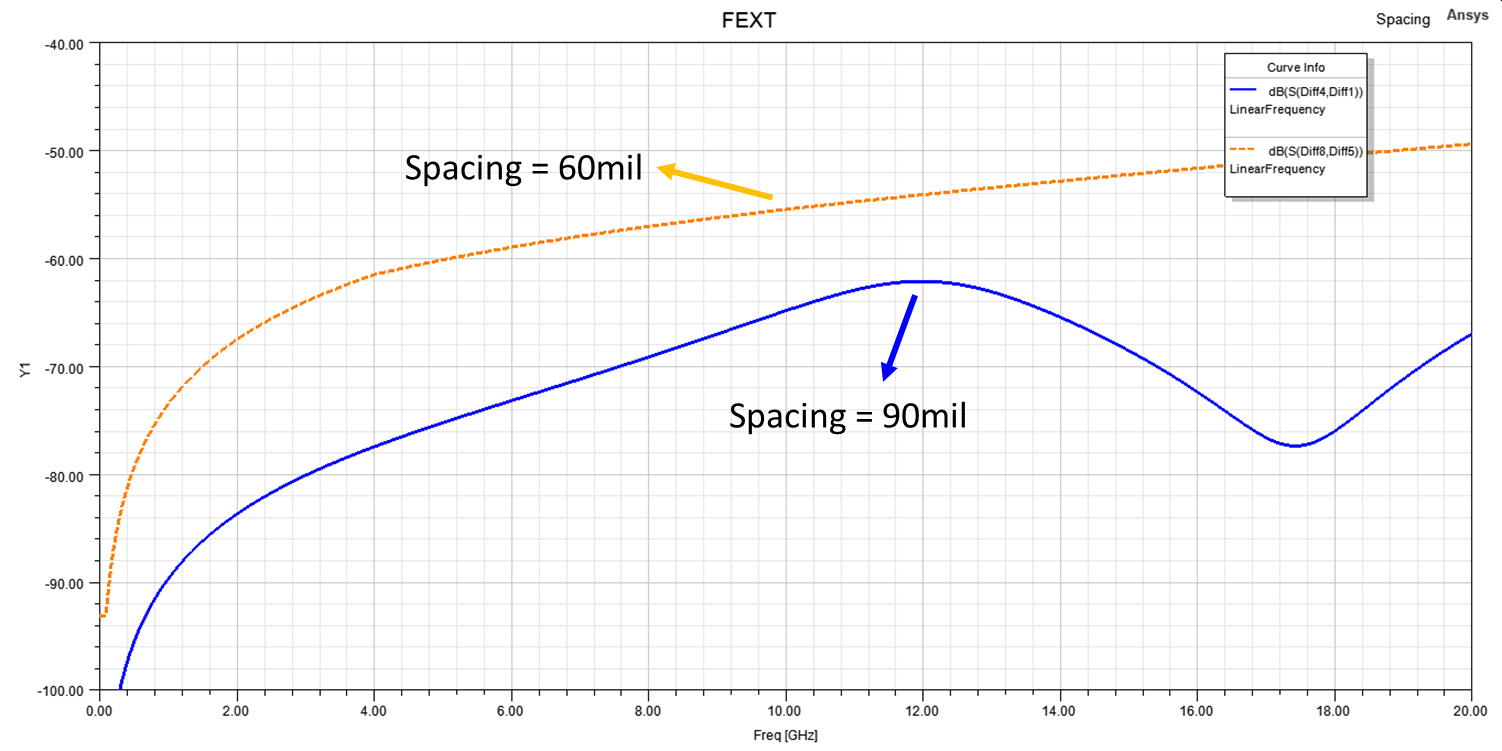

Via Spacing

我们都清楚解决Crosstalk的方法就是将干扰源移走或是拉远,所以当Via spacing从90mil拉近至60mil时 (Transition via的正常spacing),Crosstalk就会变差,不过其实仔细看Crosstalk level还是低于-50dB!

结论

10Gbps以下的讯号,Via设计其实是相对较为简单的,主因是这个频段范围,上升时间大概是30-40ps,对阻抗的感受较不明显,因此不管SG ratio是1:1抑或是1:2,都还不会影响太多。 从这些结果看起来,主要可以分成几个结论:

- 在阻抗可接受之下,AntiPad 越小对Crosstalk的抗干扰越好,越不容易发生某个频段急剧增加的结果。

- GND via的数量直接影响了Crosstalk的能力,不过-40dB已经是很好的结果,是不是一定要用这么多的GND via,这就取决于设计者如何抓系统的Margin。

- 俩俩讯号Via中间还是摆GND via好,不过如果遇到layout空间不足的情况,其实没有摆在中间,也不会是个噩梦。

- Via spacing就算减至60mil,其Crosstalk level还是可以小于-50dB,代表10Gbps以下的讯号是不太需要担心Via间距的。

P.S. 这些模拟分析并不包含Power integrity带来的影响,且也还没有探讨为什么会有那么大的共振唷!