1 D触发器

我们知道电平触发在CLK=1、S=1、R=1的时候,有不确定的状态,输出会进入不稳定状态,这种情况下电路可能会导致逻辑错误,通过如果在时钟信号有效期间,如果S和R在此期间发生了多次变化,那么输出会随着发生多次变化,导致抗干扰能力较差。

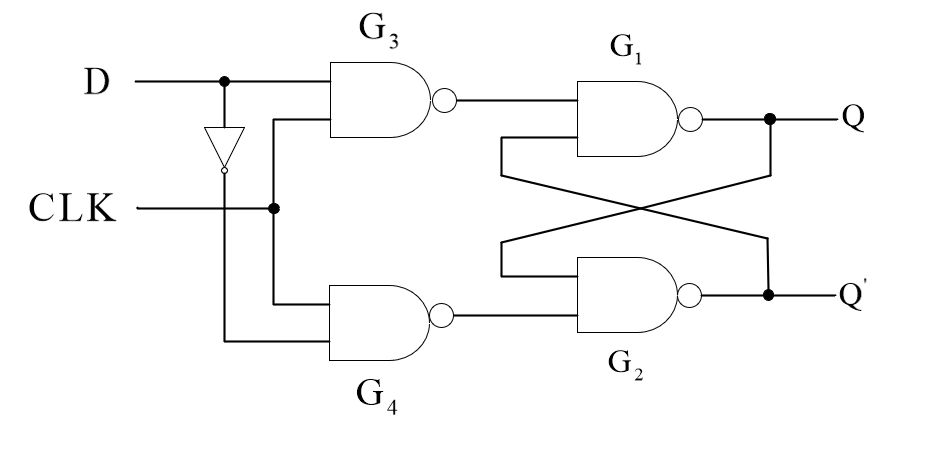

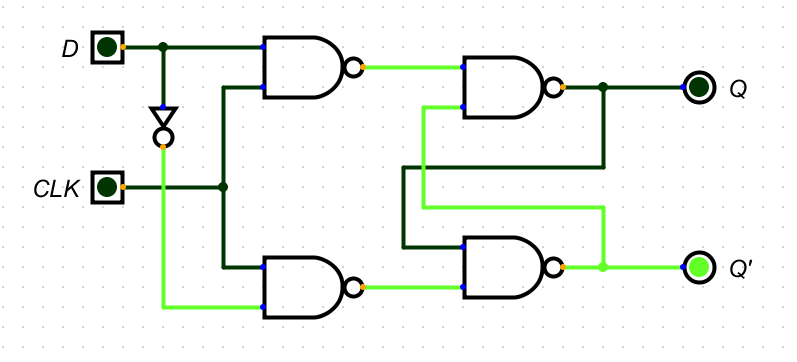

因此,在电平触发SR触发器的基础上,对于电路进行了改进。D触发器相对于电平触发SR触发器进行了简化设计,D触发器仅需要单个输入信号,相对于电平触发SR触发器的两个输入信号S和R更加简介。D触发器的电路如下所示:

图1 D触发器的电路图

图1 D触发器的电路图

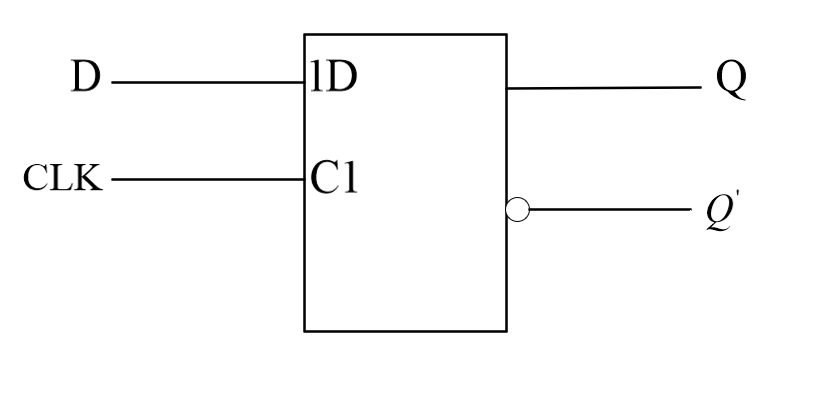

D触发器的图形符号如下所示:

图2 D触发器的图形符号

图2 D触发器的图形符号

当CLK=0时,与电平触发SR触发器相同,触发器的输出结果保持不变。当CLK=1,D=0,此时触发器输出为0,即复位操作。当CLK=1,D=1,此时触发器输出为1,即为置位操作。

总结:

- 当CLK=0时,无论D为何值,此时Q和Q'保持不变。

- 当CLK=1、D=0时,此时Q输出为0(复位)。

- 当CLK=1、D=1时,此时Q输出为1(置位)。

D触发器的真值表如下所示:

| CLK | D | Q | |

|---|---|---|---|

| 0 | × | 0 | 0 |

| 0 | × | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

| [表1 电平触发D触发器的特性表] |

2 使用Digital软件来绘制D触发器

(1)绘制D触发器

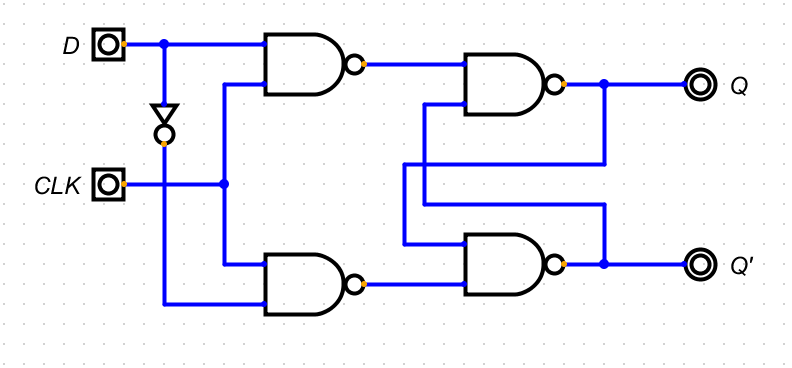

使用Digital软件来绘制D触发器如下所示:

图3 使用Digital软件绘制D触发器的电路图

图3 使用Digital软件绘制D触发器的电路图

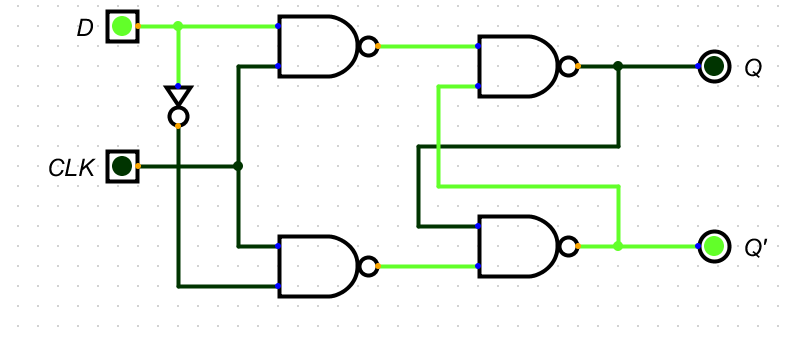

运行该电路,当CLK=1、D=0时,电路输入如下所示:

图4 D触发器运行验证图1

图4 D触发器运行验证图1

可以看到电路完成了置0操作(即复位)。此时在原有电路的基础上在将CLK设置为低电平,如下所示:

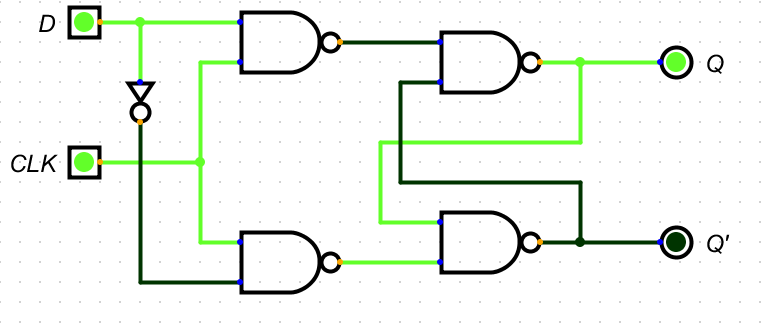

图5 D触发器运行验证图2

图5 D触发器运行验证图2

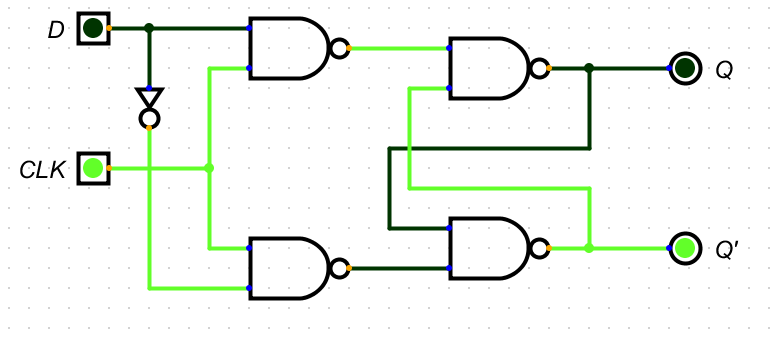

可以看到当CLK=0、D=0时,电路保持原来的状态。在原有基础上,将输入信号D设置为高电平:

图6 D触发器运行验证图3

图6 D触发器运行验证图3

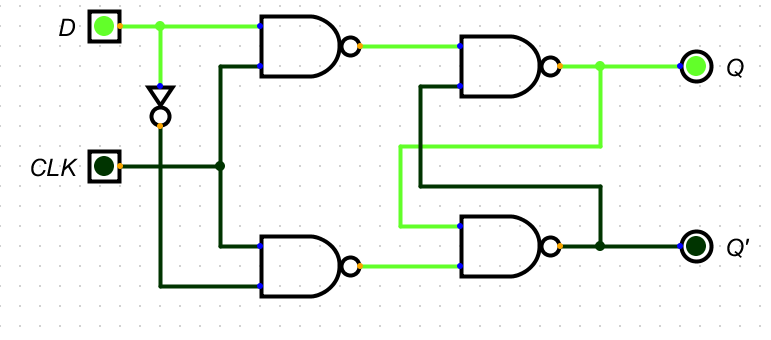

可以看到CLK=0、D=1时此时电平输出结果没有发生变化。此时将CLK设置为高电平:

图7 D触发器运行验证图4

图7 D触发器运行验证图4

可以看到此时电路置1(即置位)。如果再将输入信号CLK接低电平,输出结果如下所示:

图8 D触发器运行验证图5

图8 D触发器运行验证图5

可以看到结果没有发生变化,可以得到结果结论当CLK=0时,D触发器的输出结果不发生变化。

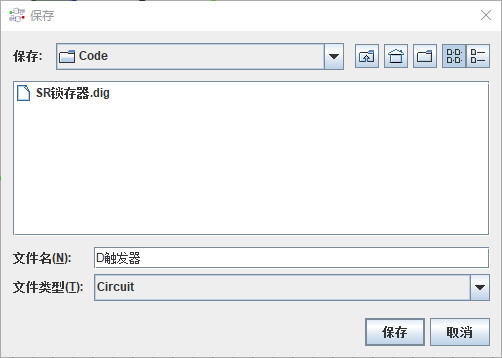

将D触发器的电路图进行保存,可以作为脉冲触发的触发器电路的组件。保存过程如下所示:

图9 将D触发器做为组件进行保存

图9 将D触发器做为组件进行保存