目录

[1 使用Digital软件来绘制脉冲触发的触发器](#1 使用Digital软件来绘制脉冲触发的触发器)

[1.1 使用Digital软件来绘制脉冲触发的SR触发器](#1.1 使用Digital软件来绘制脉冲触发的SR触发器)

[1.2 使用Digitial软件绘制脉冲触发的JK触发器](#1.2 使用Digitial软件绘制脉冲触发的JK触发器)

[1.3 使用Digital软件绘制脉冲触发D触发器](#1.3 使用Digital软件绘制脉冲触发D触发器)

1 使用Digital软件来绘制脉冲触发的触发器

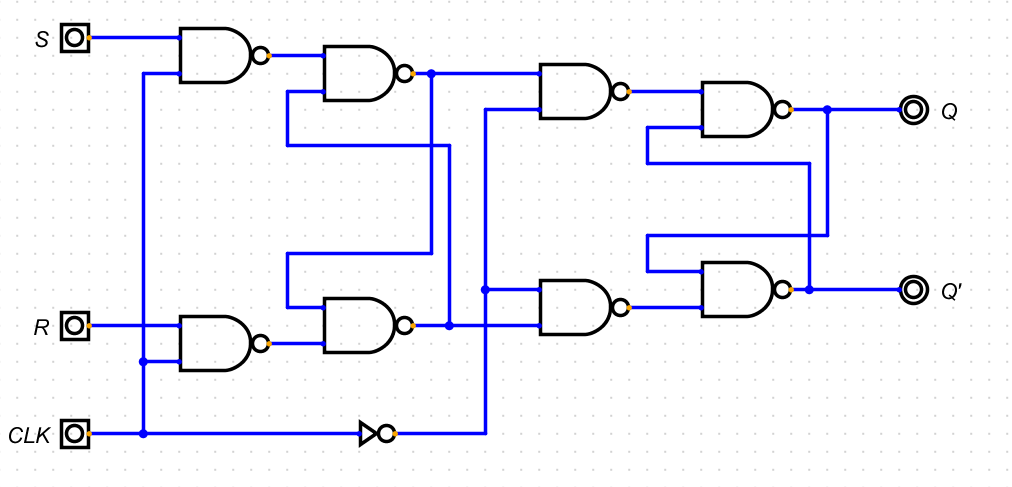

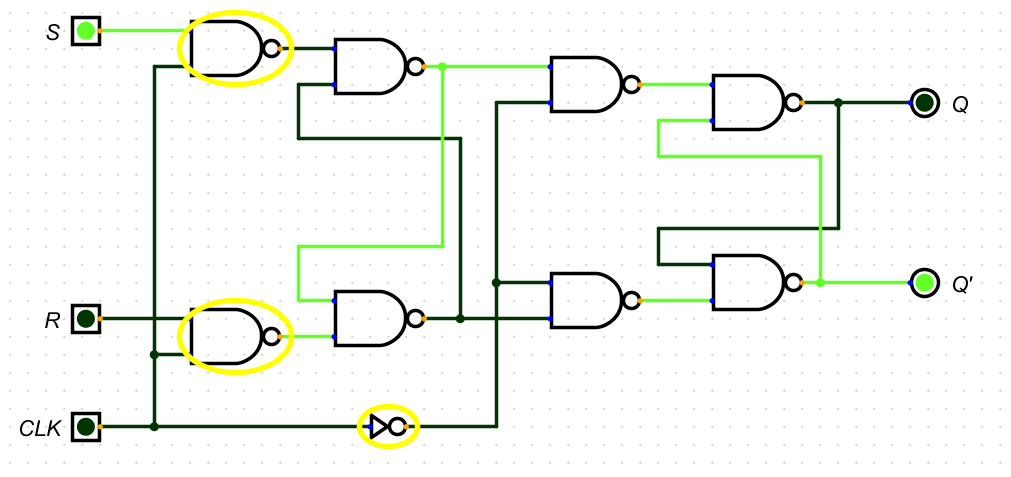

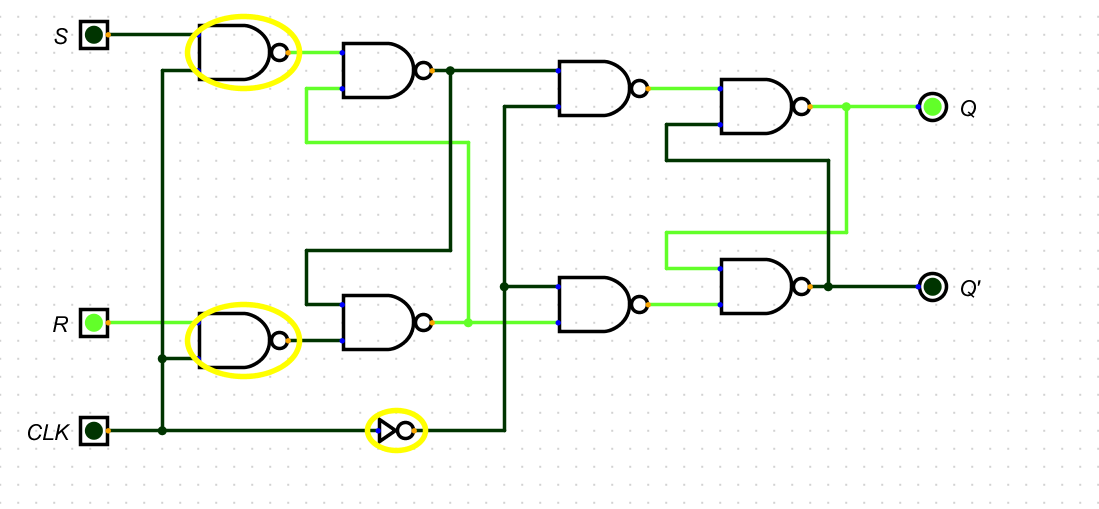

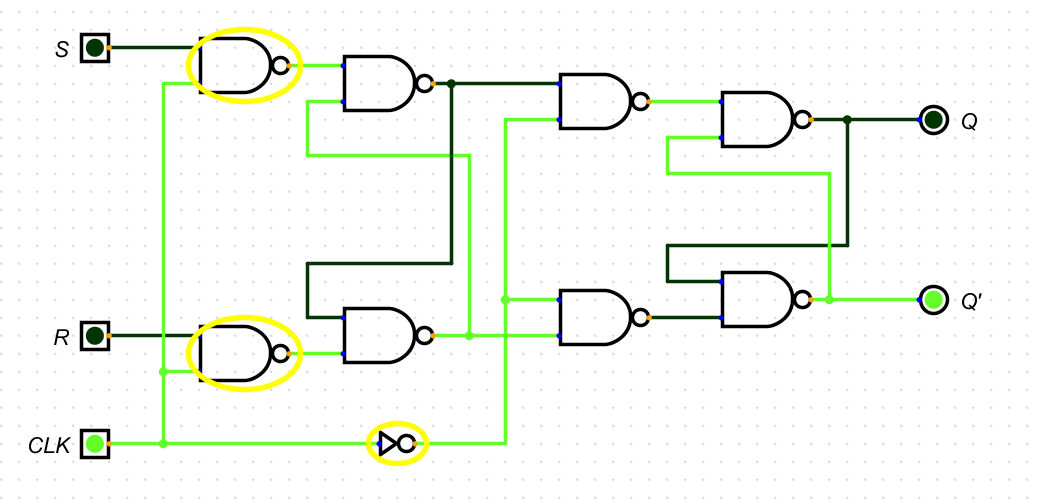

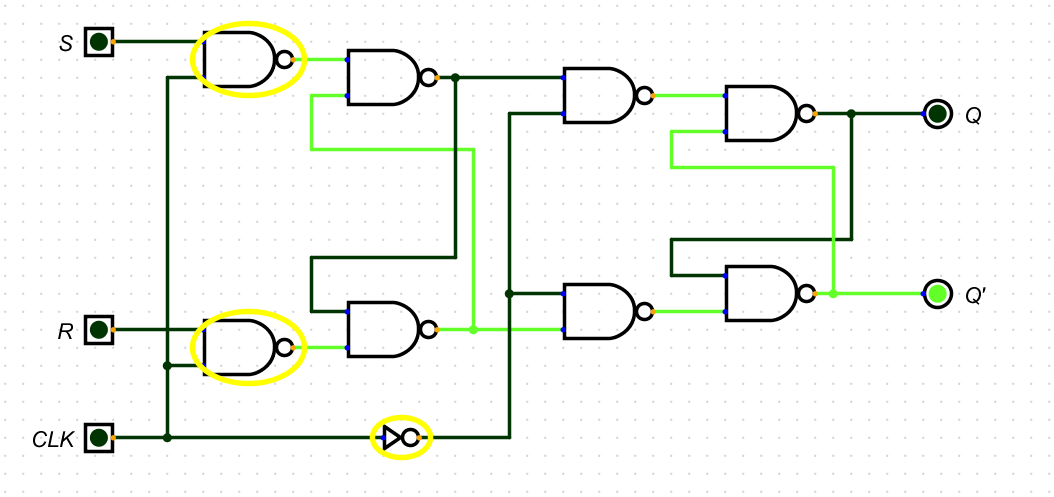

1.1 使用Digital软件来绘制脉冲触发的SR触发器

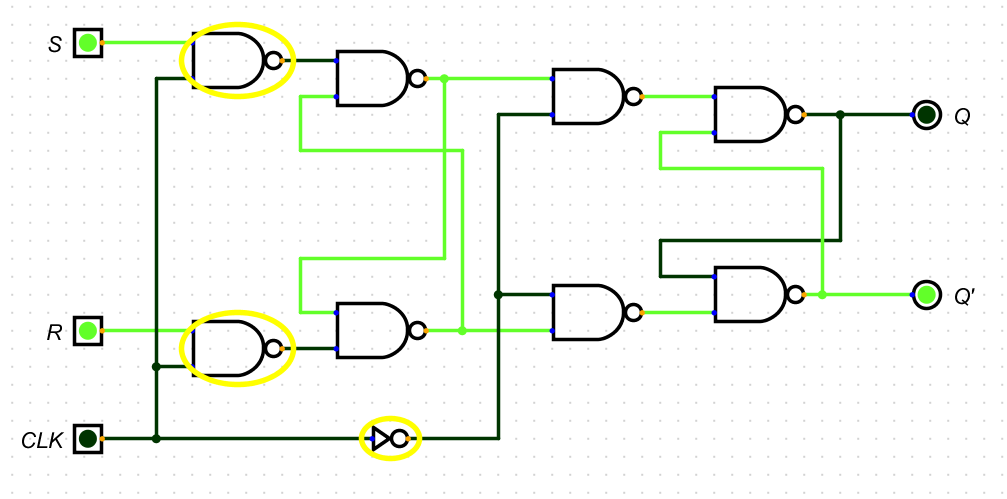

使用Digital软件绘制脉冲触发的SR触发器,电路图如下所示:

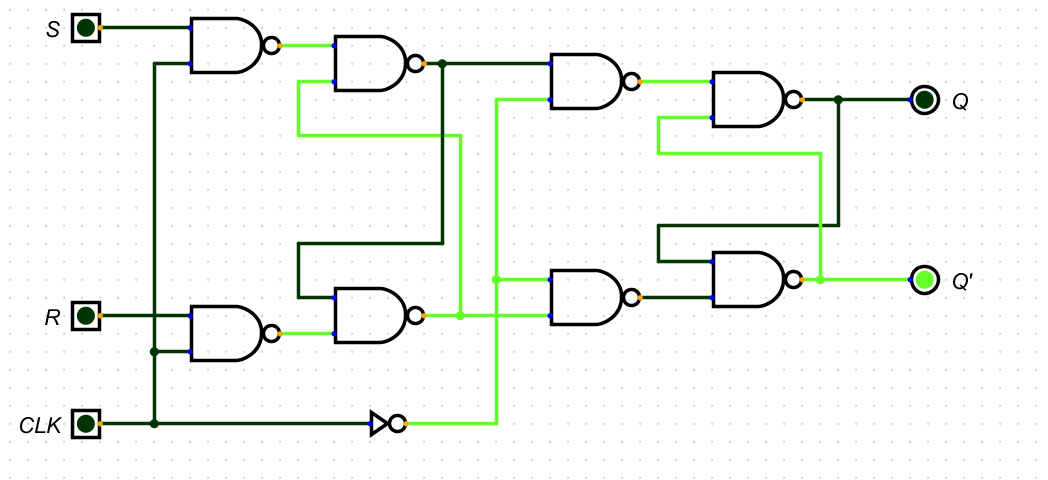

点击运行,初始状态如下所示:

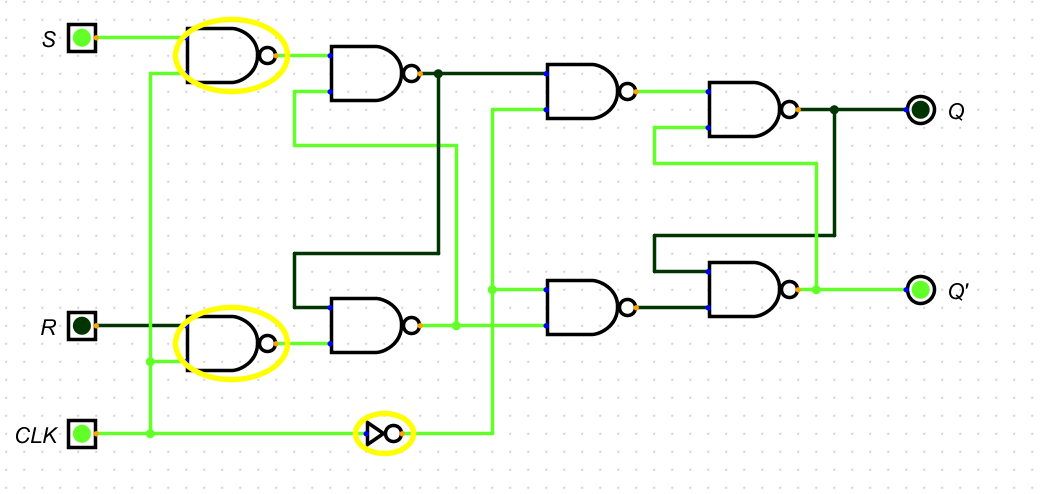

(1)下面开始使用单门仿真运行该电路,首先第一步点击仿真选项栏下面的单门仿真,首先将J置于1,K置于0,CLK置于1:

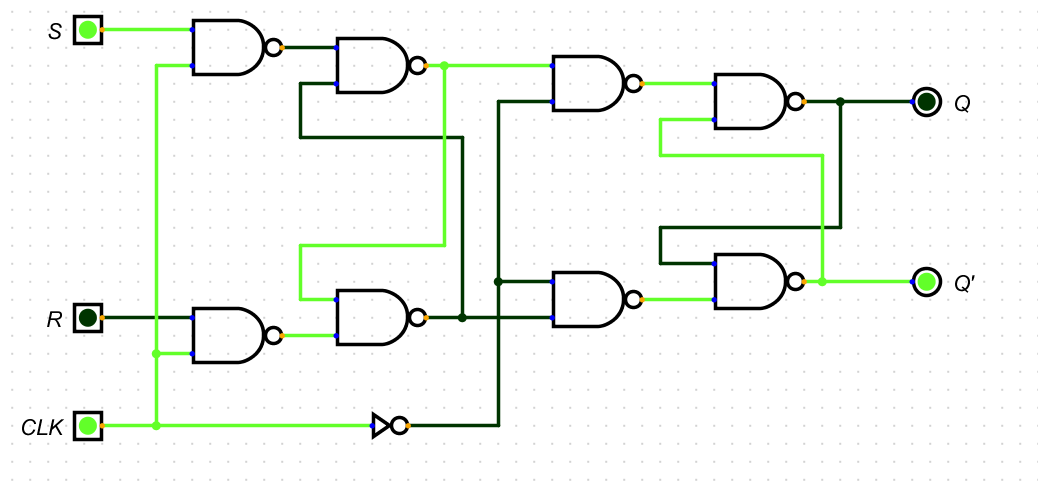

单步运行完所有门电路之后:

之后将CLK的高电平转换为低电平:

单步运行该电路,最终结果如下所示:

(2)之后将输入端R和CLK设置为高电平,输入端S设置为低电平:

单步运行完所有门电路之后:

然后将CLK的高电平变为低电平:

单步运行该电路,最终结果为:

(3)将输入端CLK设置为高电平,将S和R全部设置为低电平:

单步运行完所有门电路之后:

将CLK的高电平转换为低电平:

单步运行至最终结果为:

(4)然后,将输入端S、R和CLK全部设置为高电平:

单步运行完所有门电路之后:

将CLK转换为低电平:

单步运行后最终结果有两种情况,分别为:

可以看到,当S=R=1时,最终输出的情况为Q和Q'同零或者同一的输出,但符号SR触发器的输出情况。

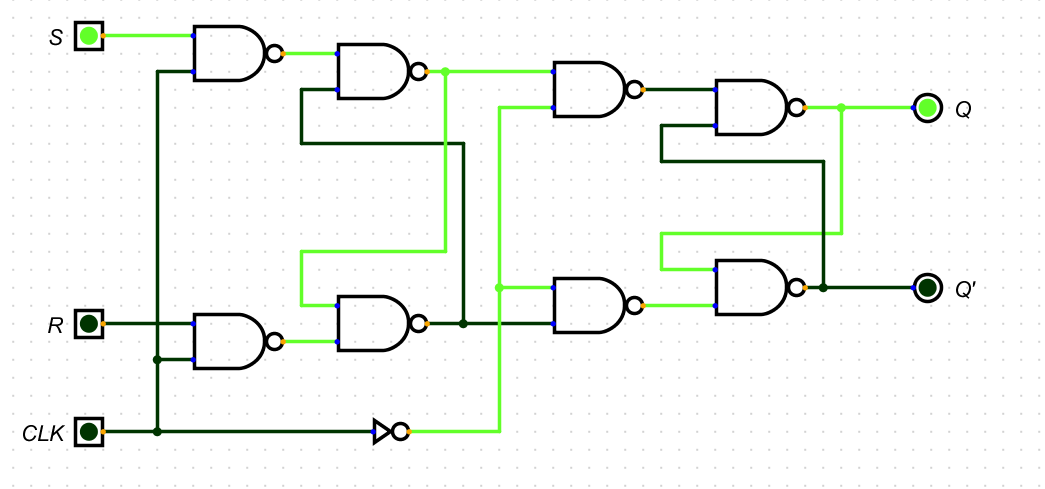

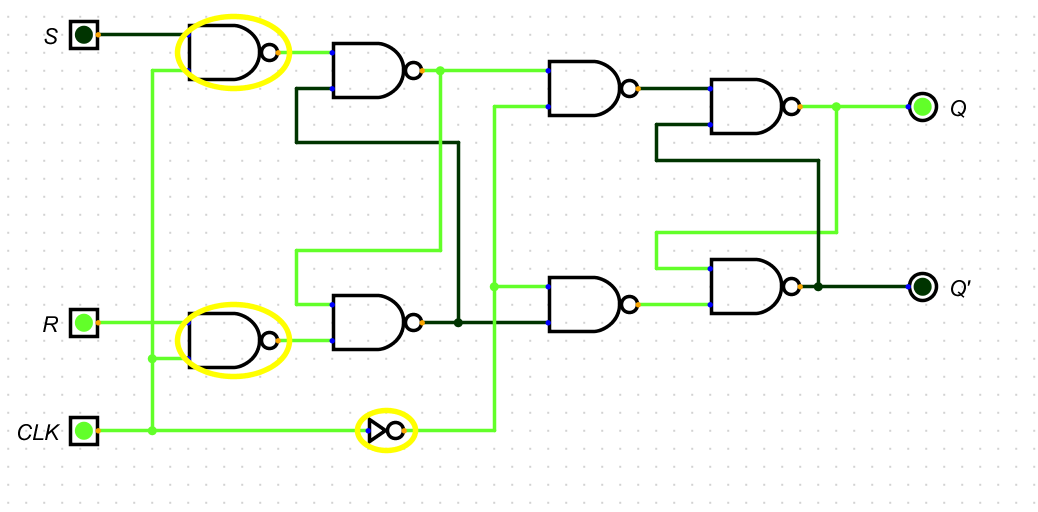

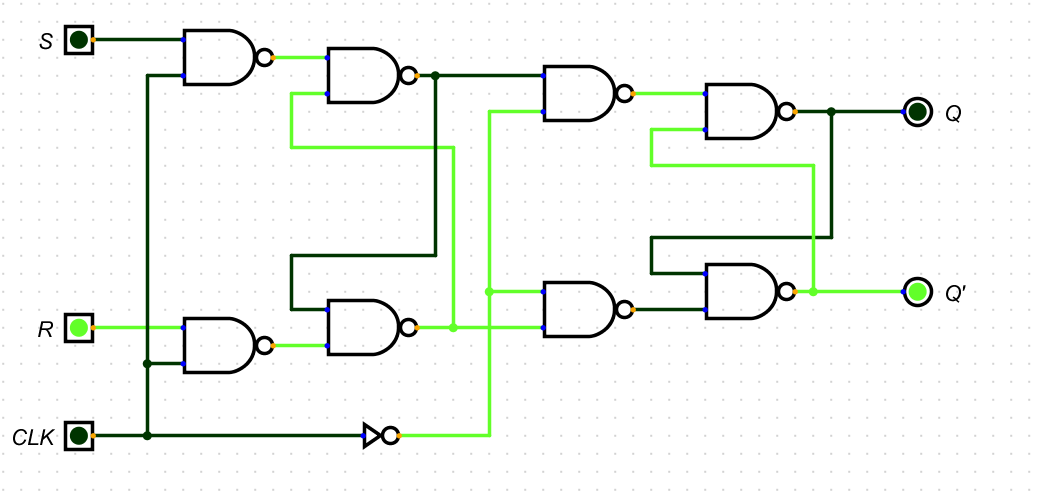

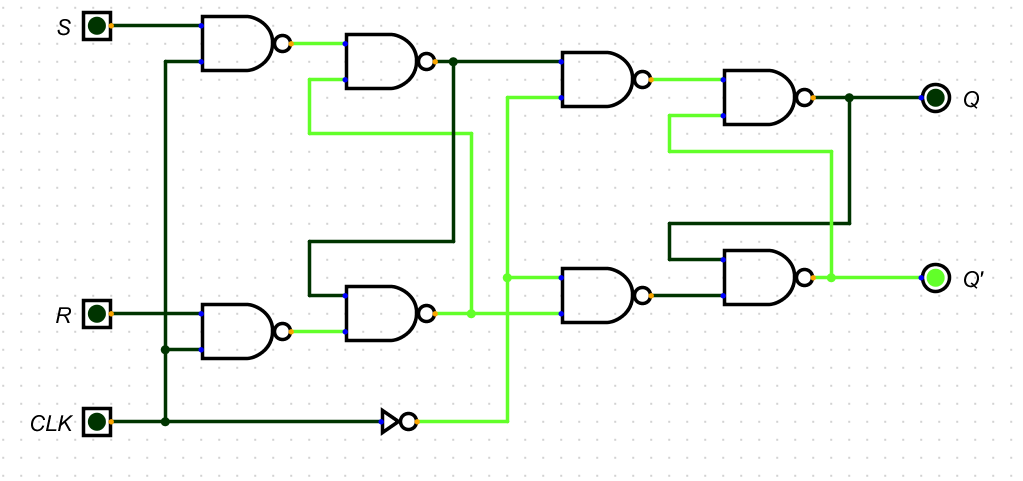

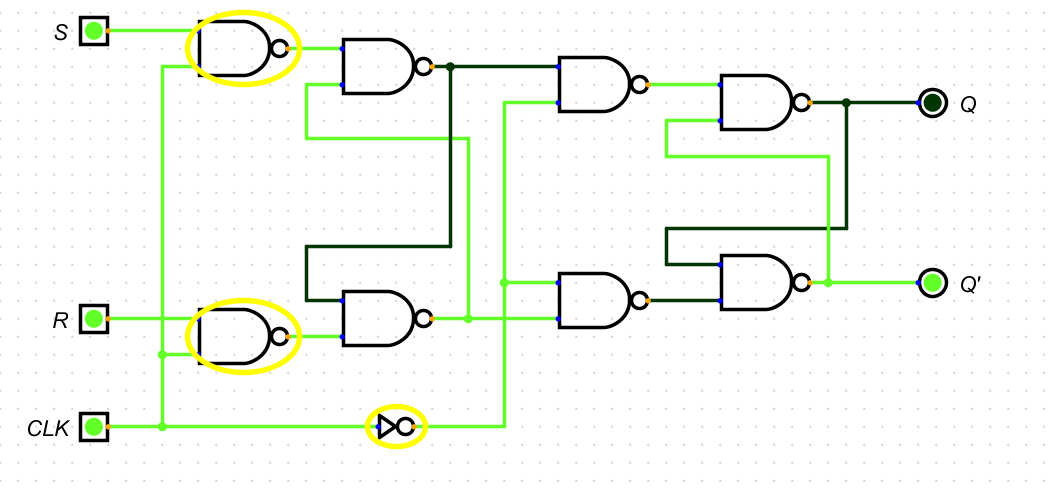

1.2 使用Digitial软件绘制脉冲触发的JK触发器

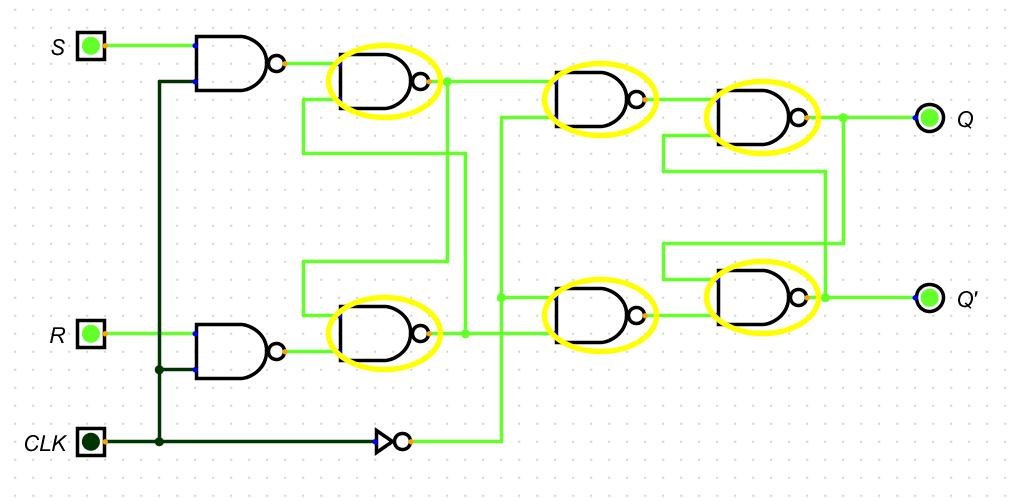

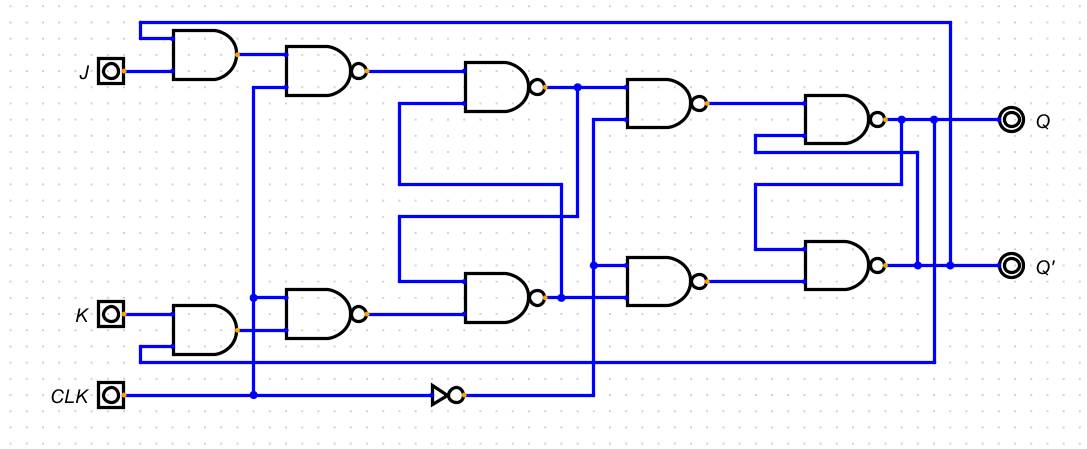

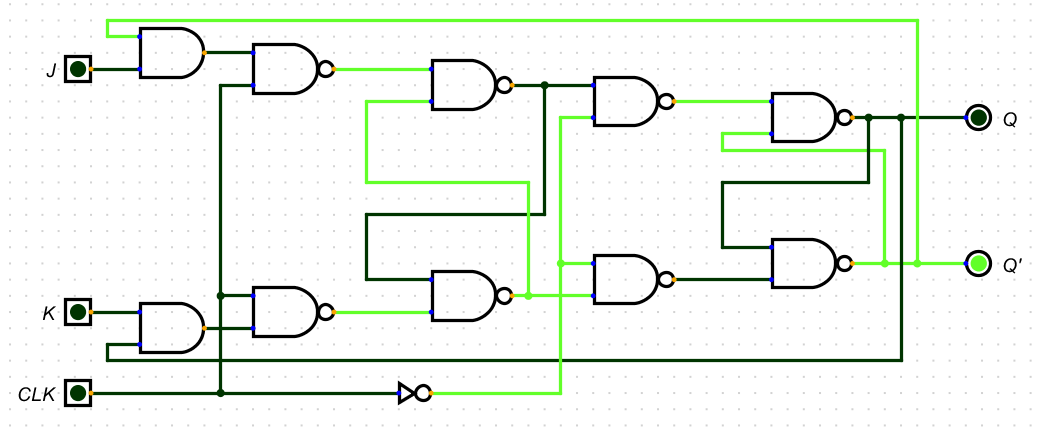

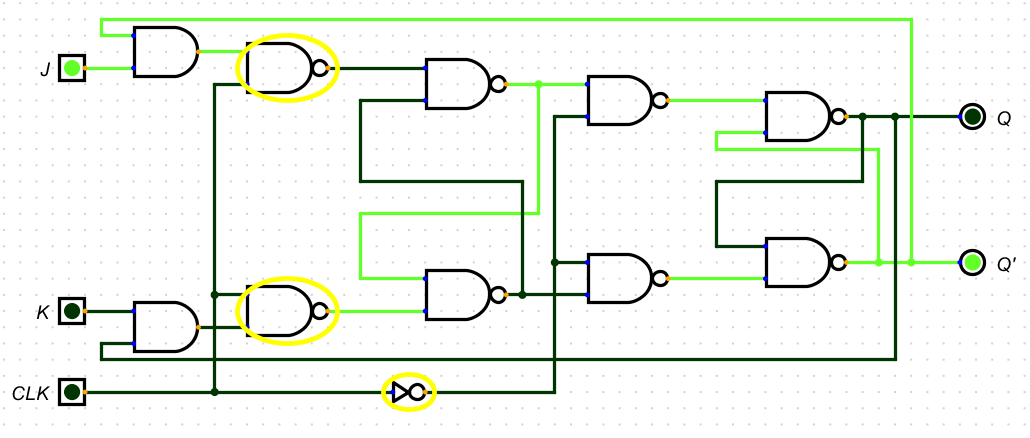

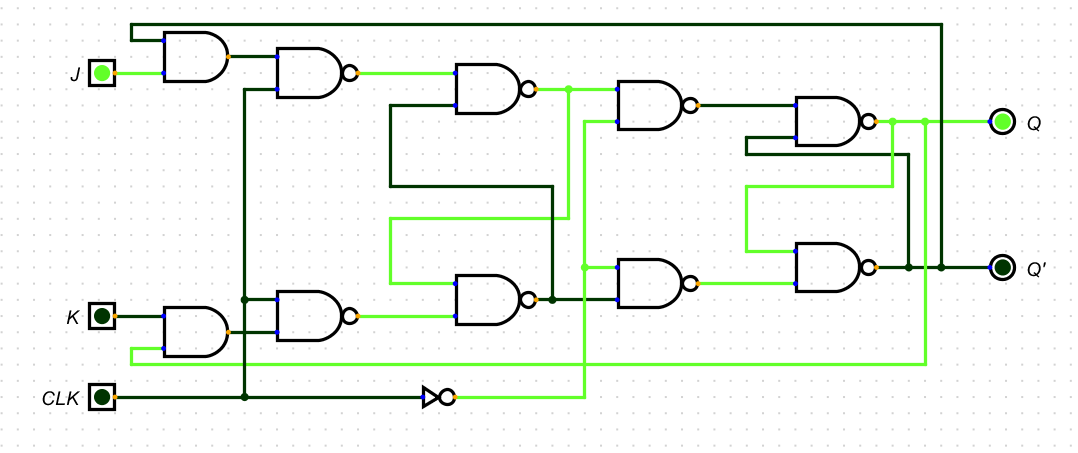

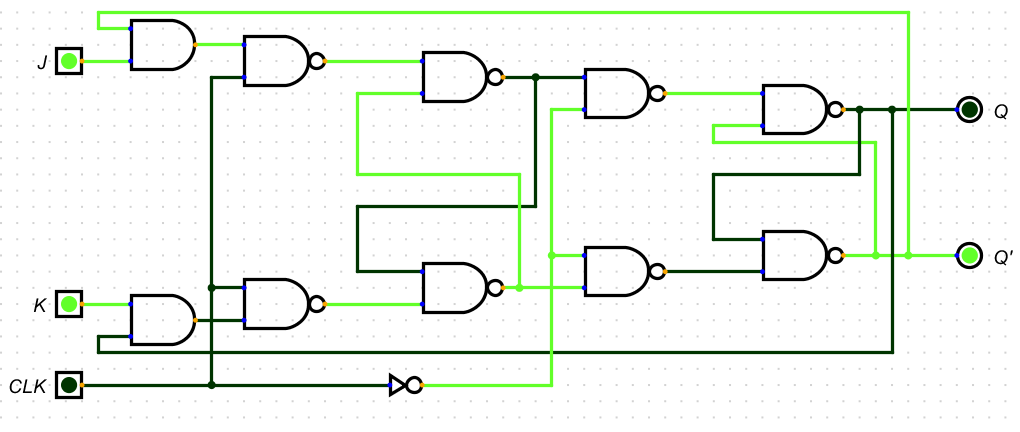

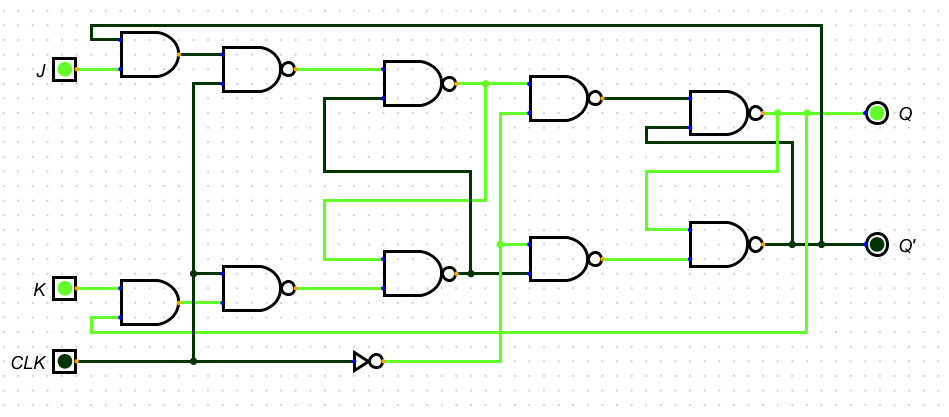

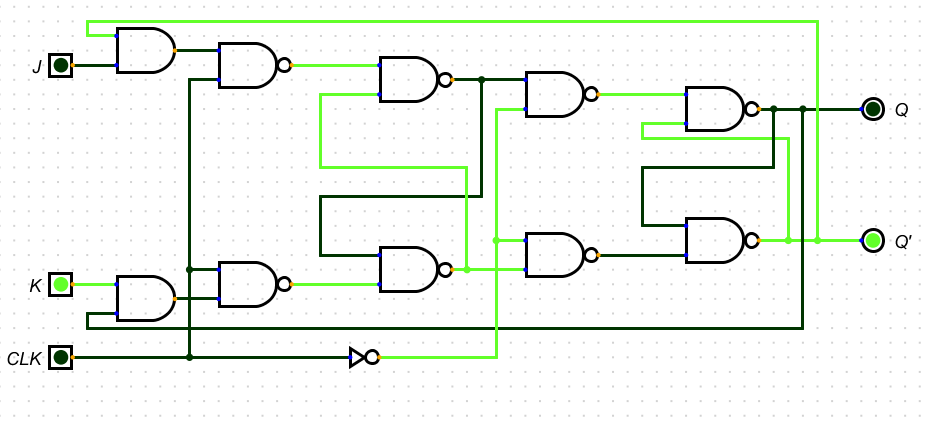

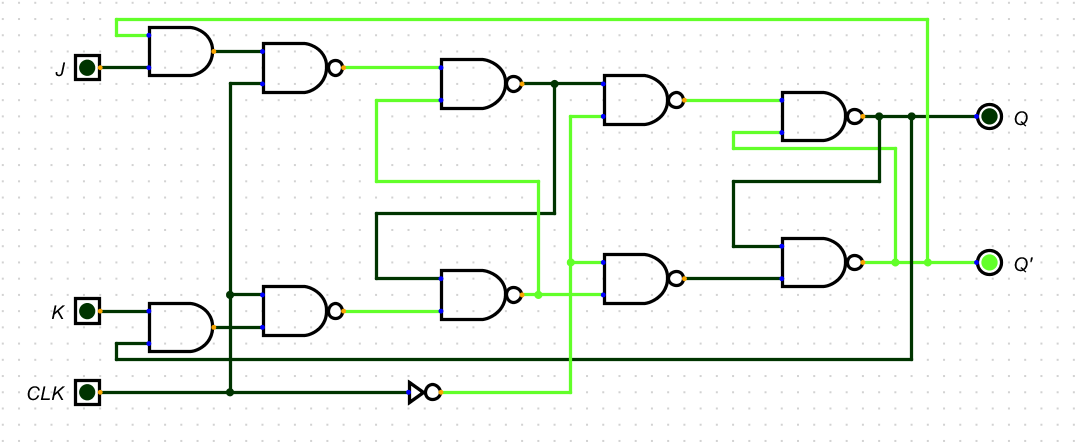

使用Digital软件绘制脉冲触发的JK触发器,电路图如下所示:

点击运行,初始状态如下所示:

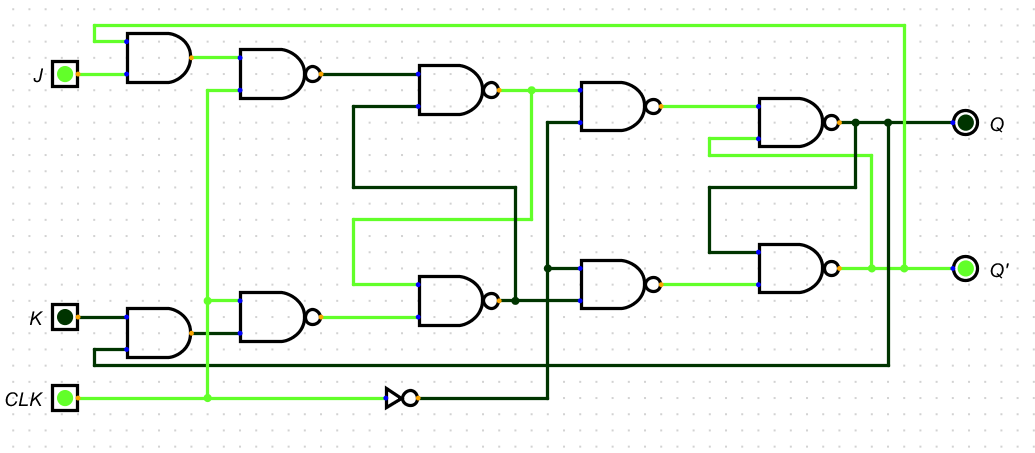

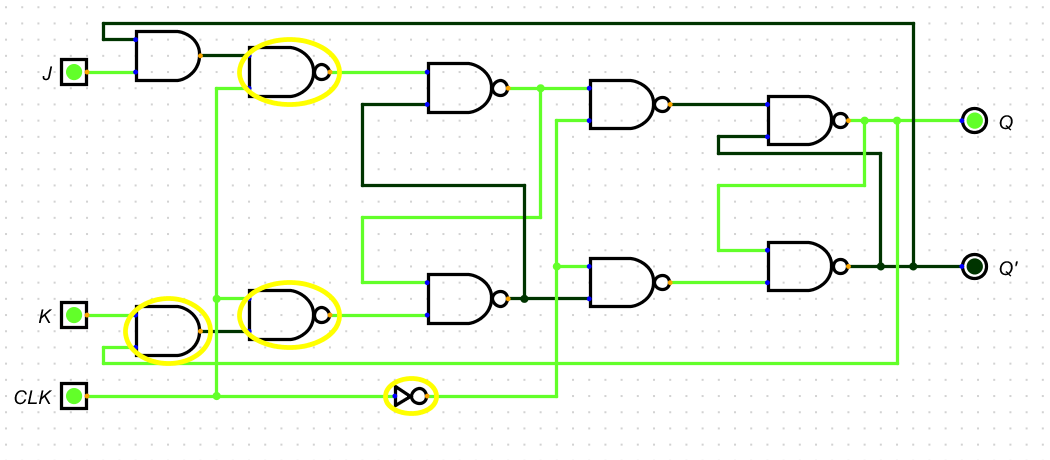

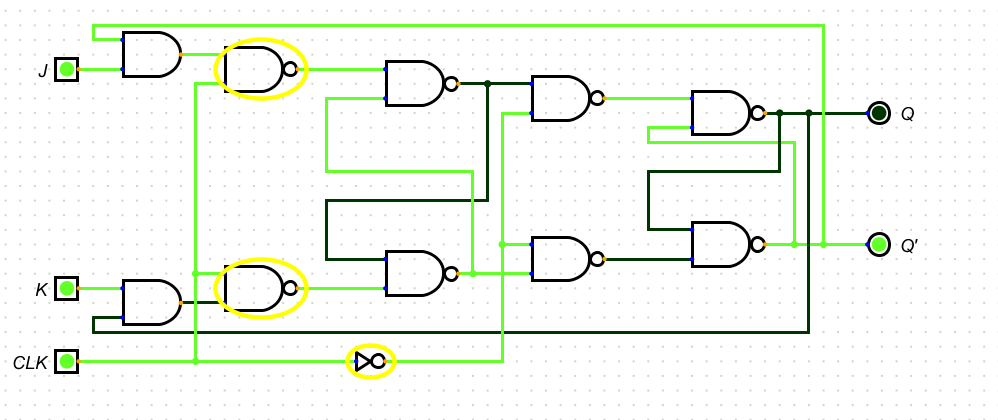

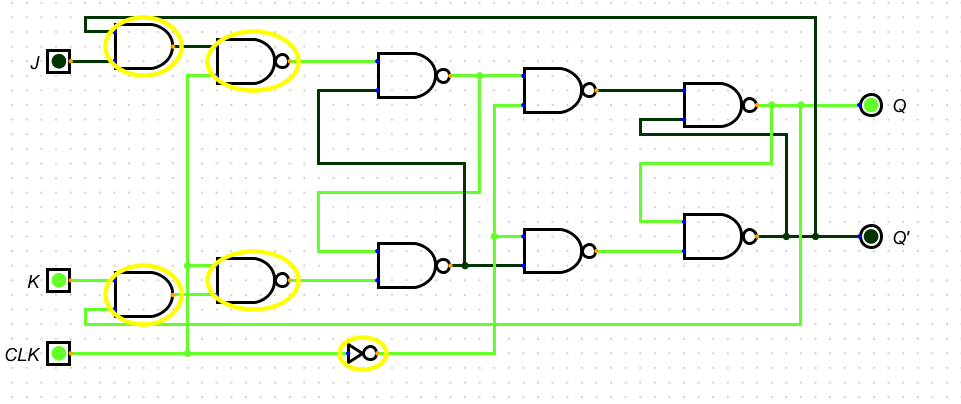

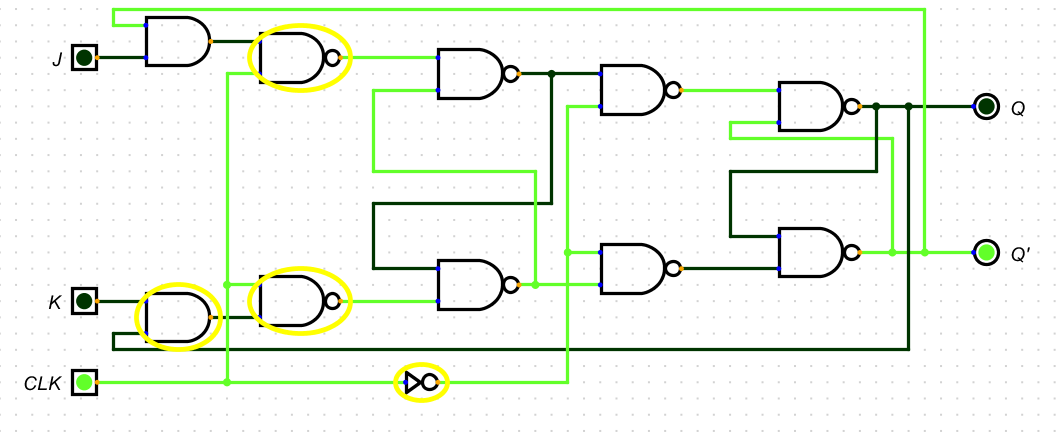

(1)下面开始使用单门仿真运行该电路,首先第一步点击仿真选项栏下面的单门仿真,首先将J置于1,K置于0,CLK置于1:

单步运行完所有门电路之后:

可以看到Q没有发生变化,但是中间部分门电路的高低电平发生了变化,这时候将CLK设置为低电平:

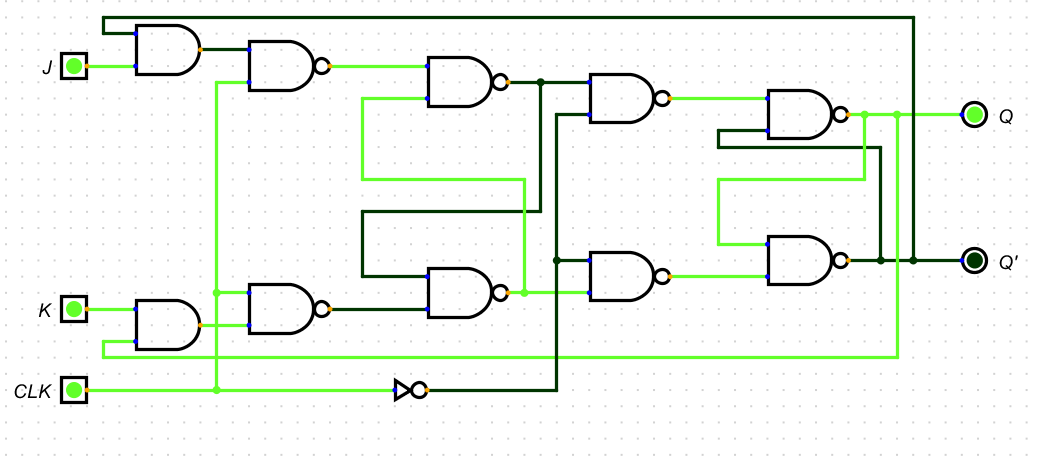

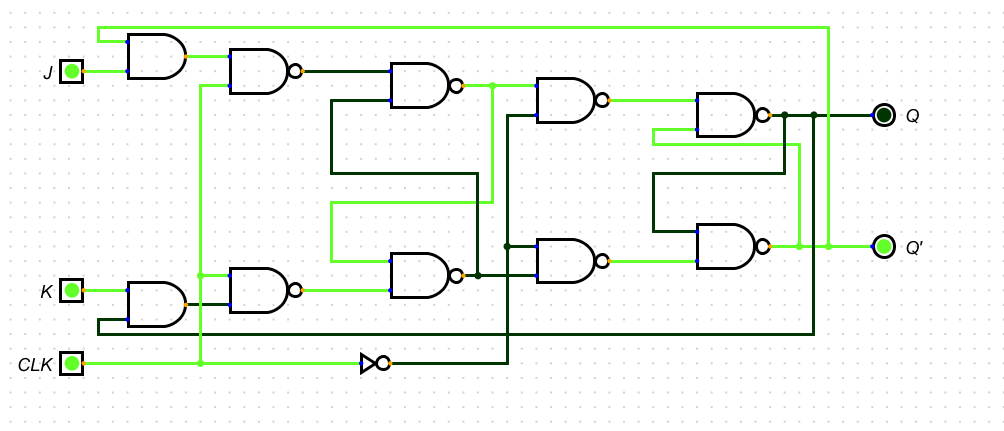

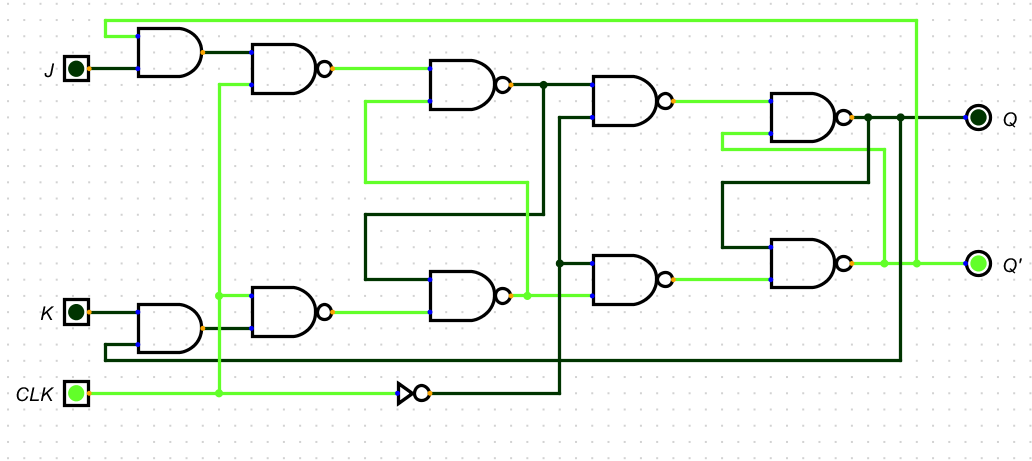

单步运行完所有的门电路如下所示:

可以看到Q由原来的低电平转换了高电平。

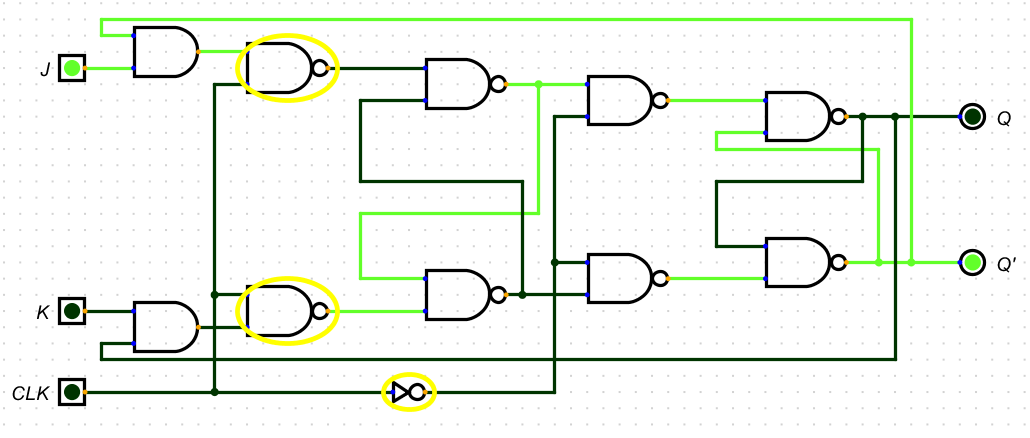

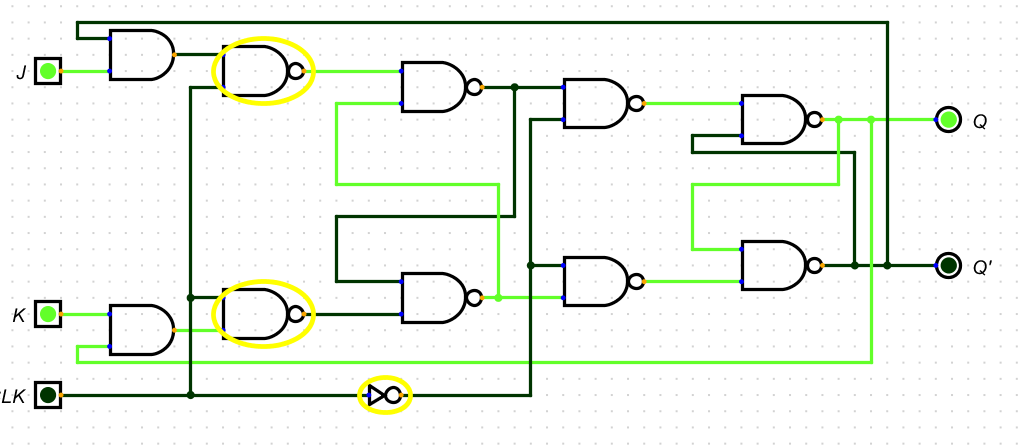

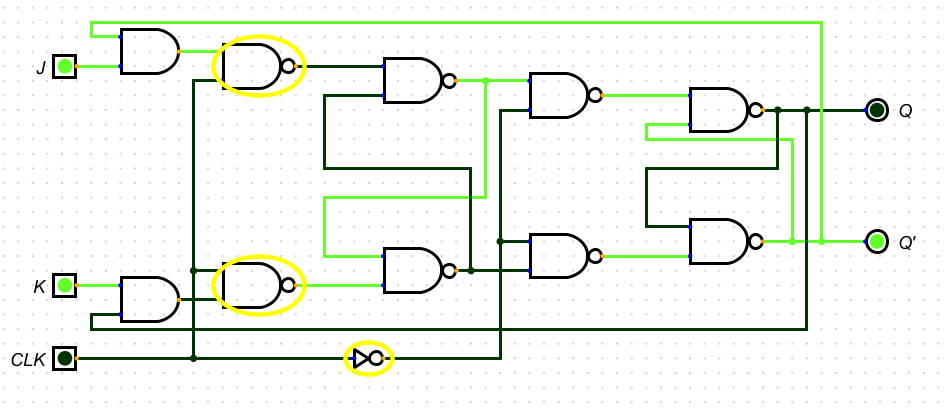

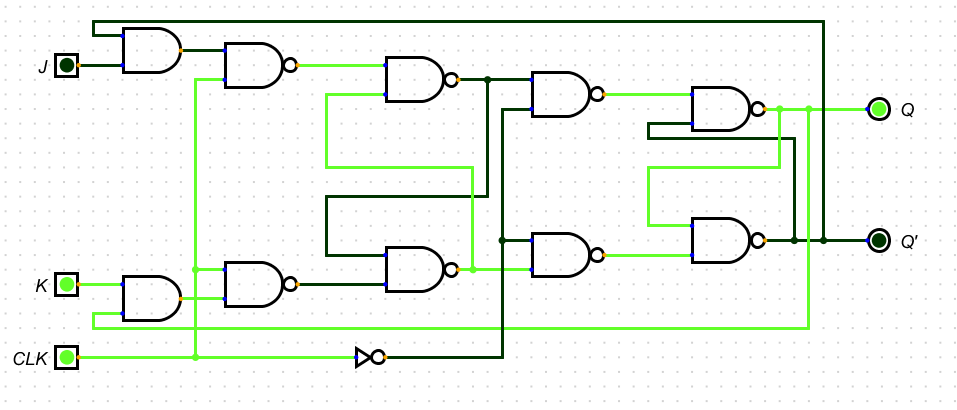

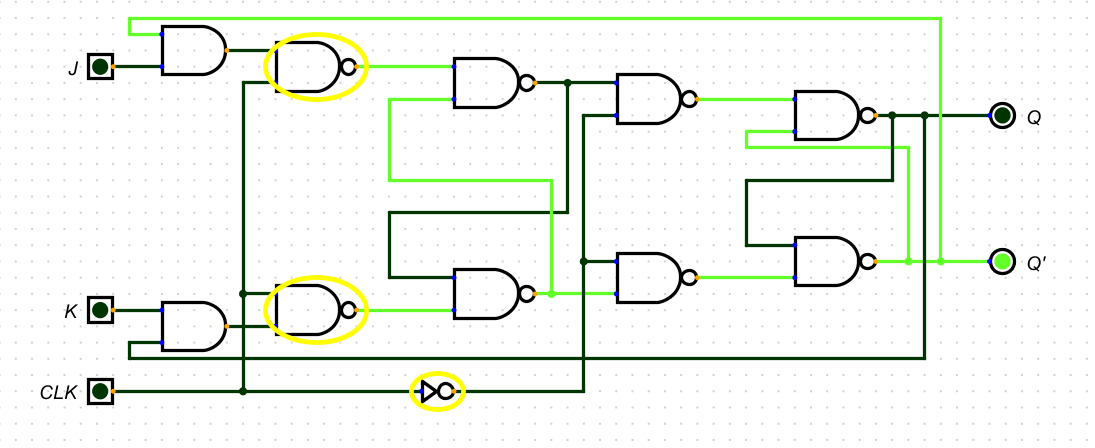

(2)下面将输入端J、K、CLK全部设置为高电平:

单步运行该电路如下所示:

可以看到主触发器做出了反应,而从触发器继续保持。

如果将CLK继续调整为低电平:

单步运行完所有的电路之后:

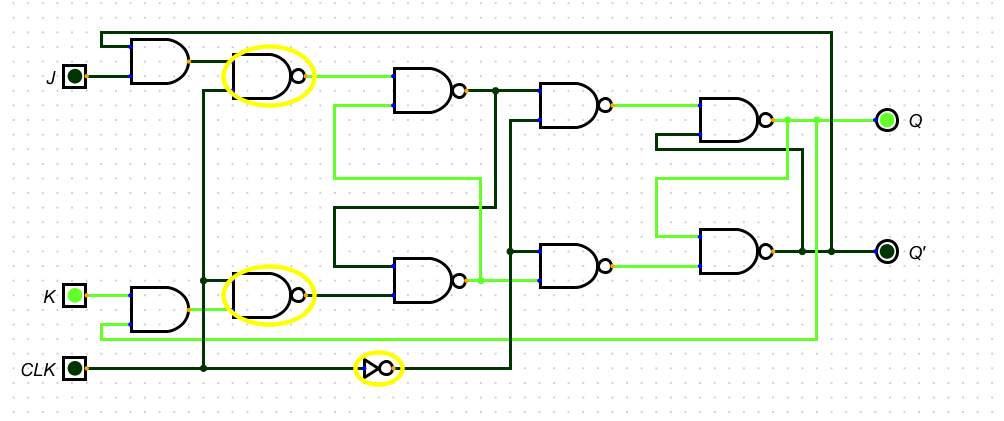

(3)继续调整该电路,将输入端J、K、CLK全部设置为高电平:

单步运行该电路,主触发器完成运行之后电路图如下所示:

此时将CLK设置为低电平:

单步运行之后结果如下所示:

可以看到当J=K=1时,完成了对于输出结果Q的翻转。

(4)将输入端置为0、J和CLK置为1,如下所示:

单步运行该电路如下所示:

可以看到此时只有主触发器做出了相应反应,从触发器继续保持。将CLK调整为低电平时:

单步运行该电路,最终结果为:

(5)将输入端J和K全部设置为低电平,然后将CLK设置为高电平:

单步运行完所有门电路之后:

然后将CLK调整为低电平,如下所示:

最终结果如下所示:

可以看到Q的输出结果保持,符号JK触发器的运算规律。

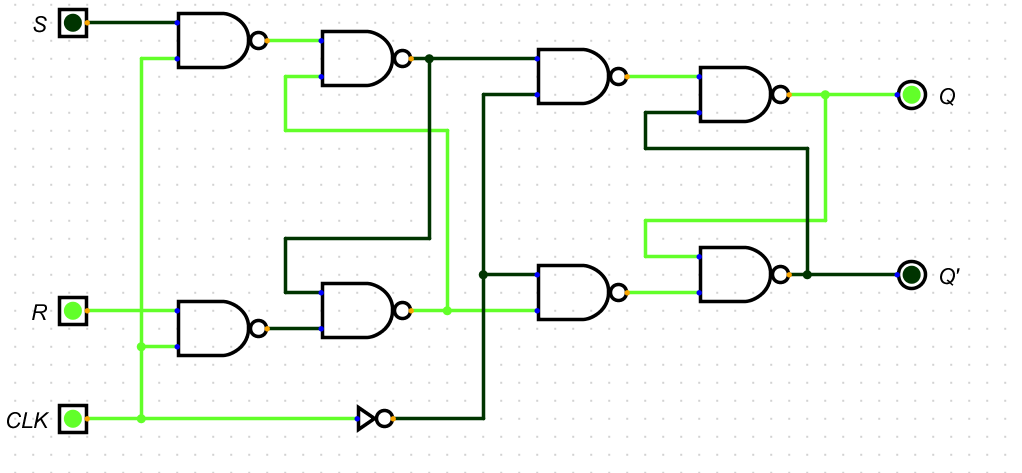

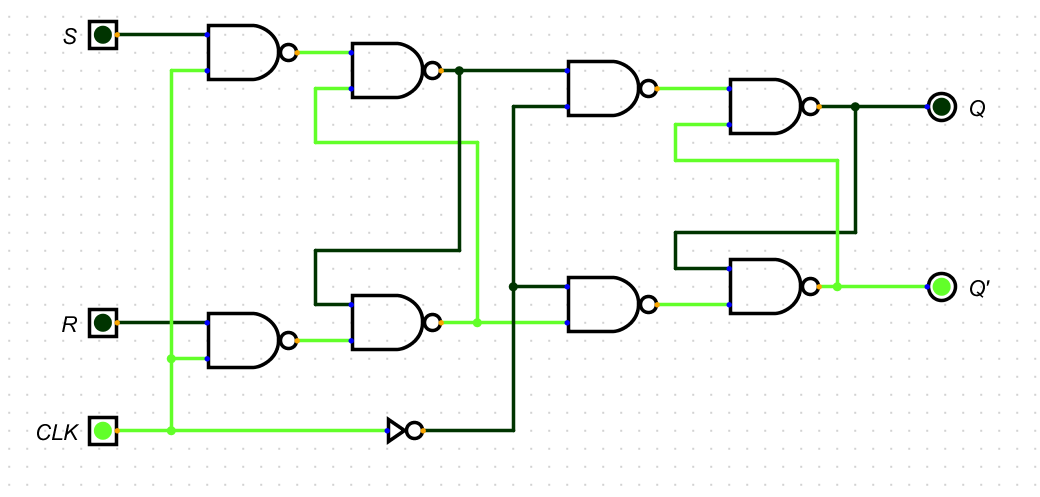

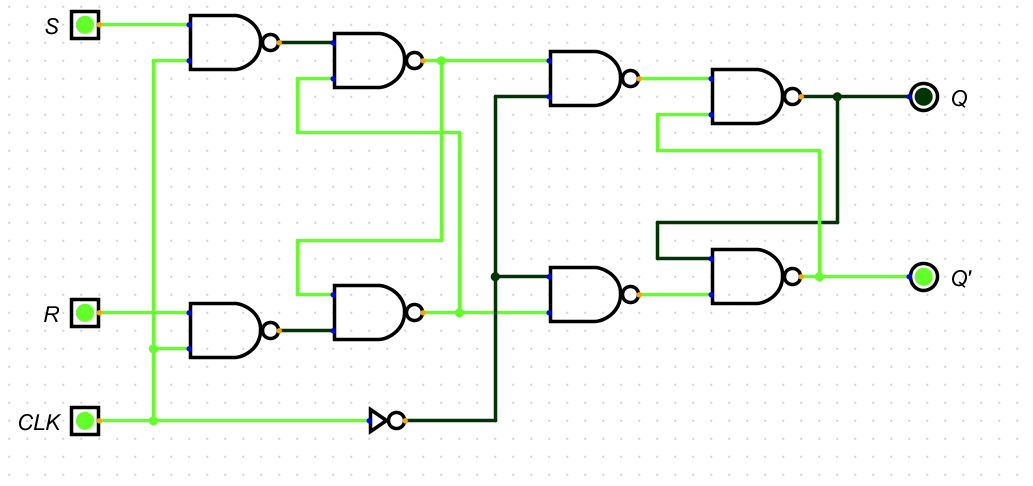

1.3 使用Digital软件绘制脉冲触发D触发器

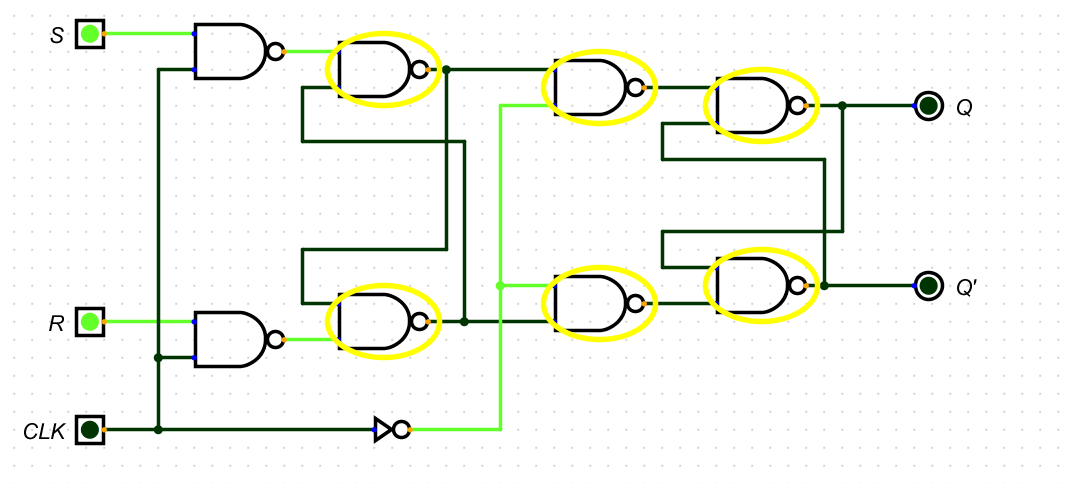

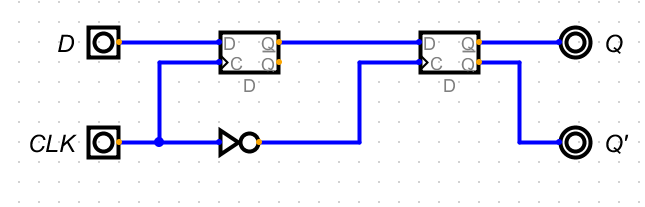

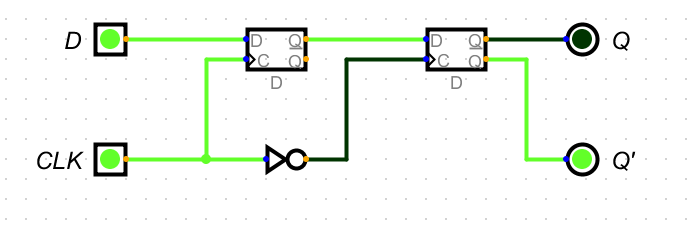

使用Digital软件来绘制脉冲触发的D触发器,电路图如下所示:

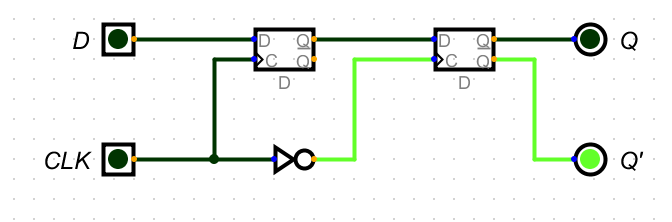

运行该电路图:

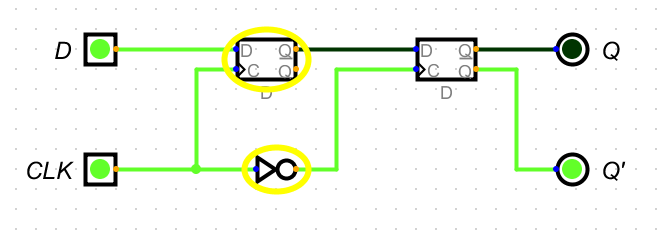

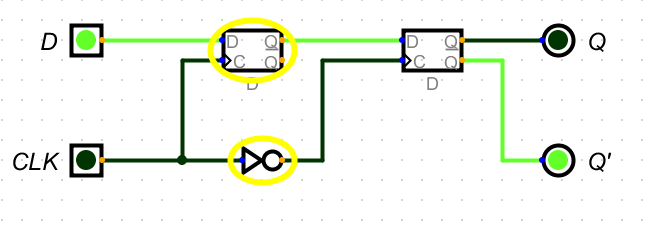

首先对于电路进行单步仿真,将输入端CLK和D全部设置为高电平:

执行完结果如下所示:

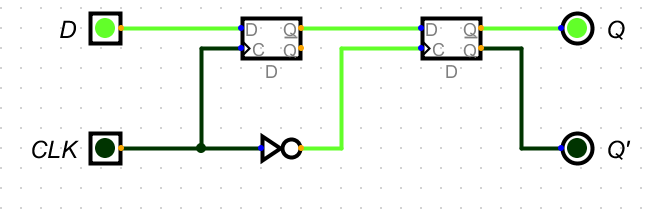

此时再将CLK接低电平:

单步执行该电路,最终结果如下所示:

可以看到Q由原来的低电平转换为高电平。