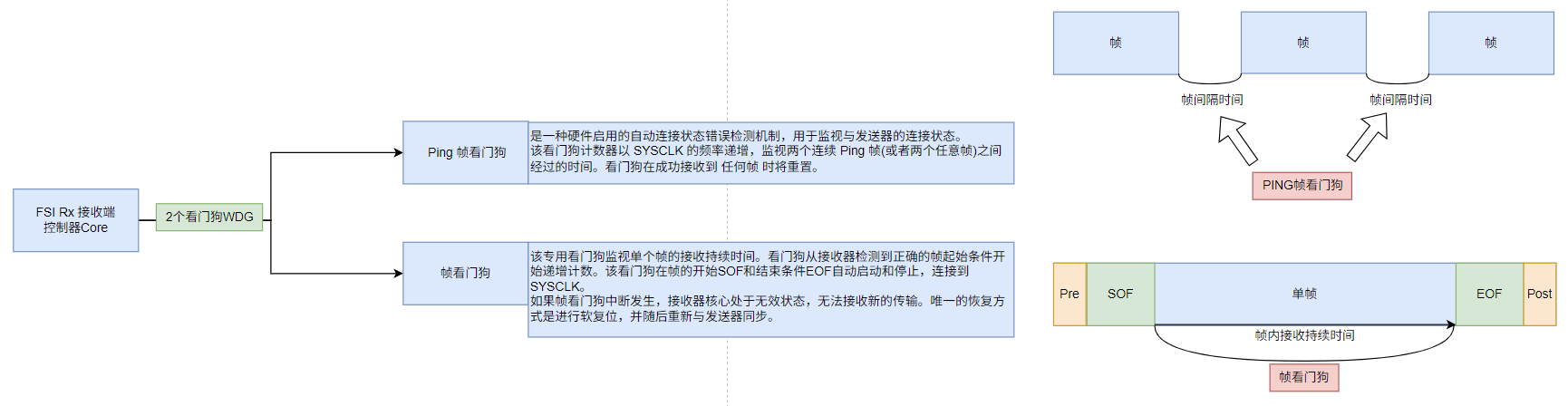

简介

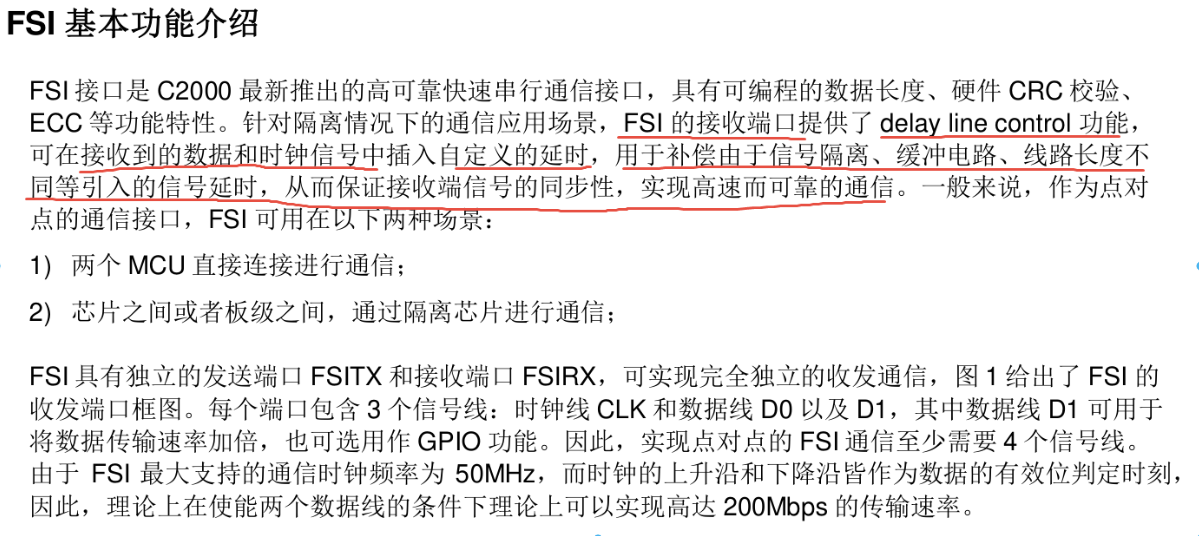

快速串行接口(FSI - Fast Serial Interface )模块是一种串行通信外设,能够在隔离设备 之间实现可靠的高速通信。在两个没有共同电源和接地连接的电子电路必须交换信息的情况下,电气隔离设备被使用。

虽然隔离设备促进了信号通信,但它们也会在信号线上引入较大的延迟,并增加信号之间的时序差异。FSI 专门设计用于确保系统在涉及隔离障碍的通信场景中进行可靠的高速通信,同时不添加额外的组件。

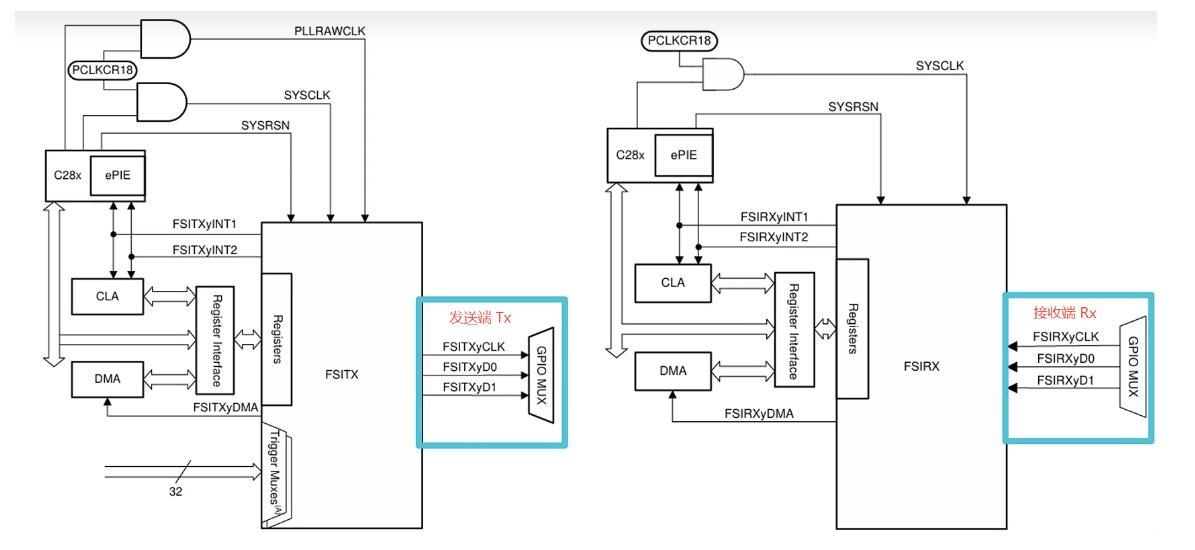

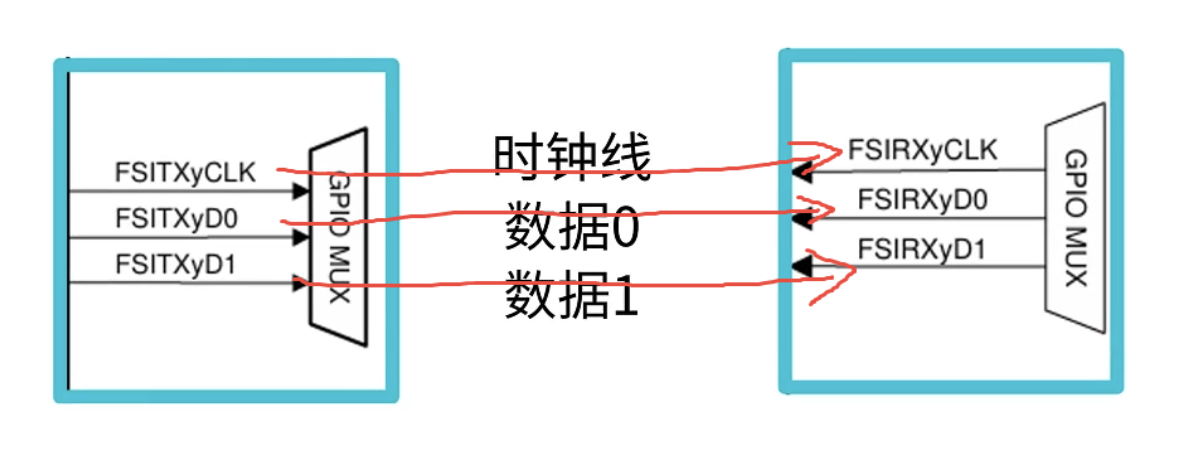

FSI 包括独立的发送器(FSITX)和接收器(FSIRX)核心。FSITX 和 FSIRX 核心可以独立配置和操作。

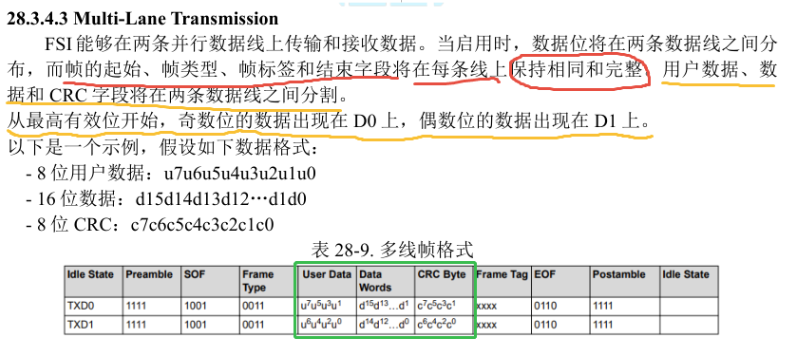

1、内部框架图

2、应用场景

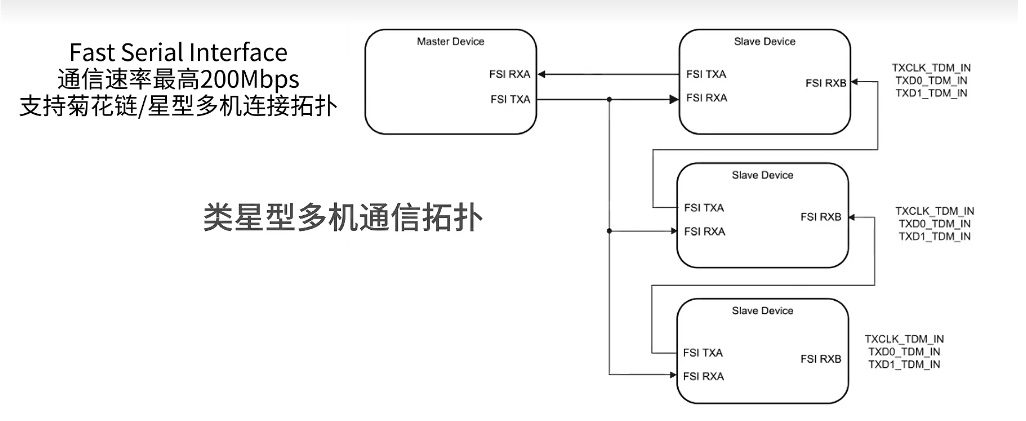

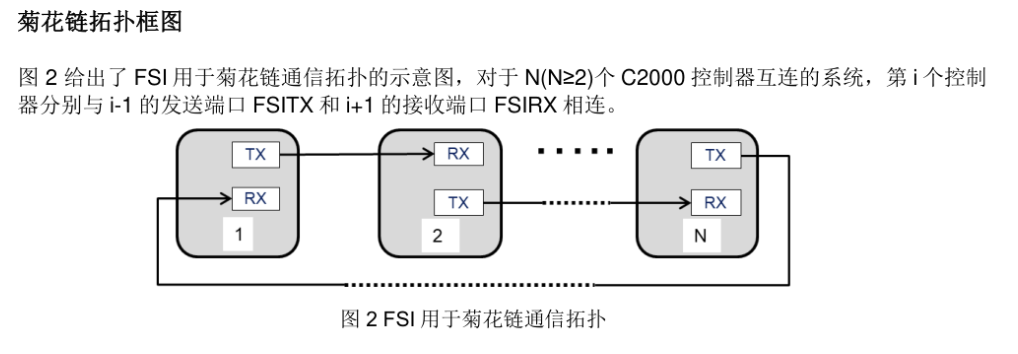

目前新一代 TI C2000:

F28004x 只提供 1 个发送端口和 1 个接收端口,只适用于菊花链拓扑 ;

F2838x 提供 2 个发送端口和 8 个接收端口,还可以用于实现一对多的星型拓扑。

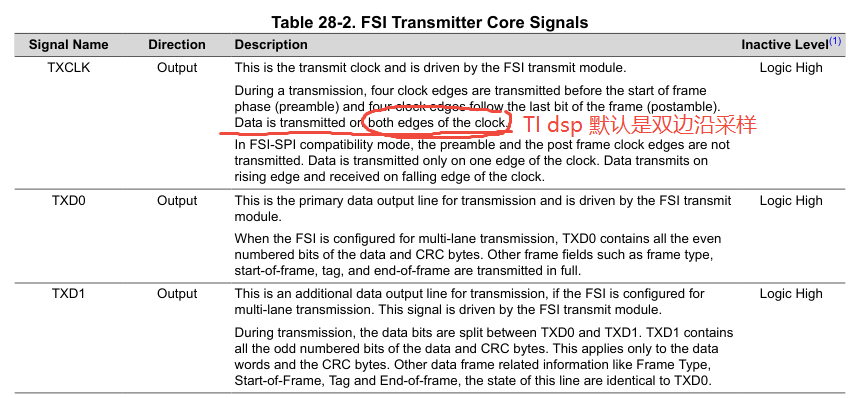

FSI - 数据采样

一个时钟周期内,有2个边沿(一个上升沿和一个下降沿),与硬件电气数据线的个数无关,而是与时钟clock周期脉冲的边沿相关。

(1) SDR (Single Data Rate)

-

采样方式 :仅在单一时钟边沿(上升沿或下降沿)采样数据。

-

数据吞吐量 :每周期传输1个数据。

(2) DDR (Double Data Rate)

-

采样方式 :在时钟的上升沿和下降沿均采样数据。

-

数据吞吐量 :每周期传输2个数据(速率翻倍)。

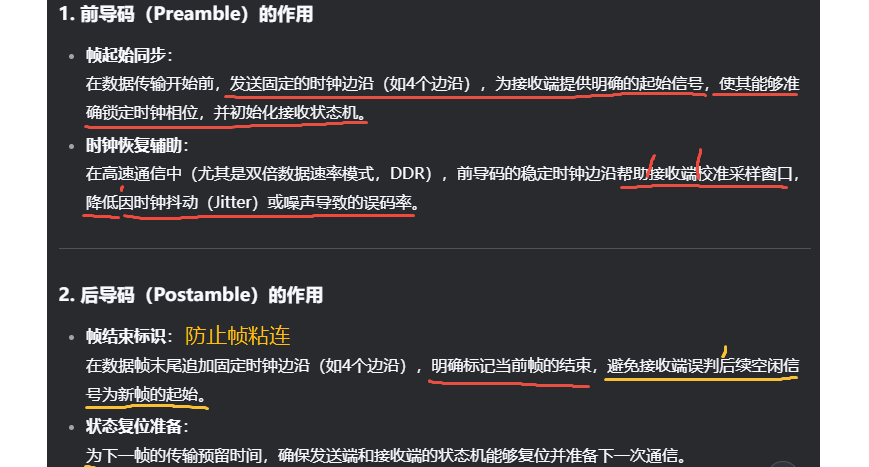

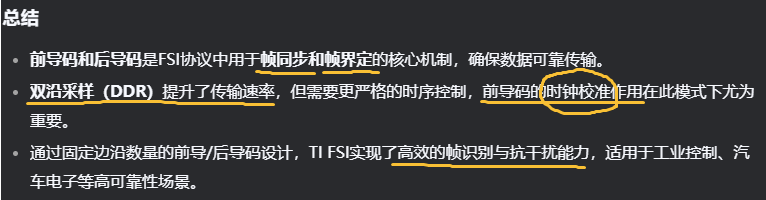

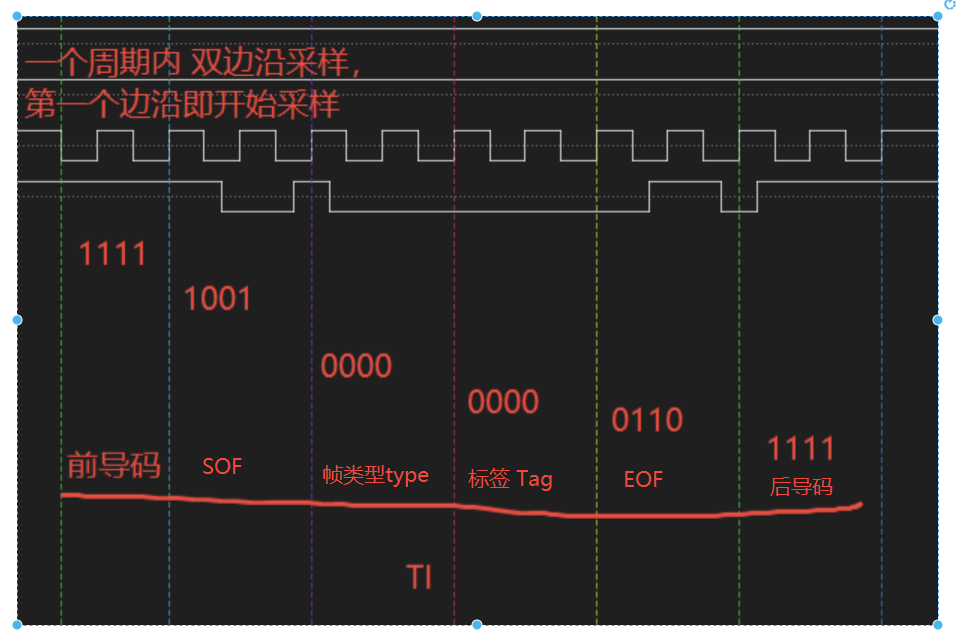

FSI - 前导码、后导码

前导码(1111)、后导码(1111)

|------------|---------------------|-------------------------------------|

| 前导码 | 接收端如何识别帧的开始? | 发送固定模式的时钟边沿(如4个边沿),接收端检测到此模式即触发帧接收。 |

| 后导码 | 如何避免帧间数据粘连或噪声误触发? | 发送固定结束信号,接收端在检测到后导码后停止采样并等待下一帧前导码。 |

| 双沿采样 | 如何提高数据传输速率? | 在时钟的上升沿和下降沿均传输数据(DDR模式),带宽翻倍。 |

| 边沿计数同步 | 如何确保发送端和接收端的时钟相位对齐? | 前导码的固定边沿数作为同步基准,接收端据此调整采样窗口。 |

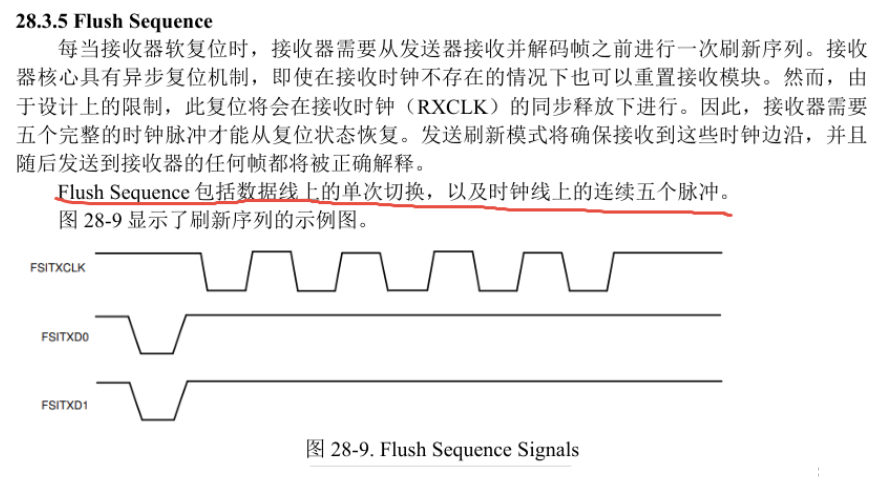

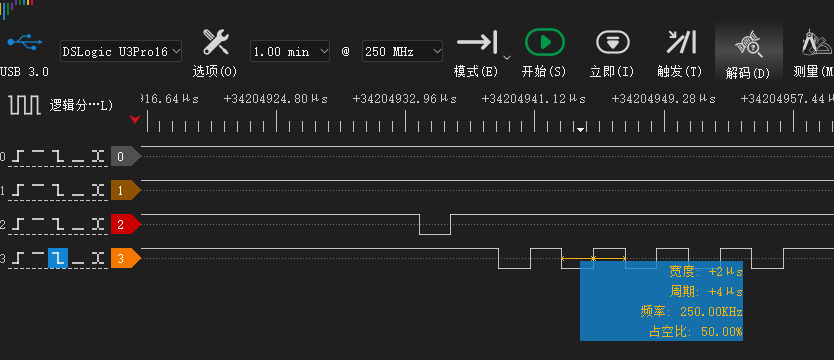

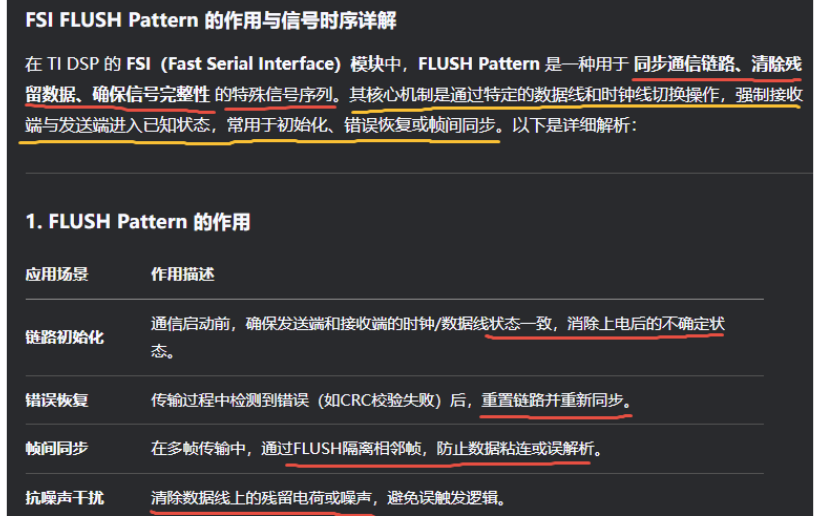

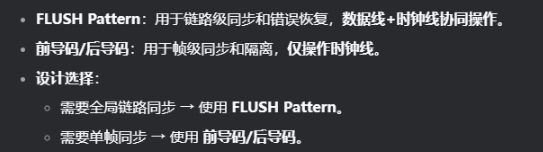

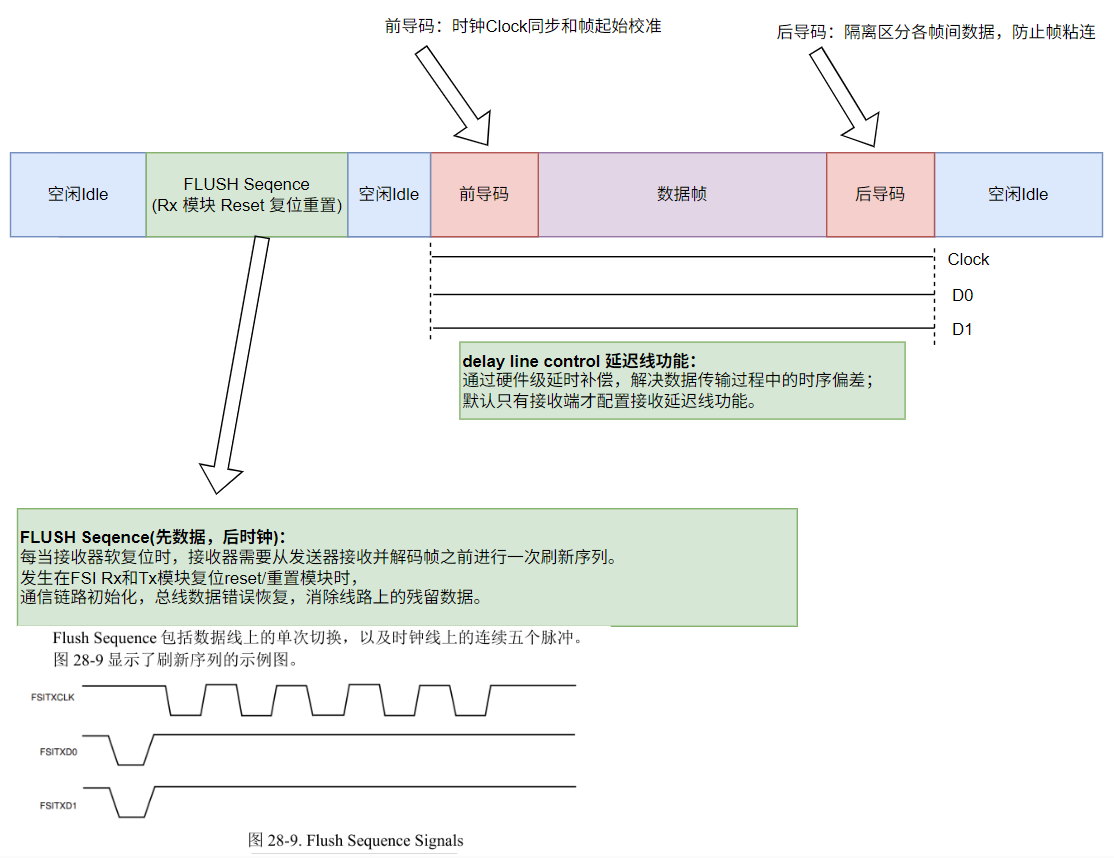

FSI - FLUSH sequence

Flush核心:信号翻转,先数据,后时钟。

实际抓取的波形:

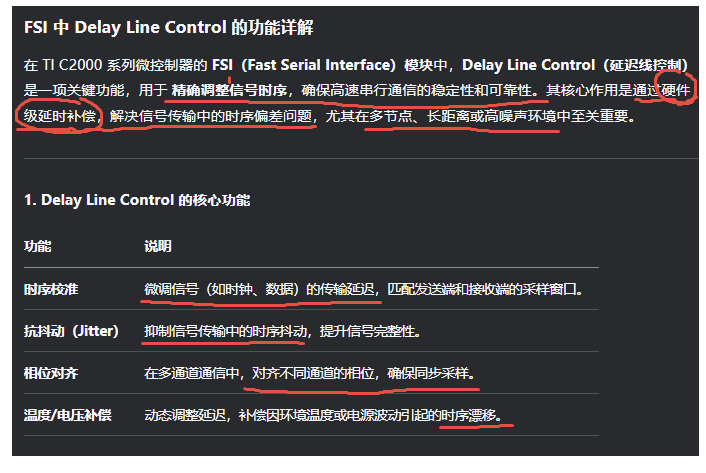

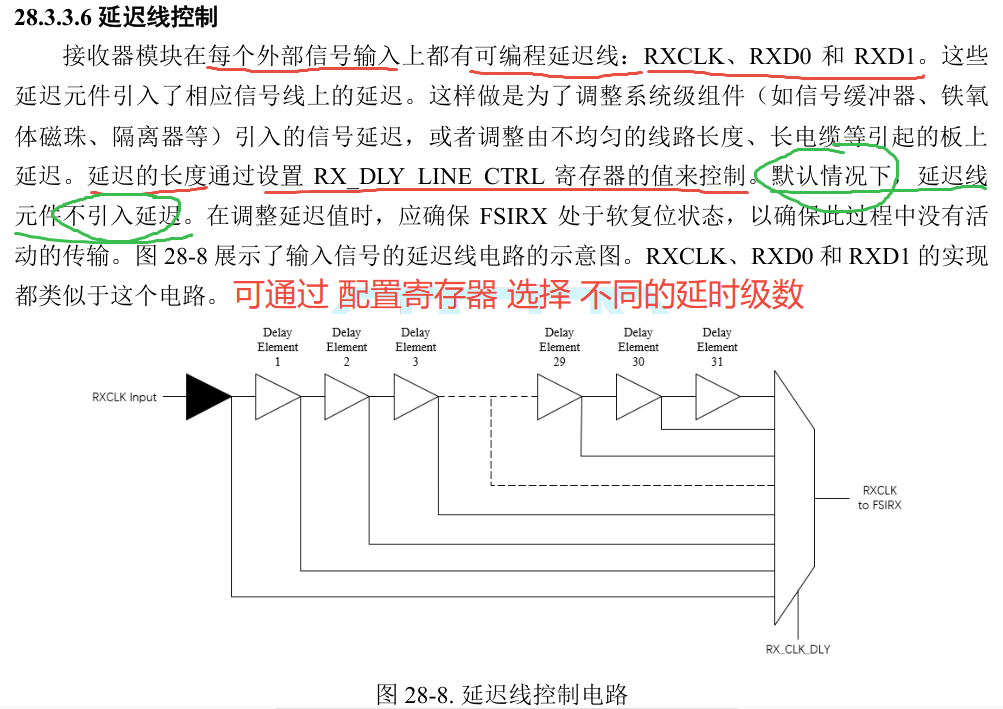

FSI - 线延迟

delay line control 延迟线功能:

FSI - 前、后导码和Flush区别

FLUSH 链路同步 是指通过特定的信号序列(FLUSH Pattern)强制发送端与接收端的时钟和数据状态对齐 ,以确保通信链路处于已知且稳定的初始状态。

区别:

| 对比项 | FLUSH Pattern | 前导码(Preamble) | 后导码(Postamble) |

|---|---|---|---|

| 核心目的 | 链路同步与状态复位 | 帧起始同步 | 帧结束标识 |

| 触发时机 | 初始化、错误恢复、帧间空闲时 | 每个数据帧传输前 | 每个数据帧传输后 |

| 信号类型 | 数据线 + 时钟线协同切换 | 仅时钟边沿 | 仅时钟边沿 |

| 时序特征 | 数据线先切换,时钟线后切换 | 固定时钟边沿(无数据) | 固定时钟边沿(无数据) |

| 典型应用场景 | 通信链路初始化、错误恢复、清除残留数据 | 帧同步、时钟相位校准 | 隔离帧间数据,防止粘连 |

| 配置参数 | 数据线切换次数、时钟边沿数 | 时钟边沿数 | 时钟边沿数 |

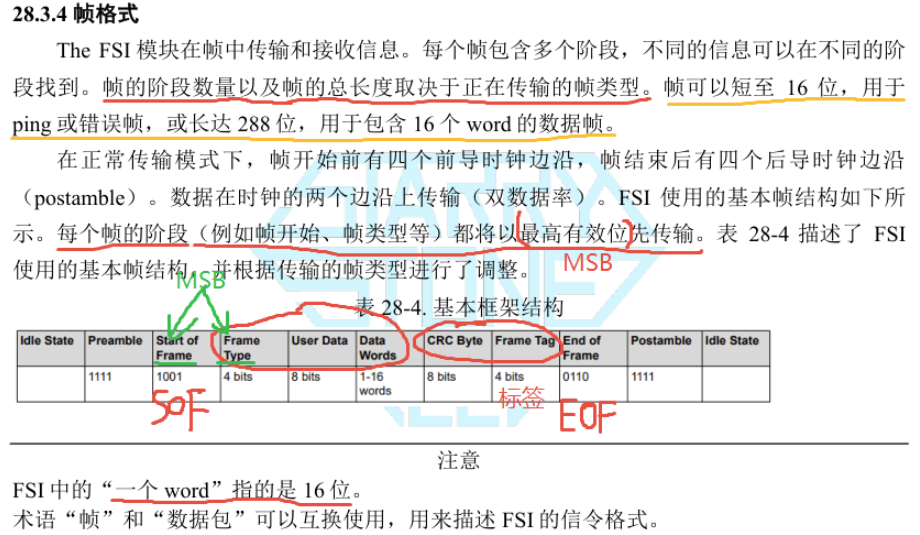

FSI - 帧格式

eg:

PING帧 TAG0

以下是帧结构的不同阶段详细描述:

Idle State

在 Idle State 下,时钟 clk 和数据线D0、D1 默认都保持高电平,即非活动状态。

Preamble

前导码阶段包含四个时钟边沿(或两个完整时钟脉冲),数据信号保持高电平。这些

时钟边沿用于清空接收逻辑,并准备接收新的帧 。

Start of Frame

包含两个时钟脉冲(4个边沿,产生4bit的数据),数据线上传输四位数据"1001"。

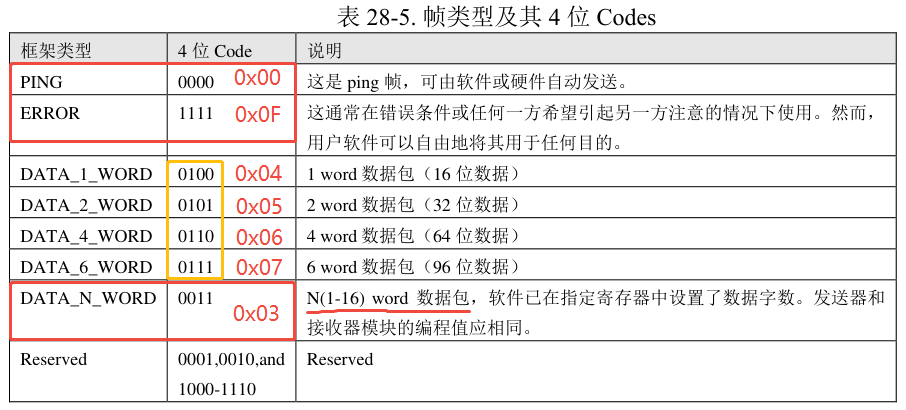

Frame Type

Frame Type 包含两个时钟脉冲,传输帧类型的 4 位编码到数据线上。在发送帧之前,发射机必须设置 TX_FRAME_CTRL.FRAME_TYPE字段。接收到的帧类型存储在RX_FRAME_INFO.FRAME_TYPE 中。

User Data

User Data 阶段包含完全可配置的用户数据字段。对该字段的使用没有限制。此阶段仅适

用于数据帧。要发送的用户数据通过写入 TX_FRAME_TAG_UDATA.USER_DATA 设置。接

收到的用户数据存储在 RX_FRAME_TAG_UDATA.USER_DATA 中。

Data

Data 阶段包含正在传输的数据。数据从发射机的发送缓冲区中提取,并将放置在接收机

的接收缓冲区中,第一个 word 首先传输。此阶段仅存在于数据帧中,根据发送的帧类型不同,

此阶段可以包含从 1 到 16 个 word。关于数据帧的更多信息可以在第 28.3.4.2.3 节中找到。

CRC Byte

CRC Byte 包含传输数据的 CRC。此阶段的值可以基于硬件或软件,具体取决于

TX_OPER_CTRL_LO.SW_CRC 位的设置。有关 CRC 如何在发送机和接收机模块中生成或使

用的更多信息,请参阅 CRC 子模块的模块特定部分。CRC 字节仅存在于数据帧中。

Frame Tag

Frame Tag 包 含 4 位 用户定义的帧标签。对于数据帧,发射机将此标签提供给

TX_FRAME_TAG_UDATA.FRAME_TAG 位。Ping 帧使用 TX_PING_TAG.TAG 中定义的标签。

接收机可以在 RX_FRAME_TAG_UDATA.FRAME_TAG 中访问接收到的帧标签。

End of Frame

包含四个时钟边沿,数据线上传输四位数据"0110"。

Postamble

包含额外的四个时钟边沿,数据线保持高电平。在后导码后,时钟和数据线将

被驱动到它们的非活动状态,保持高电平。

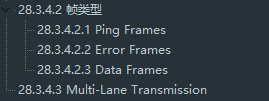

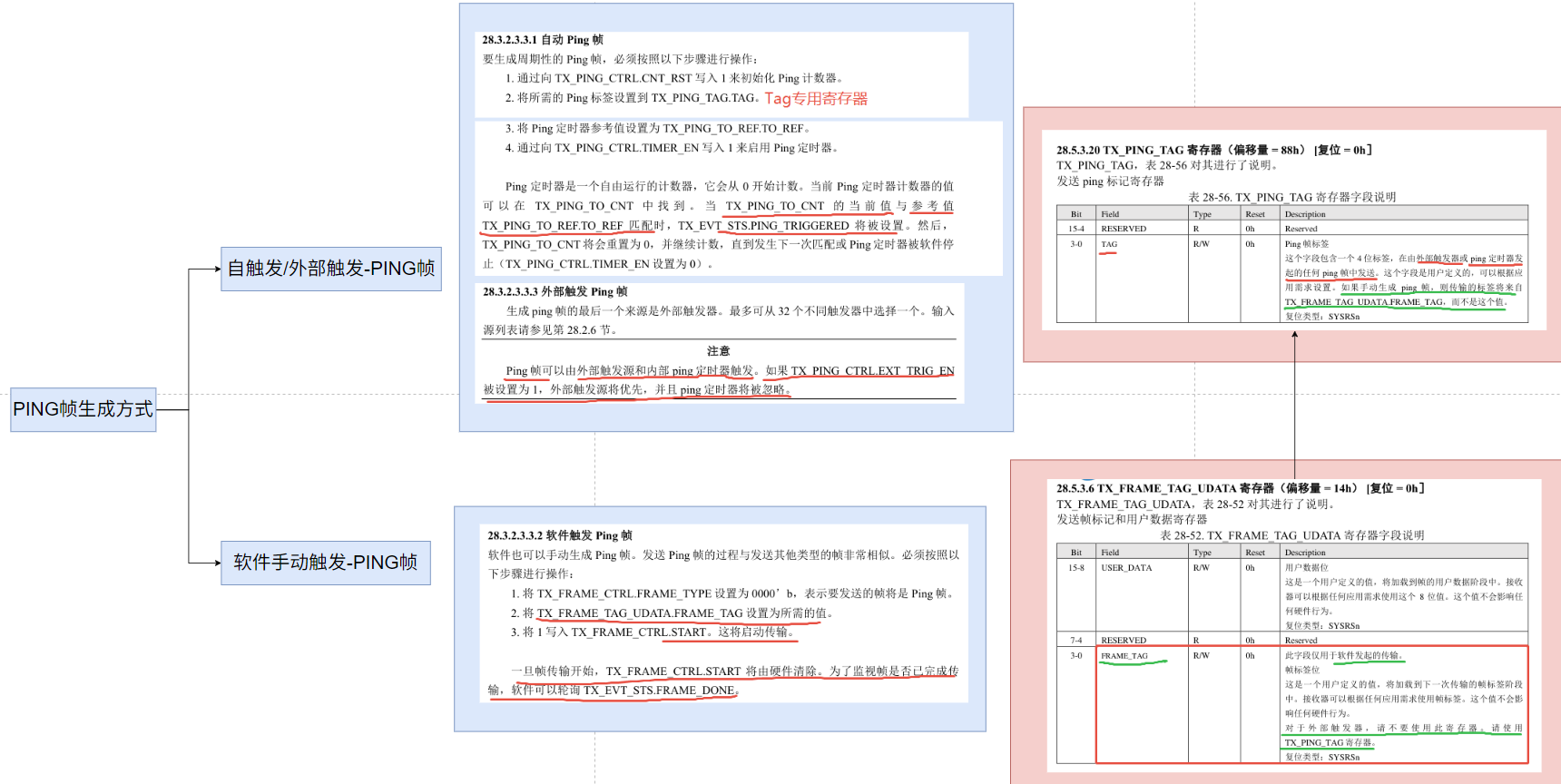

FSI - 帧类型

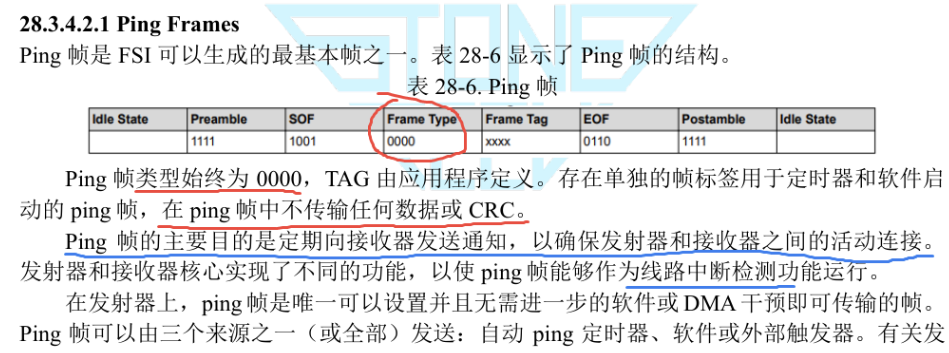

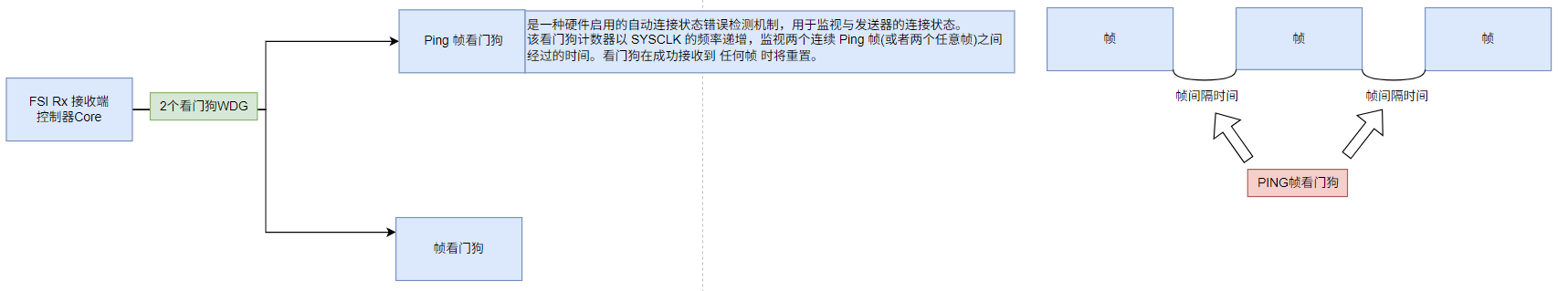

PING帧

cpp

//

// Send the flush sequence

//

FSI_executeTxFlushSequence(FSITXA_BASE, PRESCALER_VAL);

//

// Send a ping frame with frame tag

//

void FSI_txPingFrame(FSI_FrameTag frameTag)

{

FSI_setTxFrameTag(FSITXA_BASE, frameTag);

FSI_setTxFrameType(FSITXA_BASE, FSI_FRAME_TYPE_PING);

FSI_startTxTransmit(FSITXA_BASE);

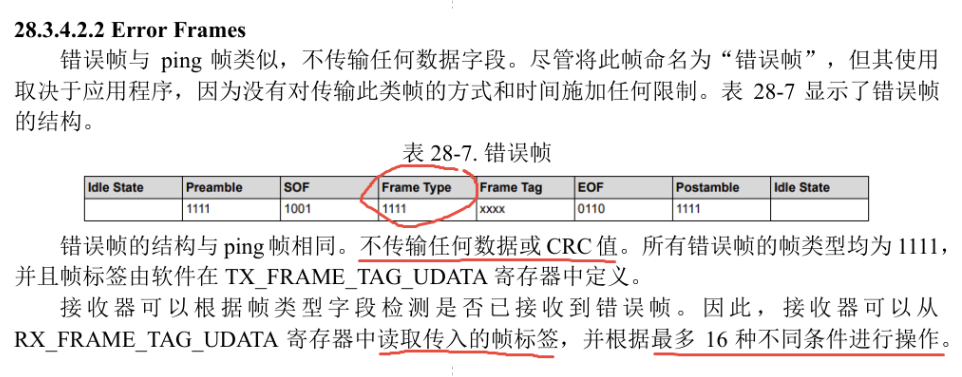

}错误帧

'

'

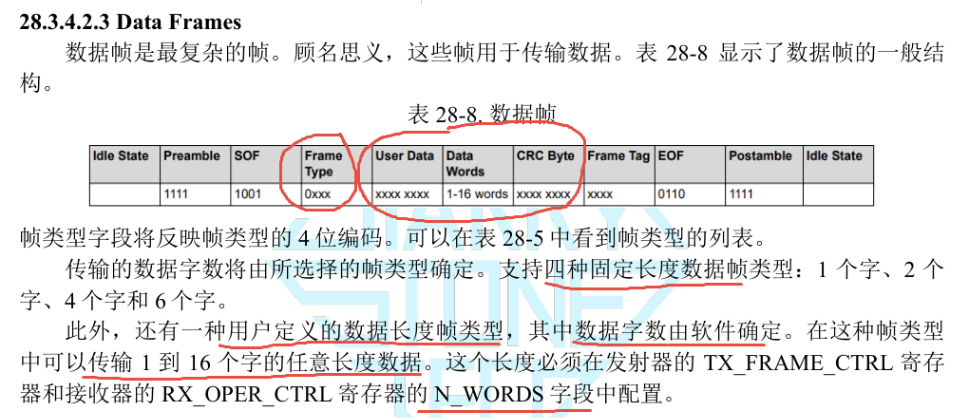

数据帧

cpp

// 使能DMA传输时,需要重新设置 发送触发源

FSI_setTxStartMode(FSITXA_BASE, FSI_TX_START_FRAME_CTRL_OR_UDATA_TAG);

// TX setting part

FSI_setTxFrameType(FSITXA_BASE, FSI_FRAME_TYPE_NWORD_DATA);

FSI_setTxSoftwareFrameSize(FSITXA_BASE, nWords);

FSI_setTxDataWidth(FSITXA_BASE, nLanes);

// 用户数据自定义

FSI_setTxUserDefinedData(FSITXA_BASE, txUserData);

FSI_setTxFrameTag(FSITXA_BASE, txDataFrameTag);

发送数据:

FSI_writeTxBuffer(FSITXA_BASE, txBufData, nWords, 0U);

FSI_startTxTransmit(FSITXA_BASE);

// Re-initialize flags and buffer pointer before next transmission

FSI_setTxBufferPtr(FSITXA_BASE, 0U);

void FSI_txDataFrame(uint16_t* buffer, uint16_t length, uint16_t Offset, FSI_FrameTag frameTag)

{

FSI_setTxFrameTag(FSITXA_BASE, frameTag);

// Set FSI TX circular buffer pointer back to beginning

FSI_setTxBufferPtr(FSITXA_BASE, 0U);

FSI_writeTxBuffer(FSITXA_BASE, buffer, length, Offset);

FSI_startTxTransmit(FSITXA_BASE);

}

cpp

// RX setting part

FSI_setRxSoftwareFrameSize(FSIRXA_BASE, nWords);

FSI_setRxDataWidth(FSIRXA_BASE, nLanes);

// 数据帧读取

FSI_enableRxInterrupt(FSIRXA_BASE, FSI_INT1, FSI_RX_EVT_DATA_FRAME);

if (rxEventSts & FSI_RX_EVT_DATA_FRAME) {

FSI_readRxBuffer(FSIRXA_BASE, rxDataArray, nWords, rxBufIndex);

}并行数据帧