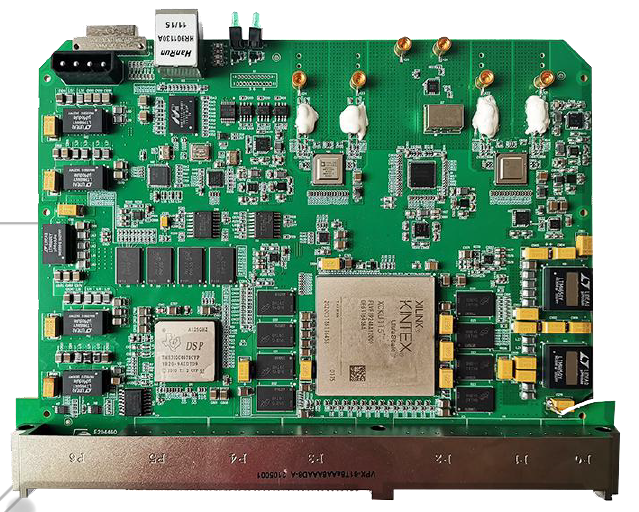

基于FPGA 和DSP 的高性能6U VPX 采集处理板,是一款处理架构采用FPGA+DSP 的高性能的6U VPX 采集处理板。板载4 片高速ADC 共8 个采集通道,可支持8 路采样率最高2.6Gsps/14Bit 的模拟信号通道。

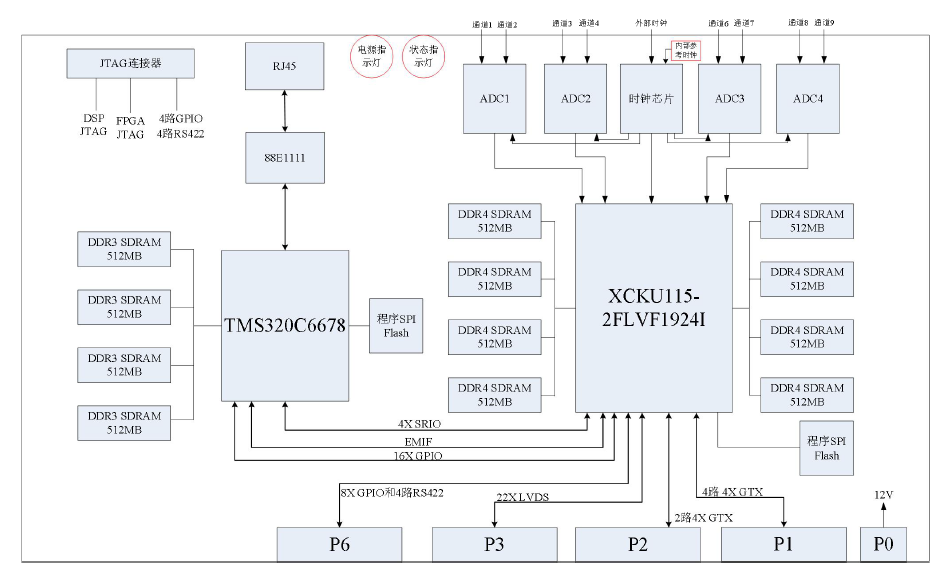

板卡FPGA 采用Xilinx 公司KU 系列的XCKU115-2FLVF1924I,DSP采用TI 公司的TMS320C6678,ADC 选型为ADI 公司的AD9689-2600。其中KU115 搭配2 组各4 片16bit 4Gb 的DDR4-2400SDRAM,总容量4GB;C6678 搭配1 组4 片16bit 4Gb 的DDR3-1333 SDRAM,总容量2GB。前面板支持8 个SMA 或SMP 连接器形式的模拟输入接口,1 个时钟接口,1个RJ45 千兆网口和1 个J30J 接口(包含DSP 和FPGA 的JTAG 调试信号,包含4 个GPIO 和4 路RS422 信号)。

背板VPX 连接器支持P0-P3、P6 共5个接口。客户可以根据应用需求灵活地选择背板和系统需要的其他板卡。便于构建灵活、高效的开发及使用环境。

应用

FPGA 信号处理

高性能计算系统

测试测量快速环境搭建

工业自动化

(雷达/声纳)电子战

大物理实验中的数据记录

产品规格

FPGA 默认为XCKU115-2FLVF1924I(也可根据需要选择XCKU085-2FLVF1924I),DSP 选择

TI 的TMS320C6678,提供高性能高性价比的采集处理方案;

• 前面板对外提供8 个SMA 或者SMP形式的ADC 接口,采样率最高2.6GSPS,精度14bit;

• 前面板对外提供1 个SMA 或者SMP形式的时钟接口,可支持参考时钟或者采样时钟切换;

• 前面板提供1 路RJ45 形式的千兆接口;

• 前面板提供一个J30J 接口连接器,可支持DSP 和FPGA 的JTAG 调试信号,包含4 个GPIO 和4 路RS422信号;提供JTAG 转接板,方便用户调试;

• FPGA 搭配2 组4GB 的高速DDR4 缓存;DSP 搭配1 组2GB 的高速DDR3缓存;

• P0 端口12V 独立供电,总功耗小于60W;

• P1 端口对外提供4 路4X SRIO,单通道传输速率可达5Gbps;

• P2 端口对外提供1 路4X PCIE,单通道传输速率可达5Gbps;

• P3 端口对外提供22 路LVDS 信号;

• P6 端口对外提供8 路GPIO,4 路RS422 信号;

• 标准6U 尺寸VPX 接口规范,支持多种协议;