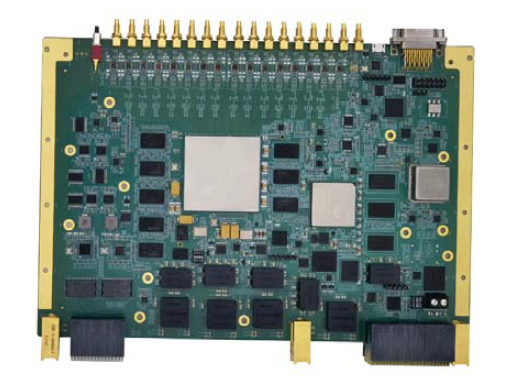

板卡概述

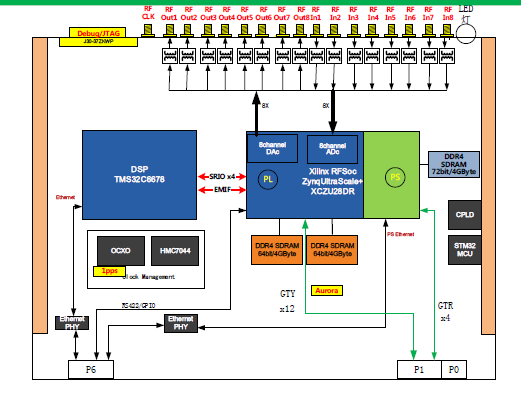

基于RFSOC ZU28DR+DSP 6U VPX处理板,是一款基于6U VPX总线架构的高速信号处理平台,数模混合信号处理卡,采用 Xilinx ZYNQ UltraScale+ RFSoC ZU28DR和TI DSP TMS320C6678组合设计,两者之间通过4x 5G SRIO互联。本板卡可实现大规模FPGA开发以及DSP数据运算处理功能。具备8路 ADC和8路DAC 端口,可扩展 I / O 端口和 DDR4 内存,适用于各种不同的可编程应用,带有 ZU28DR FPGA 的VPX6U-RFSOC-8T8R由8路 12 位,最高采样率 4.096GSPS ADC 和8路 14 位,最高采样率 6.554 GSPS DAC 端口提供支持。 该板卡具有优良的抗振动设计、散热性能和独特的环境防护设计,适合于航空、航天、船舶等应用场景。

技术指标

l 标准6U VPX规格,符合VITA46规范;

l 板载高性能FPGA处理器:XCZU28DR-2FFVE1517I

ØPS上1路 10/100/1000 EthernetRGMII网口(VPX P6);

Ø PS上2路UART接口(1路对外接口形式:VPX P6,1路板内调试);

Ø PS上1组4GByte 64bit DDR4 SDRAM;

Ø PS上1组SD/EMMC接口;

Ø 2组4GByte 64bit DDR4 SDRAM;

Ø 8 路ADC (12-bit、最大4.096GSPS)端口(SSMC连接器);

Ø 8路DAC (14-bit、最大6.554GSPS)端口(SSMC连接器);

Ø 12组GTY接口(VPX P4);

Ø8组RS422串口(VPX P6);

Ø 支持外参考时钟;

支持板内100M恒温晶振参考;

l 板载高性能DSP处理器:TMS32C6678

Ø1组2GByte 64bit DDR3 SDRAM;

Ø1片NAND FLASH; Ø1片NOR FLASH;

Ø1组4x SRIO接口与FPGA实现通信;

Ø1片EEPROM;

l 物理与电气特征

Ø 板卡尺寸:160 x 233mm

Ø 板卡供电:5A max@+12V(±5%)

Ø 散热方式:金属导冷散热 l 环境特征

Ø 工作温度:-40°~﹢65°C,存储温度:-55°~﹢125°C;

Ø工作湿度:5%~95%,非凝结

软件支持

板上各接口测试demo;

可根据客户需求提供定制化算法与系统集成: