文章目录

-

- 一、存储器种类

- 二、RAM存储器(易失性存储器)

- 三、ROM存储器(非易失性存储器)

-

- 1、**FLASH,**

- [3、**NOR FLASH**](#3、NOR FLASH)

- [4、**NAND FLASH**](#4、NAND FLASH)

- 5、总结

- 四、**EEPROM的全称是"电可擦除可编程只读存储器"**

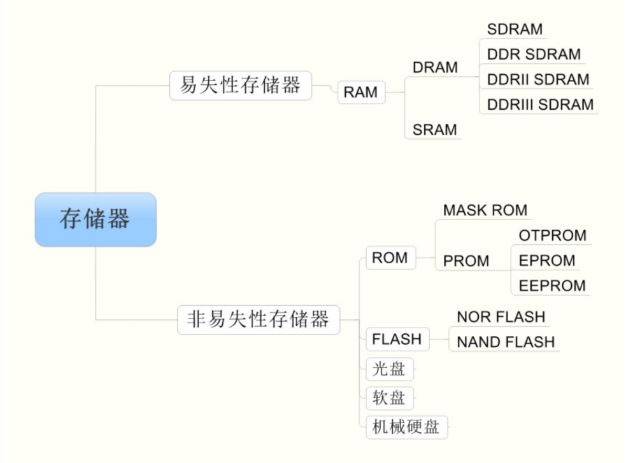

一、存储器种类

存储器是计算机结构的重要组成部分。存储器是用来存储程序代码和数据的部件,有了存储器计算机才具有记忆功能。基本的存储器种类见图基本存储器种类。存储器按其存储介质特性主要分为"易失性存储器"和"非易失性存储器"两大类。其中的"易失/非易失"是指存储器断电后,它存储的数据内容是否会丢失的特性。由于一般易失性存储器存取速度快,而非易失性存储器可长期保存数据,它们都在计算机中占据着重要角色。在计算机中易失性存储器最典型的代表是内存,非易失性存储器的代表则是硬盘。

Mask ROM(掩膜ROM):是在出厂的时候写进去的,写进去以后再也不能修改了。

PROM(可编程只读存储器):通过某些手段,在出厂以后还可以进行编程。只能修改一次。

EPROM(可擦除可编程ROM):使用紫外线照射的方法,多次。

二、RAM存储器(易失性存储器)

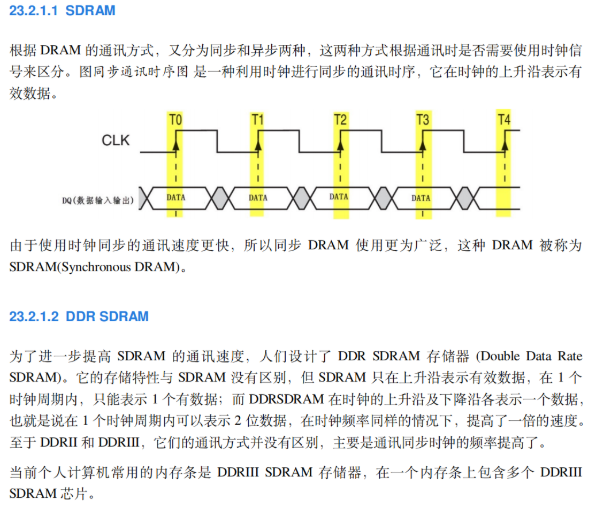

RAM 是"Random Access Memory"的缩写,被译为随机存储器。所谓"随机存取",指的是当存储器中的消息被读取或写入时,所需要的时间与这段信息所在的位置无关。这个词的由来是因为早期计算机曾使用磁鼓作为存储器,磁鼓是顺序读写设备,而 RAM 可随读取其内部任意地址的数据,时间都是相同的,因此得名。实际上现在 RAM 已经专门用于指代作为计算机内存的易失性半导体存储器。根据 RAM 的存储机制,又分为动态随机存储器 DRAM(Dynamic RAM) 以及静态随机存储器SRAM(Static RAM) 两种。

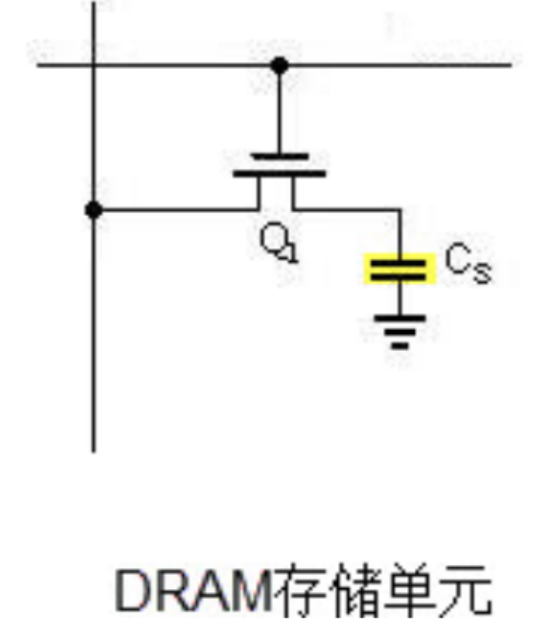

1、DRAM

动态随机存储器 DRAM 的存储单元以电容的电荷来表示数据,有电荷代表 1,无电荷代表 0,见图 DRAM 存储单元。但时间一长,代表 1 的电容会放电,代表 0 的电容会吸收电荷,因此它需要定期刷新操作,这就是"动态 (Dynamic)"一词所形容的特性。刷新操作会对电容进行检查,若电量大于满电量的 1/2,则认为其代表 1,并把电容充满电;若电量小于 1/2,则认为其代表 0,并把电容放电,藉此来保证数据的正确性。

2、SRAM

静态随机存储器 SRAM 的存储单元以锁存器来存储数据,见图 SRAM 存储单元。这种电路结构不需要定时刷新充电,就能保持状态 (当然,如果断电了,数据还是会丢失的),所以这种存储器被称为"静态 (Static)"RAM。

3、DRAM 与 SRAM 的应用场合

对比 DRAM 与 SRAM 的结构,可知 DRAM 的结构简单得多,所以生产相同容量的存储器,DRAM的成本要更低,且集成度更高。而 DRAM 中的电容结构则决定了它的存取速度不如 SRAM,特性对比见表 DRAM 与 SRAM 对比。

所以在实际应用场合中,SRAM 一般只用于 CPU 内部的高速缓存 (Cache),而外部扩展的内存一般使用 DRAM。在 STM32 系统的控制器中,只有 STM32F429 型号或更高级的芯片才支持扩展SDRAM,其它型号如 STM32F1、STM32F2 及 STM32F407 等型号只能扩展 SRAM。

三、ROM存储器(非易失性存储器)

1、FLASH,

相比较EEPROM,擦除时不再以字节为单位,而是以块为单位,,一次简化了电路,数据密度更高,降低了成本。上M的ROM一般都是Flash,如GD25Q16,有2M个字节;NOR 与 NAND 的共性是在数据写入前都需要有擦除操作,而擦除操作一般是以"扇区/块"为单位的。而 NOR 与 NAND 特性的差别,主要是由于其内部"地址/数据线"是否分开导致的。

FLASH分为NOR FLASH 和NAND FLASH:

3、NOR FLASH

芯片内部的数据线和地址线分开,可以实现 RAM一样的随机寻址功能,可以读取任何一个字节。但是擦除仍要按块来擦。如GD25Q16;

由于 NOR 的地址线和数据线分开,它可以按"字节"读写数据,符合 CPU 的指令译码执行要求,所以假如 NOR 上存储了代码指令,CPU 给 NOR 一个地址,NOR 就能向 CPU 返回一个数据让CPU 执行,中间不需要额外的处理操作。

在使用中:因为 NOR FLASH可以进行字节寻址,所以程序可以在NOR FLASH中运行。

单片机程序是运行在FLASH中,内部是NOR FLASH,

4、NAND FLASH

同样是按块擦除,但是数据线和地址线复用,不能利用地址线随机寻址。读取只能按页/块来读取。(NANDFLASH 按块来擦除,按页来读,NORFLASH没有页)。如W29N01HVSINA;而由于 NAND 的数据和地址线共用,只能按"块"来读写数据,假如 NAND 上存储了代码指令,CPU 给 NAND 地址后,它无法直接返回该地址的数据,所以不符合指令译码要求。NAND FLASH 引脚上复用,因此读取速度比NOR FLASH慢一点,但是擦除和写入速度比NOR FLASH快很多;NAND FLASH内部电路更简单,因此数据密度大,体积小,成本也低。因此大容量的FLASH都是 NAND型 的。小容量的2~12M 的 FLASH多是NOR型的;

例如我们使用的U盘,一般都是NAND FLASH

使用寿命上,NANDFLASH的擦除次数是NOR的数倍。而且NAND FLASH可以标记坏块,从而使软件跳过坏块。NORFLASH一旦损坏便无法再用;

手机 SOC 程序是跑在内存中,所以一般使用的是NAND FLASF。

5、总结

另外,FLASH 的擦除次数都是有限的 (现在普遍是 10 万次左右),当它的使用接近寿命的时候,可能会出现写操作失败。由于 NAND 通常是整块擦写,块内有一位失效整个块就会失效,这被称为坏块,而且由于擦写过程复杂,从整体来说 NOR 块块更少,寿命更长。由于可能存在坏块,所以 FLASH 存储器需要"探测/错误更正 (EDC/ECC)"算法来确保数据的正确性。由于两种 FLASH 存储器特性的差异,NOR FLASH 一般应用在代码存储的场合,如嵌入式控制器内部的程序存储空间。而 NAND FLASH 一般应用在大数据量存储的场合,包括 SD 卡、U 盘以及固态硬盘等,都是 NAND FLASH 类型的。

四、EEPROM的全称是"电可擦除可编程只读存储器"

这种ROM的特点是可以随机访问和修改任何一个字节,可以往每个bit位 中写入 0或者1;

掉电后数据不丢失,可以保存100年,可以擦写100w次;

具有较高的可靠性,但是芯片构成电路复杂/成本也高,因此目前的EEPROM容量都很小,例如我们常见的24C02,只有256个字节。02表示的是2K bit,24C16表示的是16K bit

2K bit = 256 * 8 = 2048 bit

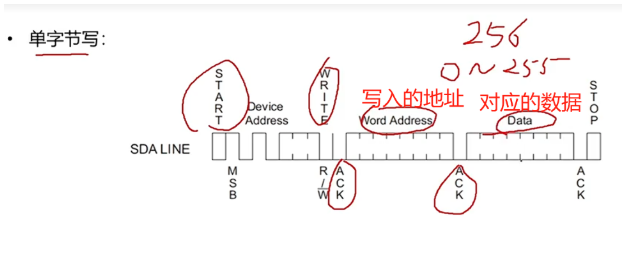

1、单字节写入

24C02写数据:

256个字节可以写入数据,每个字节都有对应的一个地址,地址的范围是0到255,因此我们要写入数据之前,必须告诉EEPROM我们要向哪个地址写入数据。

随机访问和修改任何一个字节,所以在写的时候不一定得要从第一个字节写进去。

2、可以按页写

24C02每一页有8个字节,那么一共有32页。

0是第一页的起始地址(使用的是是10进制表示)

8是第二页的起始地址(使用的是是10进制表示)

16是第三页的起始地址(使用的是是10进制表示)

等等一次类推。

并且不一定非要从每一页的起始地址开始写入数据,例如可以从第一页的"1(使用的是是10进制表示)"这个地址写入数据。

在一页内部 芯片会自动将数据地址加1,但是当内部产生的地址达到该页边界地址时,随后的数据将写入该页的页首。如果超过8个数据传送给了EEPROM,地址将回转到该页的首字节,先前的字节将会被覆盖;

写数据超过1页时,可以重新发起,包括要有起始信号、设备地址、数据起始地址、数据和结束信号;

写数据超过1页时,页和页之间要有间隔,EEPROM写数据需要时间。

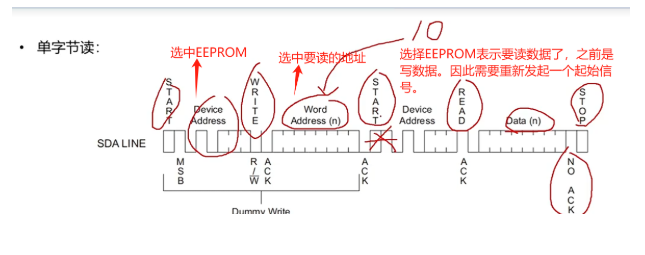

三、单字节读

第一步:起始信号

第二步:选中相应的EEPROM,并且是写信号。

第三步:写入要读数据的地址

第四步:因为之前都是写命令,因此需要重新告诉EEPROM我要读数据了,因此这个时候需要一个起始信号。(相当于是进行一次重置)

第五步:选中相应的EEPROM,并且是读信号。

第六步:读出数据,最后是非应答信号。一定要切记,是非应答信号。

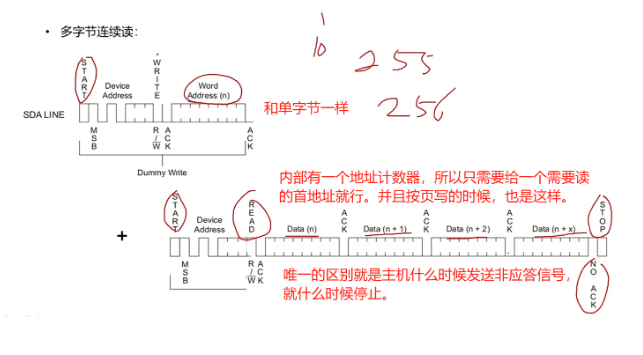

四、多字节连续读

地址计数器,在芯片内部实现的.

文章源码获取方式:

如果您对本文的源码感兴趣,欢迎在评论区留下您的邮箱地址。我会在空闲时间整理相关代码,并通过邮件发送给您。由于个人时间有限,发送可能会有一定延迟,请您耐心等待。同时,建议您在评论时注明具体的需求或问题,以便我更好地为您提供针对性的帮助。

【版权声明】

本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议。这意味着您可以自由地共享(复制、分发)和改编(修改、转换)本文内容,但必须遵守以下条件:

署名:您必须注明原作者(即本文博主)的姓名,并提供指向原文的链接。

相同方式共享:如果您基于本文创作了新的内容,必须使用相同的 CC 4.0 BY-SA 协议进行发布。

示例:

如果您在博客或文章中引用了本文的内容,请在显著位置标注类似以下声明:

本文部分内容参考自 [博主名称] 的原创文章,原文链接:[文章链接],遵循 CC 4.0 BY-SA 版权协议。

感谢您的理解与支持!如果您有任何疑问或需要进一步协助,请随时在评论区留言。*