- 官网:www.arm.com

- 官方资料:

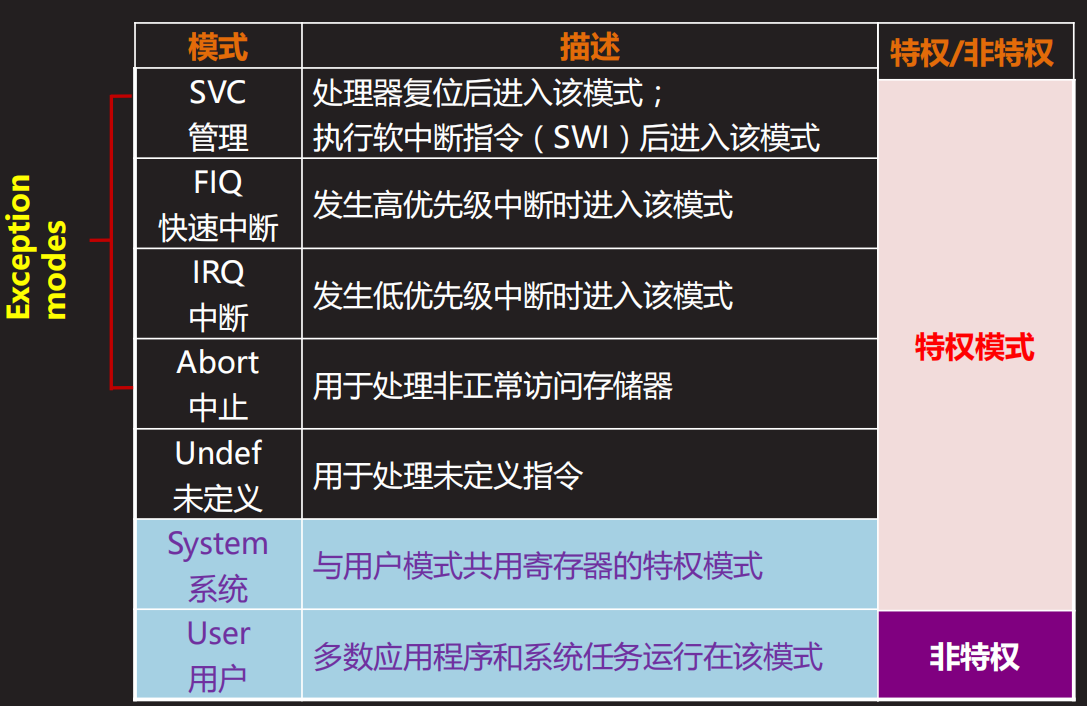

ARM 工作模式

七大基本工作模式

- 通用的有以下七种工作模式:

- 前5种称为异常模式,用来处理系统异常

- 前6种称为特权模式

- system模式是为了解决同类型异常嵌套而设计的。例如IRQ模式下执行了子函数调用,会把返回地址保存到LR_寄存器。此时如果又产生了IRQ异常,硬件自动会把异常执行完的返回地址保存到LR_,覆盖掉了子函数调用后的返回地址。为此,ARMv4及之后的版本提供了system mode这样一种处理器模式来解决这个问题

- System mode是一种特权模式,而且共用User模式的所有寄存器

注意:System mode不是因为发生了某种异常处理器自动进入的模式,而是异常处理函数通过修改CPSR来进入的

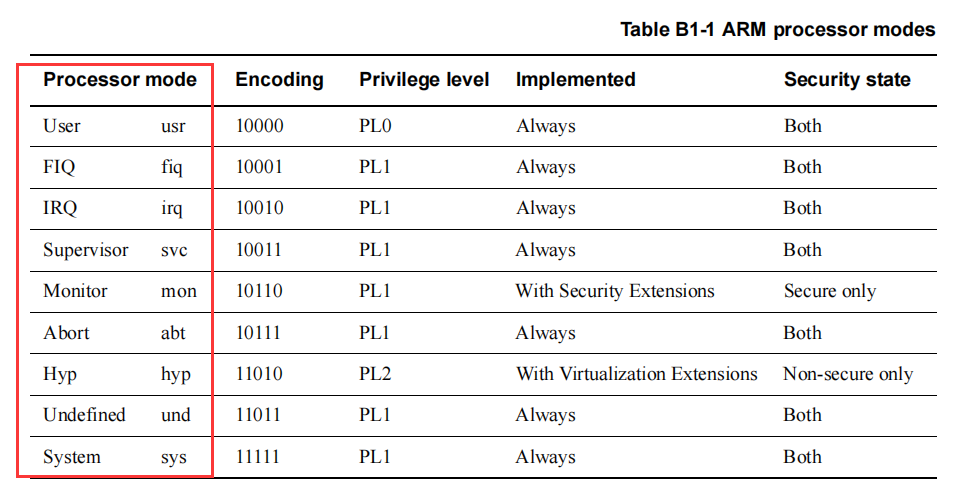

ARMv7新增工作模式

- ARMv7架构中增加的两种工作模式:

- Monitor模式,安全监控模式,为了安全而扩展出的用于执行安全监控代码的模式

- Hpy模式,针对虚拟化技术的支持

工作状态(指令集状态)

- 四种工作状态:

- ARM 状态,执行ARM指令(32bit)

- Thumb状态,执行Thumb指令(16bit)

- ThumbEE状态, 16bit、32bit的混合指令

- Jazelle状态,对JAVA代码执行加速

- 程序执行时可以完成ARM状态和THUMB的切换。执行异常处理时,应该工作于ARM状态

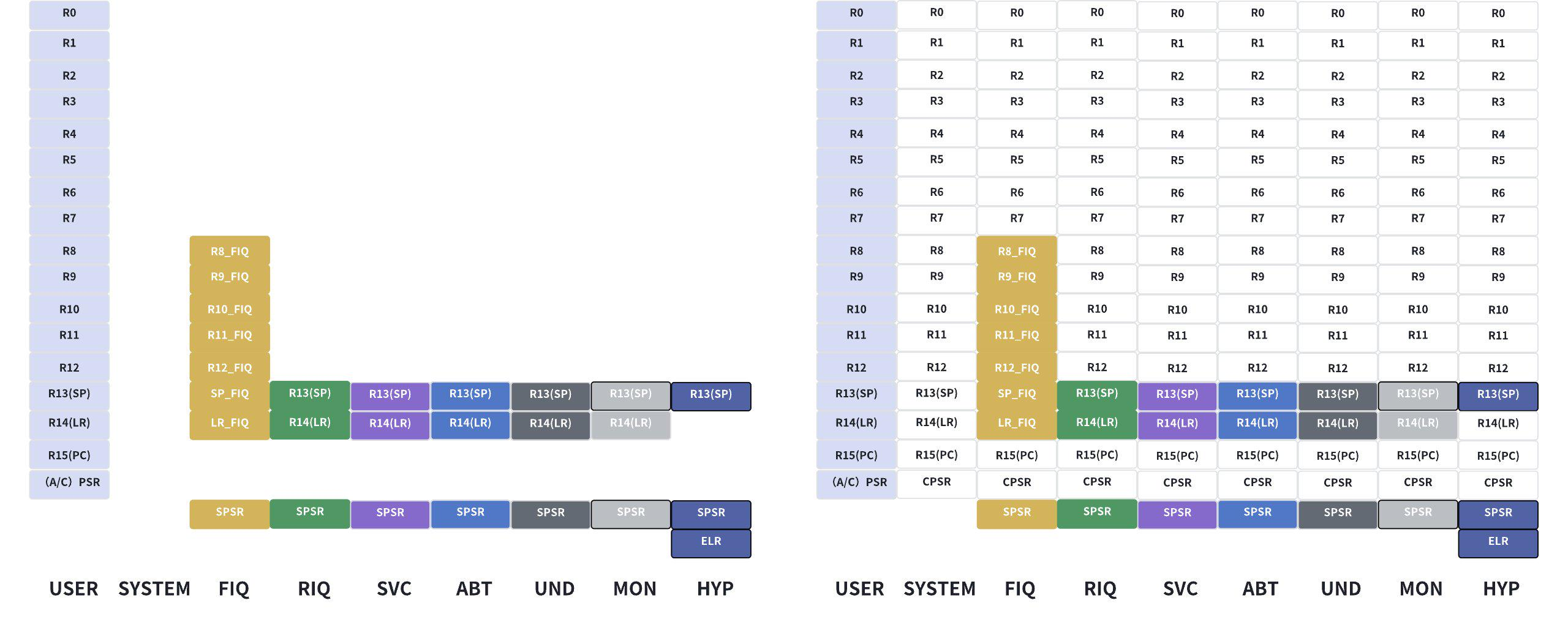

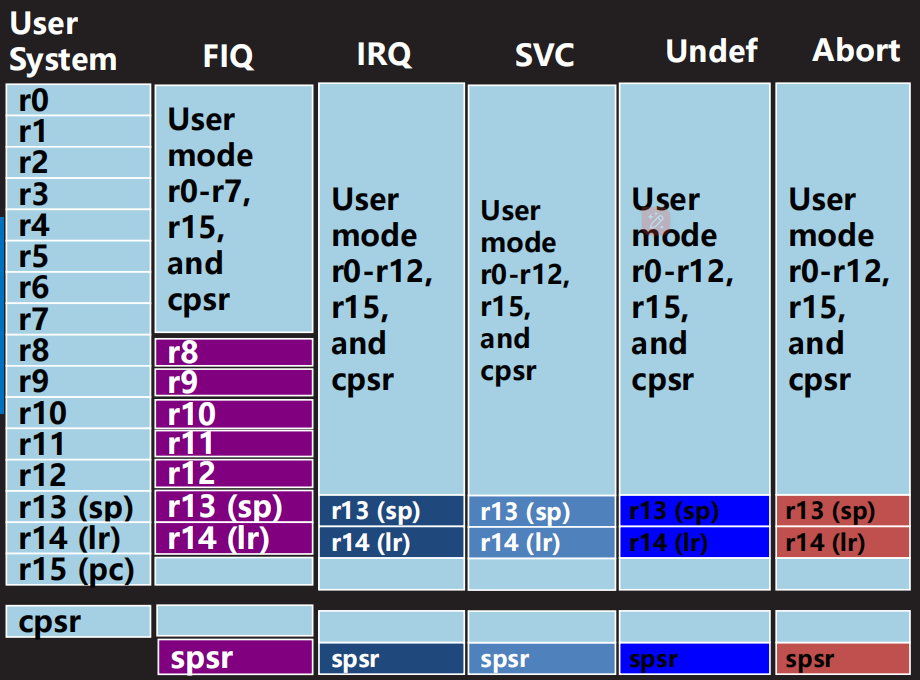

寄存器组织架构

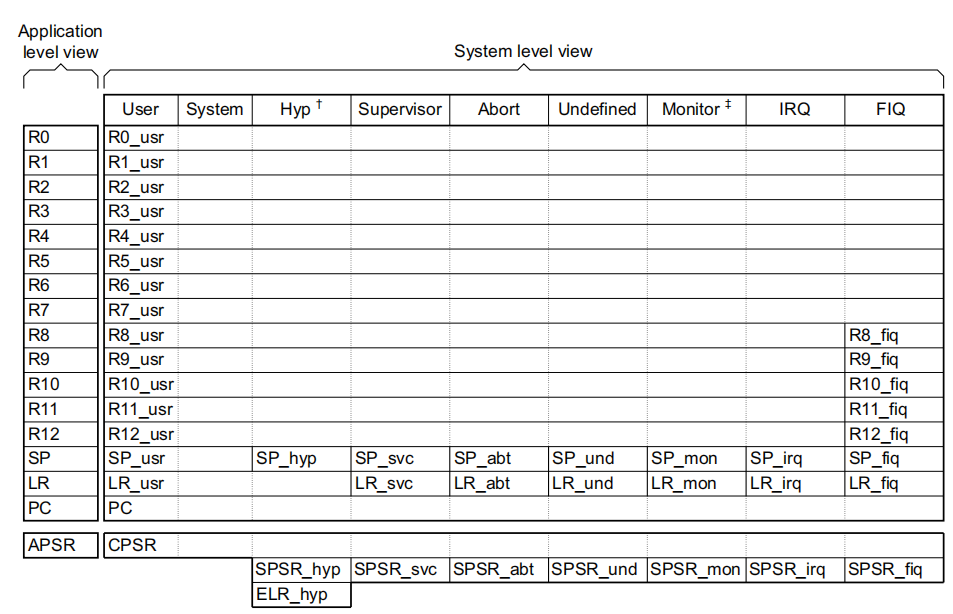

通用寄存器组织形式

- ARM核中有37个32bit的寄存器

- 其中31个通用寄存器,分别被命名为r0 r1 r2 ... r15

- 1个cpsr寄存器、5个spsr寄存器

- 每种工作模式下只能访问37个寄存器的一个子集

- 通用寄存器的说明

- r13(sp, 栈指针寄存器)

- r14(lr, 保存函数的返回地址)

- r15(pc, 保存取指令的地址)

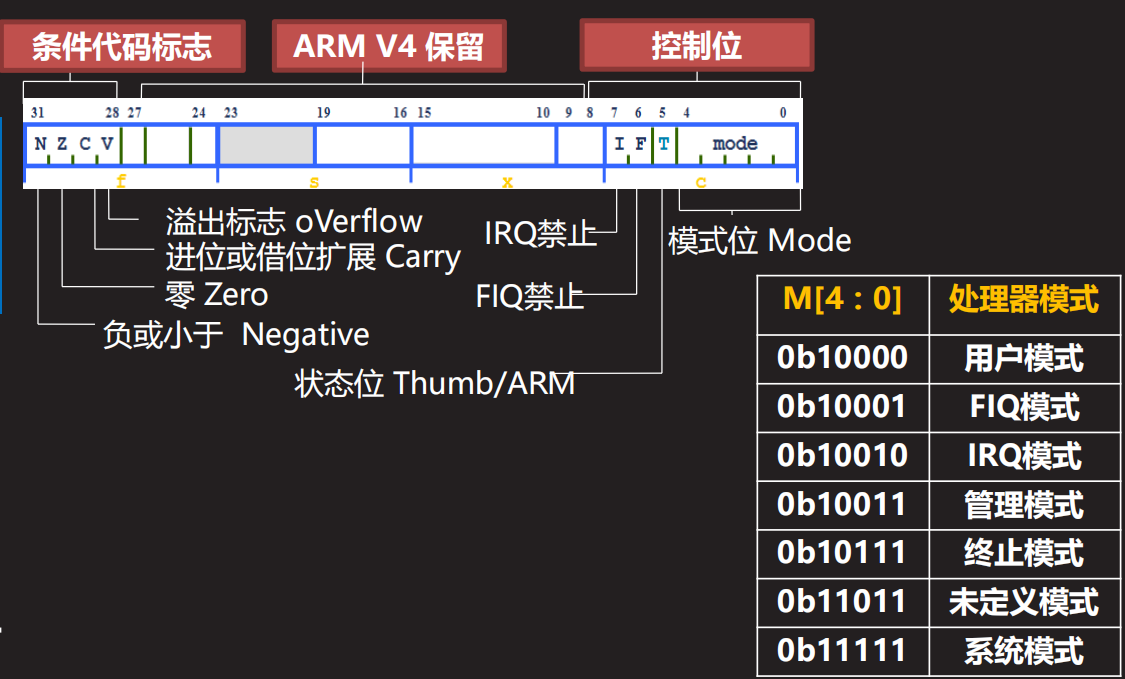

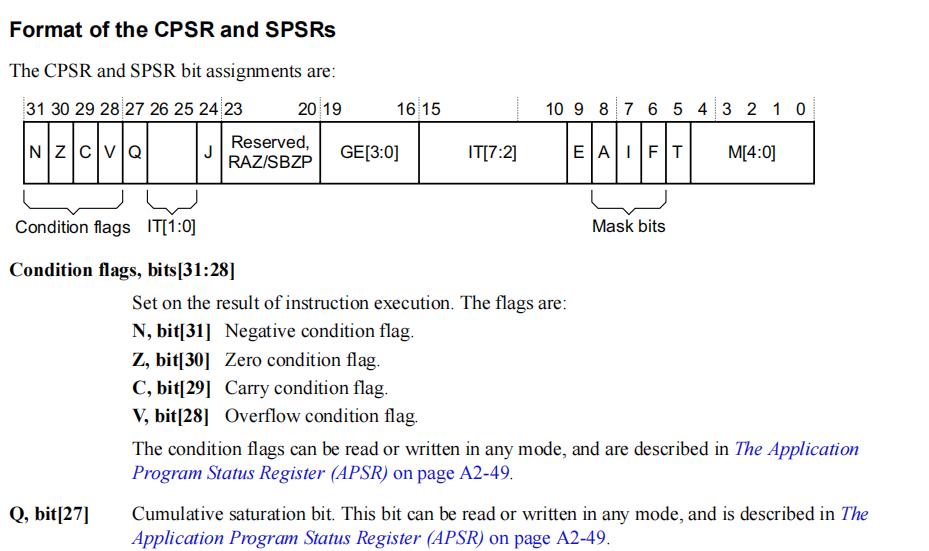

- cpsr/spsr的说明

- cpsr, currented Program Statued Register:当前程序状态寄存器

- spsr, Saved Program Statued Register:cpsr的备份寄存器

-

4:0\] 模式位,标识当前ARM核工作于哪种工作模式

-

6\] F=1/0 , 屏蔽/不屏蔽FIQ异常

-

28\] V位:Overflow,对于加减法指令,在操作数和结果是有符号的整数时,如果发生溢出,则V=1,反之V=0

-

30\] Z位:Zero,运算结果为0, Z=1 反之Z=0

ARMv7架构

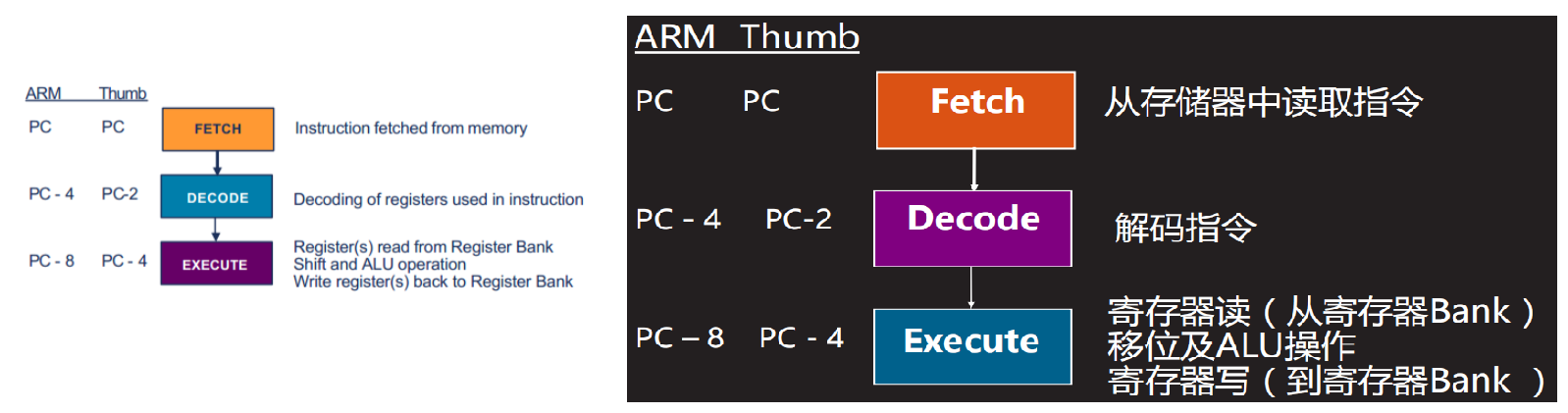

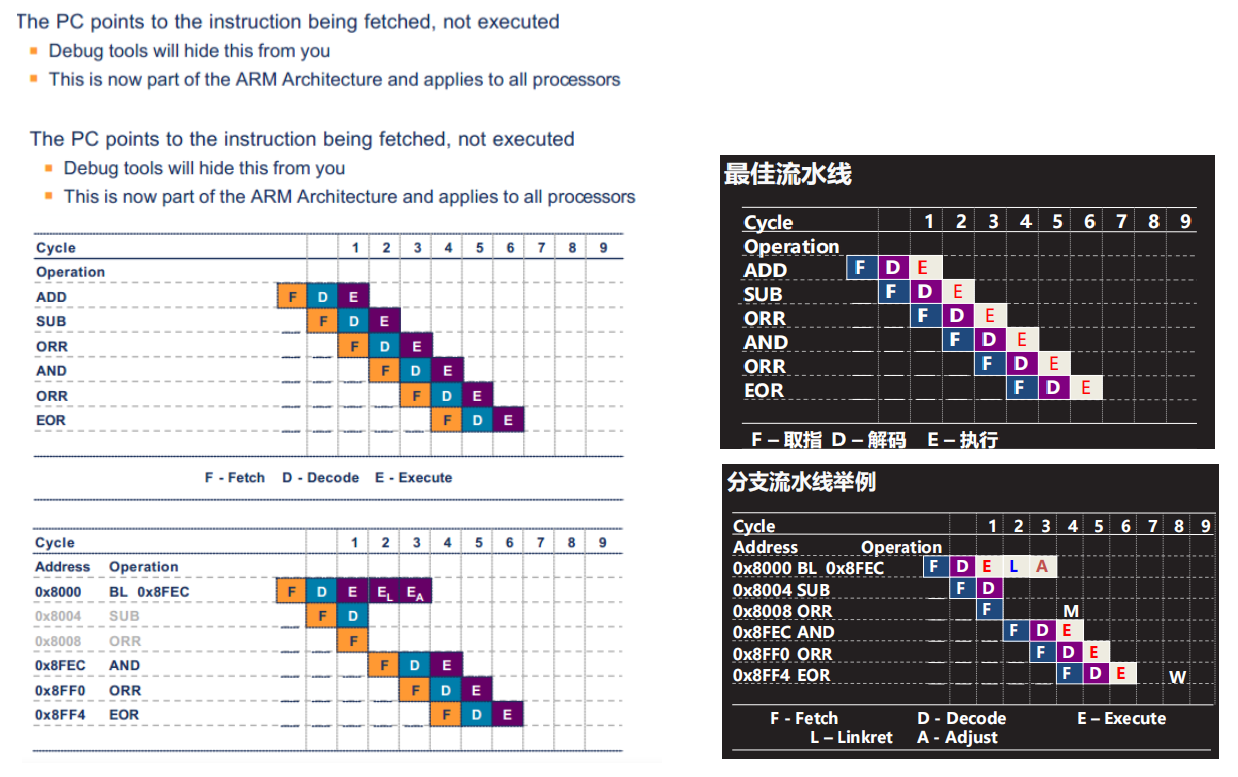

三级流水线

- 为了提高指令的执行效率,ARM汇编指令采用流水线的方式执行

- ARM流水线可以分为3级流水线,5级流水线,7级流水线,8级流水线,13级流水线。cortex-A7中采用的是8级流水线

- 三级流水线:取指令、解码指令、执行指令

- ARM工作状态下,当前正在执行的指令地址 = PC - 8

异常与异常向量表

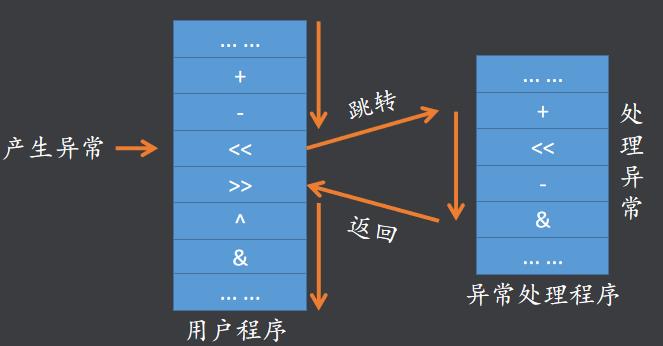

- 异常是指在计算机系统运行过程中发生的不正常情况,由于内部或者外部的一些事件所导致的,例如:IO错误、缓冲区溢出等都属于异常

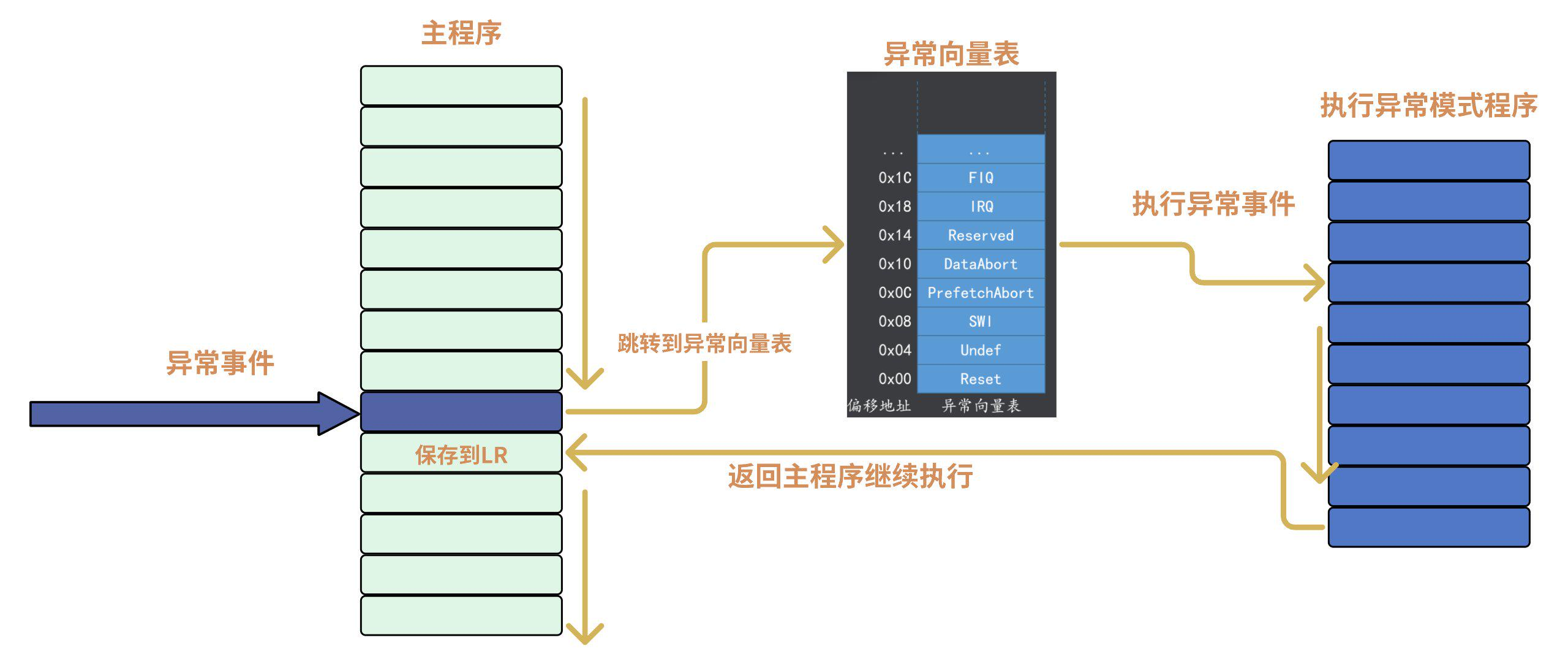

- 计算机中对异常的处理套路:异常产生时,CPU就要将当前的程序暂停下来转而去处理这个异常的事件,异常事件处理完成之后再返回到被异常打断的点继续执行程序

ARM中的异常

- ARM支持7种异常:

| 异常名称 | 产生原因 | CPU 进入的工作模式 |

|---|---|---|

| Reset(复位异常) | 按下复位键、系统上电 | SVC |

| Undefined Instruction (未定义指令异常) | 处理器遇到无法识别的指令 | Undefined |

| SWI (软中断异常) | 执行软中断汇编指令 | SVC |

| Prefetch Abort (预取终止异常) | 取指令时访问了非法地址 | Abort |

| Data Abort (数据终止异常) | 取数据时访问了非法地址 | Abort |

| IRQ(中断异常) | 硬件(按键、定时器...)产生中断信号 | IRQ |

| FIQ (快速中断异常) | 硬件(DMA...)产生快速中断信号 | FIQ |

- ARM支持的7种异常会导致ARM和进入5种异常工作模式

处理异常

- 需要软硬件配合来实现

硬件硬件自动执行的 "四大核心操作"

- ARM收到异常信号,首先介入处理异常的就是硬件(ARM就是这么设计的)。硬件上收到异常信号,会执行四大、三小的操作

| 硬件操作步骤 | 具体行为 | 作用说明 |

|---|---|---|

| 1. 状态保存 | 拷贝当前 CPSR(当前程序状态寄存器)的内容到对应异常模式 下的 SPSR_<mode>(保存程序状态寄存器) |

保存异常发生前的 CPU 状态,方便异常处理完成后恢复 |

| 2. 修改 CPSR | + 设置 CPSR.I=1(关闭 IRQ 普通中断)、CPSR.F=1(关闭 FIQ 快速中断) + 设置 CPSR.T=0(强制进入 ARM 指令模式,异常处理代码不能用 Thumb 指令 + 修改 CPSR.mode为对应异常的工作模式(如 IRQ 模式、SVC 模式) |

避免异常处理过程中被其他中断打断,同时切换到异常处理所需的工作模式 |

| 3. 保存返回地址 | 将异常返回地址写入对应异常模式 下的 LR_<mode>(链接寄存器) |

记录异常发生前的执行位置,异常处理完成后通过 LR 返回原程序 |

| 4. 跳转异常向量 | 给 PC(程序计数器)赋值为异常向量表中对应异常的固定地址(如复位异常是 0x00、IRQ 是 0x18) |

让 CPU 跳转到异常处理程序的入口地址,开始执行软件处理逻辑 |

软件需要执行的操作

- 现场保护:将异常处理过程中会用到的通用寄存器(如 R0-R12)保存到栈中(不同异常模式有独立的栈,需提前初始化),避免覆盖原程序的寄存器值

- 执行异常处理逻辑:根据异常类型执行具体处理(如 IRQ 中断处理硬件事件、数据终止异常处理地址错误)

- 恢复现场:从栈中恢复之前保存的通用寄存器值

- 异常返回:

- 从 SPSR_ 恢复 CPSR(恢复异常前的 CPU 状态);

- 从 LR_ 修正后的值恢复 PC(不同异常的 LR 需要偏移不同值,如 IRQ 异常 LR 需减 4),跳回原程序继续执行

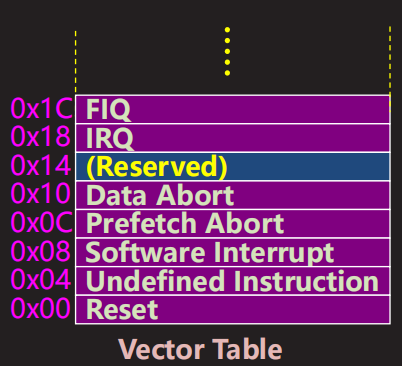

| 异常名称 | 产生原因 | CPU进入的 工作模式 | PC赋值 |

|---|---|---|---|

| Reset | 按下复位键、系统上电 | SVC | PC = vec_base + 0x00 |

| Undefined Instruction | 处理器遇到无法识别的指令 | Undefined | PC = vec_base + 0x04 |

| SWI | 执行软中断汇编指令 | SVC | PC = vec_base + 0x08 |

| Prefetch Abort | 取指令时访问了非法地址 | Abort | PC = vec_base + 0x0c |

| Data Abort | 取数据时访问了非法地址 | Abort | PC = vec_base + 0x10 |

| IRQ | 硬件(按键、定时器...)产生中断信号 | IRQ | PC = vec_base + 0x18 |

| FIQ | 硬件(DMA...)产生快速重点信号 | FIQ | PC = vec_base + 0x1c |

- 异常产生后,跳转的位置是一片连续的内存。而在这片内存中留给处理每种异常的代码空间只有四字节(一条ARM指令)

- 该条指令只能是放跳转指令,当异常产生时,跳转到该位置, 而该位置上存储的也是一条跳转指令,使得继续跳转到更广阔的空间,在该广阔空间中分别放置对应异常处理代码。而存储了跳转指令的这片连续的内存就称作异常向量表了

- 一般情况下异常向量表出现在0x00000000 或者0xFFFF0000地址上。也可以通过CP15协处理器设置异常向量表放置在任意位置

存储模型

- ARMv7架构:

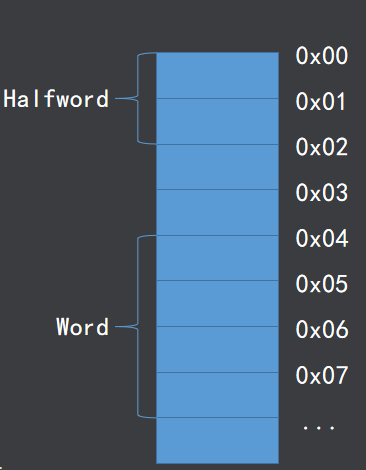

- 支持的数据类型:

latex

Byte ---> 字节 ---> 8bits(1字节)

Half word ---> 半字 ---> 16bits(2字节)

word ---> 字 ---> 32bits(4字节)

Doubleword --->双字 ---->64bits(8字节)- 对齐方式

- 数据本身是多少字节在内存存储时就应该多少字节对齐(超过4字节的按4字节对齐)

- 例如半字是2字节数据,就应该放置在2字节对齐的内存中

- 字是4字节数据,就应该放置在4字节对齐的内存中。

- 双字放置在4字节对齐的内存中(比较特殊)

- 如果没有内存对齐,就有可能导致内存访问效率降低或者出现不可预测结果

- 大小端

latex

int a = 0x12345678;

地址 大 小

0x100 12 78

0x101 34 56

0x102 56 34

0x103 78 12- 不同架构的芯片在存储以上int类型数据时,采用的策略是不同的。

- X86采用小端模式,PowerPC采用大端模式

- ARM默认是小端模式,但可以通过操作CP15协处理器切换为大端模式