一、概述(Overview)

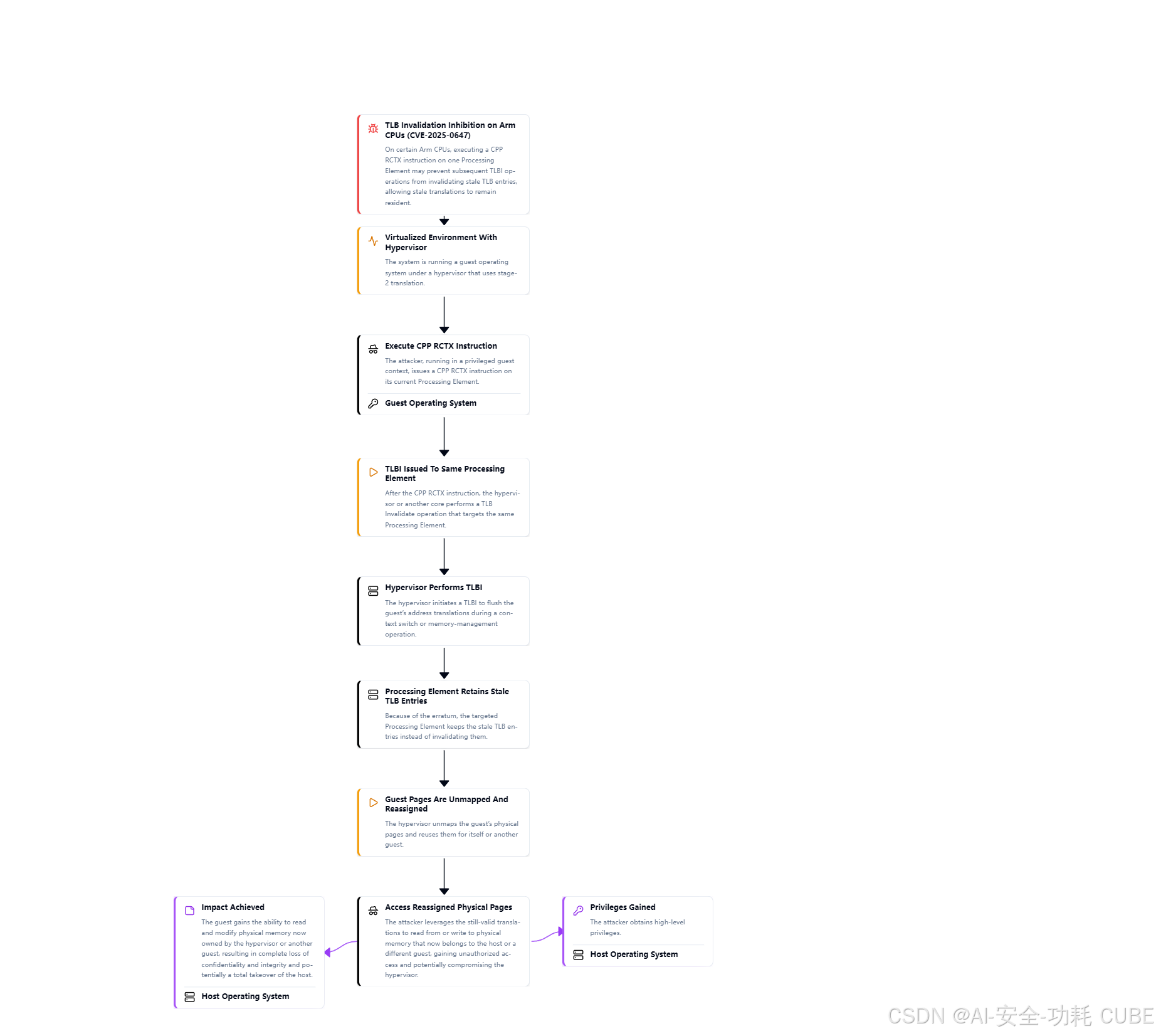

在部分基于 Arm 的 CPU 中发现一个漏洞:在某些虚拟机管理程序(hypervisor)环境下,经过修改且不受信任的guest操作系统(guest OS)可能利用该问题破坏宿主系统(host)的安全性。

在某些基于 Arm 的 CPU 中,如果某个处理单元(Processing Element,PE)执行了一条 CPP RCTX 指令,那么当向该 PE 发出 TLBI(TLB Invalidate)操作时------无论该 TLBI 是由同一个 PE 发出,还是由同一共享域(shareability domain)中的其他 PE 发出------都可能导致该 TLBI 失效操作被抑制。

在这种情况下,该 PE 可能会保留本应被 TLBI 失效的陈旧(stale)TLB 条目。

二、CVE 详情(CVE Details)

该问题已分配编号:CVE-2025-0647

受影响的 Arm 处理器允许特权级guest(privileged guest)执行 CPP RCTX 指令,该指令会抑制同一核心上后续的 TLB(Translation Lookaside Buffer,地址转换后备缓冲区)失效操作。

由于虚拟机管理程序(hypervisor)假定刷新(flush)已经成功完成,物理页可能会被重新分配,而此时guest仍然持有有效的地址转换条目。这样,guest就可以读取或修改当前已归属于宿主或其他guest的内存,从而破坏二级地址转换(stage-2)隔离机制。

三、受影响产品(Affected Products)

-

C1-Ultra,C1-Premium

-

Cortex-A710

-

Cortex-X2,Cortex-X3,Cortex-X4,Cortex-X925

-

Neoverse-V2,Neoverse-V3,Neoverse-V3AE

-

Neoverse-N2

四、建议(Recommendations)

为规避该问题,受影响的合作伙伴在每次执行 CPP RCTX 指令时,必须执行 TLB(Translation Lookaside Buffer,地址转换后备缓冲区)失效操作(TLB invalidation)。

有关具体操作方法,请参阅对应产品的勘误通知(Errata Notice)。

五、致谢(Acknowledgements)

该问题由 Arm 识别发现。

版本历史(Version History)

| 版本 | 日期 | 描述 |

|---|---|---|

| 1-0 | 2026年1月14日 | 初始发布 |