一、概念

状态机(State Machine)又称有限状态机(Finite State Machine, 简称FSM),是在有限个状态之间按一定规律转换的时序电路。

二、模型

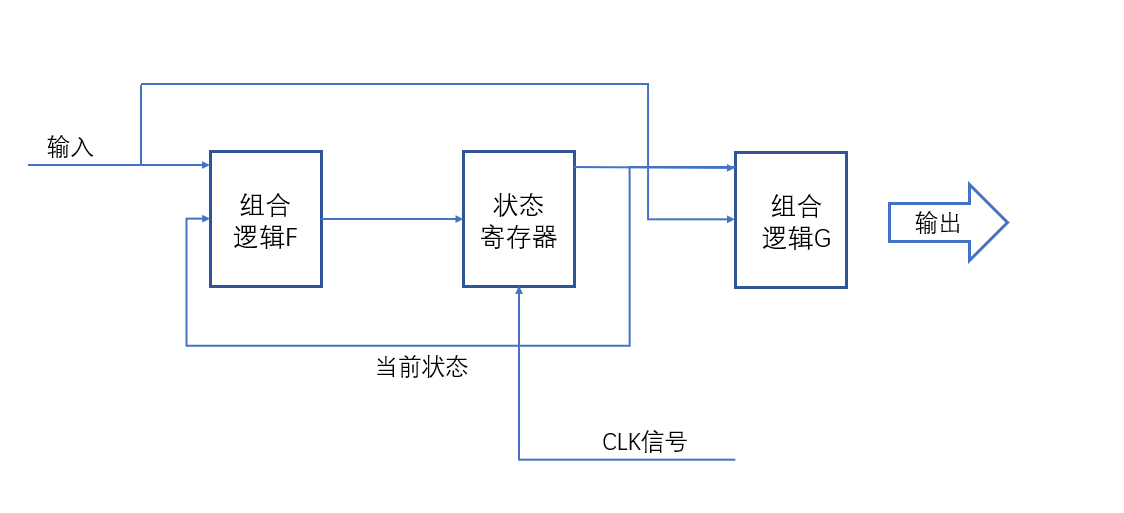

下面用模型的方式说明状态机的工作原理:

状态机的输入有两个部分,一部分是当前状态机zhe所处的状态,另一部分是用户的输入。其中状态寄存器由一组D触发器组成,用来记忆状态机当前所处的状态,状态的改变只发生在时钟的跳变沿。状态是否改变、如何改变,取决于组合逻辑F的输出,F是当前状态和输入信号的函数状态机的输出是出输出组合逻辑G提供的,G也是当前状态和输入信号的函数。

状态机由组合逻辑G的输入的不同分为moore状态机和mealy状态机,moore状态机的组合逻辑G的输入只有当前状态,而mealy状态机的输入包括用户输入和当前状态。

三、状态机的设计

状态机的设计一般采用四段论的一个方法,按序排列如下:状态空间定义、状态跳转、下一状态判断、各个状态的下的动作。

3.1 状态空间定义

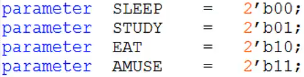

使用parameter关键字定义状态机的各状态,所有状态的集合就叫做状态空间:

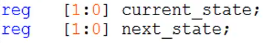

使用reg关键字定义状态寄存器和下一状态变量

这里需要注意的是这两个reg变量的位宽应该和状态空间中的状态常量位宽一致。

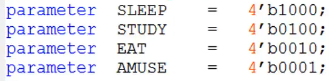

在定义状态空间时,一般使用更加直观,译码更加简单的独热码的形式来定义,独热码是指每个状态只有一个寄存器置位(置1),译码逻辑简单:

此时状态寄存器和下一状态变量位宽也应该是四。

3.2 状态的跳转(时序逻辑部分)

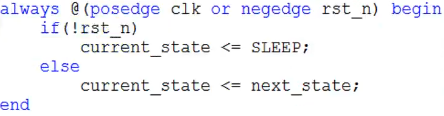

状态的跳转使用always语句描述,以时钟信号上升沿为触发条件,使用非阻塞赋值,不停的更新状态寄存器为next_state的状态,具体示例代码如下:

3.3 下一状态判断(组合逻辑)

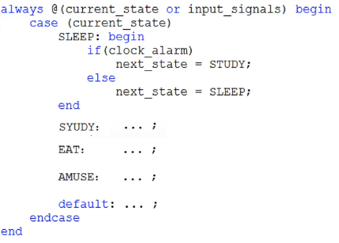

状态的判断使用always语句描述,以输入信号的电平触发(每输入一次判断一次),使用case关键字在当前状态的前提下去判断下一状态应该是怎样的。

3.4 状态下的动作(组合逻辑)

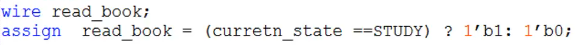

对于简单的动作,可以使用assign关键字+条件语句的形式规定每一个状态下的动作,举例如下:

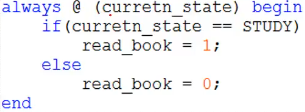

复杂动作则可以使用always语句来进行状态的动作,举例如下:

四 总结

本文对状态机进行了详细的介绍,主要介绍了状态机的设计,状态机的设计可以归结为两个组合逻辑和一个时序逻辑的组合。在Verilog代码上则体现为状态定义+三个功能定义语句(并行运行)。