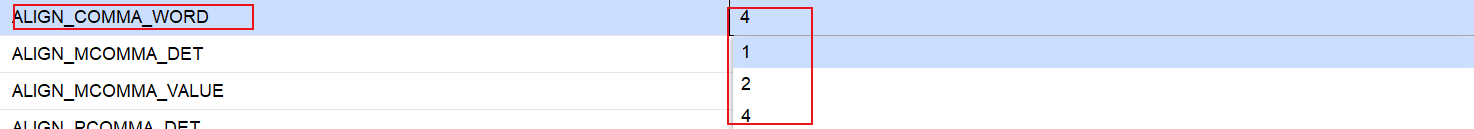

ALIGN_COMMA_WORD可以设置的值为1、2、4,是用于word中对齐的byte数;

如果设置为1,表示的是任意字节对齐;

如果设置为2,表示的是2byte边界对齐;

如果设置为4,表示的是4byte边界对齐。

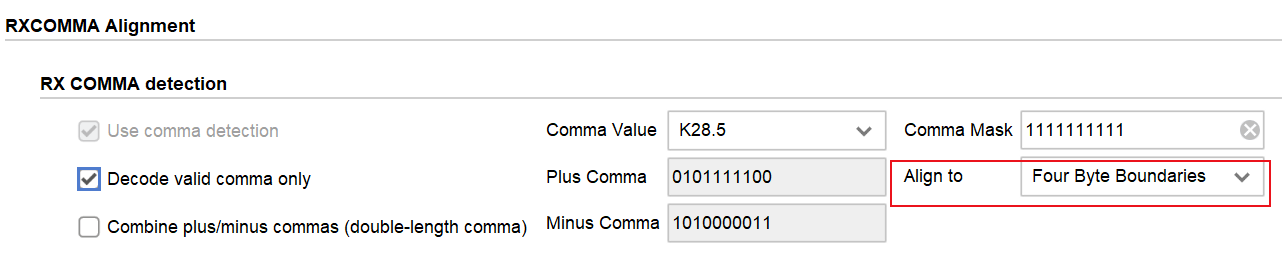

此参数对于的GUI界面为:

用于修饰对齐方式。

可以通过约束的方式进行限定:

set_property ALIGN_COMMA_WORD 1 [get_gt_channels gt_rx_ch0]

or

set_property ALIGN_COMMA_WORD 2 [get_gt_channels gt_rx_ch0]

or

set_property ALIGN_COMMA_WORD 4 [get_gt_channels gt_rx_ch0]