目录

1.课题概述

流水线(Pipeline)技术源于工业生产中的装配线理念,在数字电路中,它将一个复杂运算任务分解为若干个子任务,每个子任务由专门的电路模块(级)完成,且各级可以并行工作。前一级的输出作为后一级的输入,通过寄存器(或锁存器)在时钟边沿同步传递,从而实现 "多任务并发处理"。对于加法器而言,传统的组合逻辑加法器(如超前进位加法器)的延迟随输入位数增加而显著增长(通常与位数呈对数关系),导致最高工作频率受限。而流水线加法器通过时间换空间的策略,将长延迟的组合逻辑分割为短延迟的多级电路,每级延迟控制在一个时钟周期内,从而大幅提升工作频率。

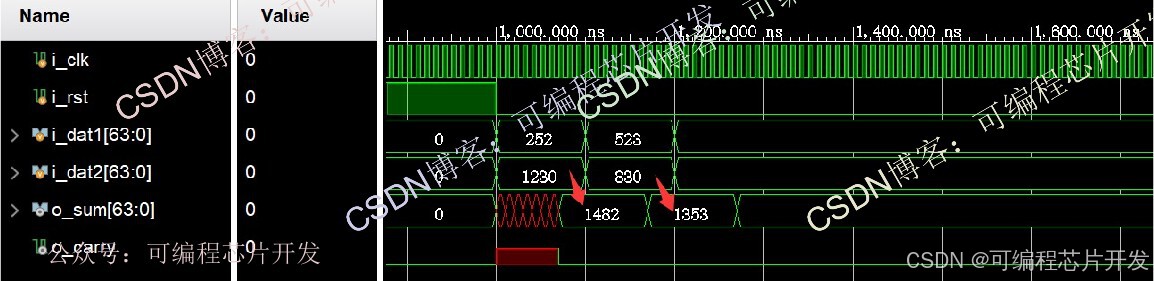

2.系统仿真结果

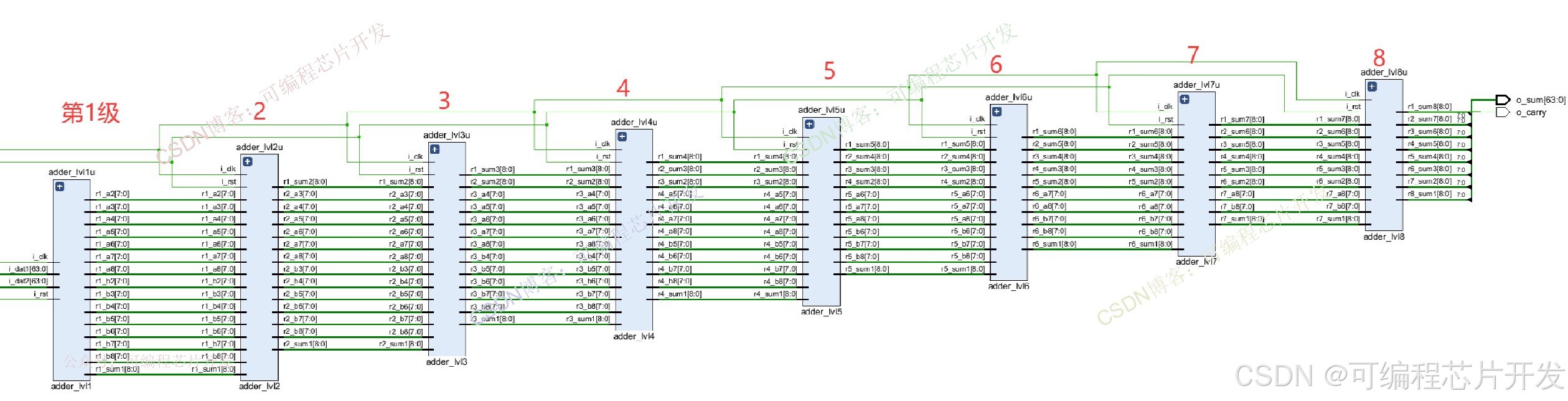

RTL结构图如下:

3.核心程序

vivado2022.2

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2025/07/20 20:27:36

// Design Name:

// Module Name: Test_multi_adder

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module Test_multi_adder();

reg i_clk; // 时钟信号,用于驱动流水线各级寄存器

reg i_rst; // 复位信号,高电平有效,复位时所有寄存器清零

reg [63:0] i_dat1; // 64位输入数据1,作为加法运算的第一个操作数

reg [63:0] i_dat2; // 64位输入数据2,作为加法运算的第二个操作数

wire [63:0] o_sum; // 64位加法结果输出

wire o_carry; // 进位输出,当64位加法结果溢出时为1

multi_adder multi_adderu(

.i_clk (i_clk), // 时钟信号,用于驱动流水线各级寄存器

.i_rst (i_rst), // 复位信号,高电平有效,复位时所有寄存器清零

.i_dat1 (i_dat1), // 64位输入数据1,作为加法运算的第一个操作数

.i_dat2 (i_dat2), // 64位输入数据2,作为加法运算的第二个操作数

.o_sum (o_sum), // 64位加法结果输出

.o_carry(o_carry) // 进位输出,当64位加法结果溢出时为1

);

initial

begin

i_clk=1'b1;

i_rst=1'b1;

i_dat1=64'd0;

i_dat2=64'd0;

#1000

i_rst=1'b0;

i_dat1=64'd252;

i_dat2=64'd1230;

#100

i_dat1=64'd523;

i_dat2=64'd830;

#100

i_dat1=64'd0;

i_dat2=64'd0;

end

always #5 i_clk=~i_clk;

endmodule

00X6_007m4.系统原理简介

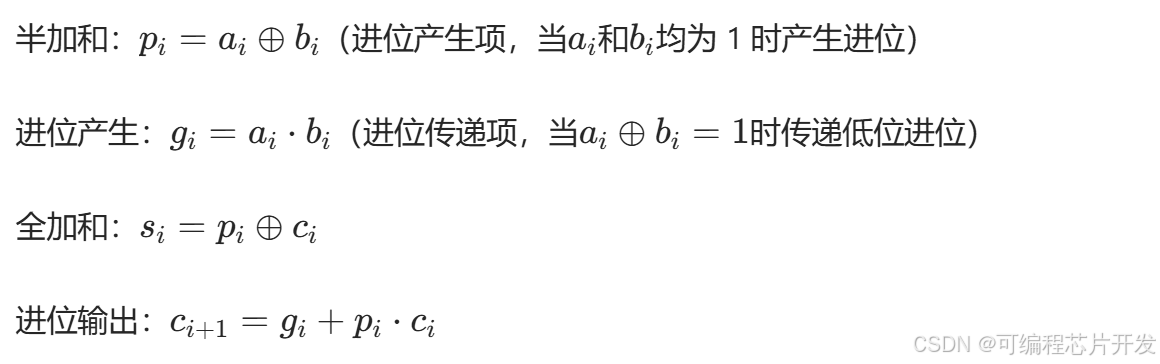

加法运算的延迟主要来自进位链(Carry Chain)。以 n 位加法器为例,两个二进制数A=an−1an−2...a0和B=bn−1bn−2...b0相加,其第 i 位的和si与进位ci+1的计算公式为:

其中,c0为初始进位(通常为 0,即无进位输入)。从公式可见,ci+1依赖于ci,形成串行的进位链:c1依赖c0,c2依赖c1,...,cn依赖cn−1。对于n位加法器,进位链的总延迟与n成正比( ripple-carry adder)或O(logn)(超前进位加法器),但即使是超前进位,当n很大(如 64 位、128 位)时,延迟仍会超过时钟周期限制。

FPGA的架构特点(LUT、进位链资源、寄存器)对流水线加法器的实现有显著影响。主流 FPGA(如 Xilinx 7系列、Intel Cyclone系列)均提供专用进位链逻辑(如Xilinx的Carry4模块),可高效实现进位传递,因此流水线设计需与FPGA的硬件资源匹配。

与其他加法器的性能对比:

| 加法器类型 | 延迟(n 位) | 吞吐量 | 资源消耗(LUT+FF) | 适用场景 |

|---|---|---|---|---|

| 串行进位加法器 | O(n) | 1/T | 低(n + 1) | 低速、低资源场景 |

| 超前进位加法器 | O(logn) | 1/T | 中(nlogn) | 中速、中等资源场景 |

| 2级流水线加法器 | 2T(首次) | 1/T | 中(n + 2) | 中高速场景 |

| k级流水线加法器 | kT(首次) | 1/T | 高(n + k) | 高速、高吞吐量场景 |

当加法器需要支持级联扩展(如 128 位、256 位)时,可将多个 k 级流水线加法器通过进位链连接,形成更大位数的加法器。此时,上级加法器的进位输出cn作为下级加法器的进位输入c0,并通过额外的流水线寄存器同步,确保级间时序匹配。

5.参考文献

1\]袁松,唐敬友,刘莉.一种基于多级流水线加法器的累加电路设计研究\[J\].四川理工学院学报:自然科学版, 2012, 25(5):4.DOI:CNKI:SUN:SCQX.0.2012-05-014. ## 6.完整工程文件 **v** **v**