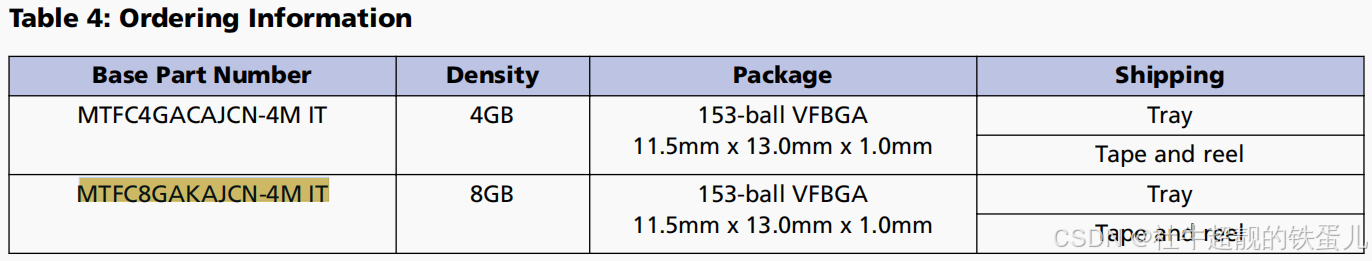

1.1 芯片订购信息

美光MTFC8GAKAJCN-4M_IT型eMMC,容量8GB,153-ball VFBGA封装。

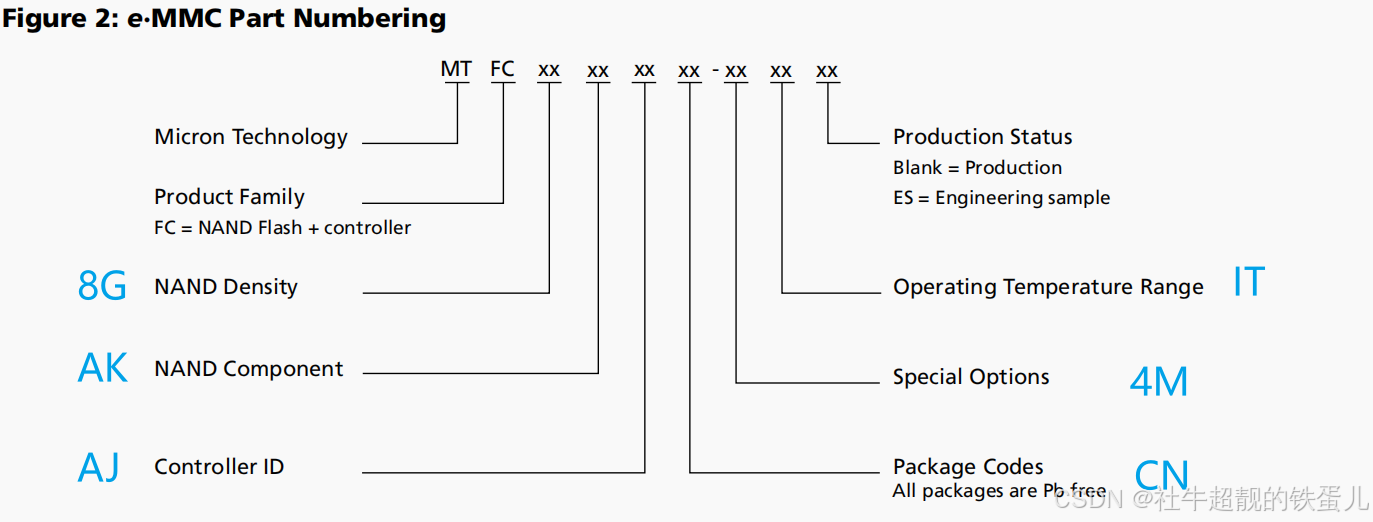

1.2 eMMC料号含义

2.1 特性

•多媒体卡(MMC)控制器和NAND闪存

•153球FBGA封装(符合RoHS标准,环保封装)

•VCC:2.7--3.6V

•VCCQ(双电压):1.65--1.95V;2.7--3.6V

•工业温度范围

--工作温度:-40˚C至+85˚C

--存储温度:-40˚C至+85˚C

2.2 MMC特性

•符合JEDEC/MMC标准5.0版(JEDEC标准编号JESD84-B50)

--先进的12信号接口;

--主机可选支持x1、x4和x8个I/O通道

--支持SDR/DDR模式,时钟频率最高达52 MHz

--HS200/HS400模式

--实时时钟

--命令类别:类0(基础);类2(块读取);类4(块写入);类5(擦除);类6(写保护);类7(锁卡)

--临时写保护

--强制启动(高速启动)

--睡眠模式

--可重放保护内存块(RPMB)

--安全擦除与安全修剪

--硬件复位信号

--多分区增强属性

--永久及上电写保护

--高优先级中断(HPI)

--后台操作

--可靠写入

--数据丢弃与清理

--扩展分区

--上下文ID

--数据标签

--声明已打包的命令

--设备容量动态调整

--向后兼容旧版MMC

--缓存

--现场固件更新(FFU)

--设备运行状态报告

--休眠通知

--关机通知

•实现ECC和块管理

2.3 e-MMC性能和电流消耗

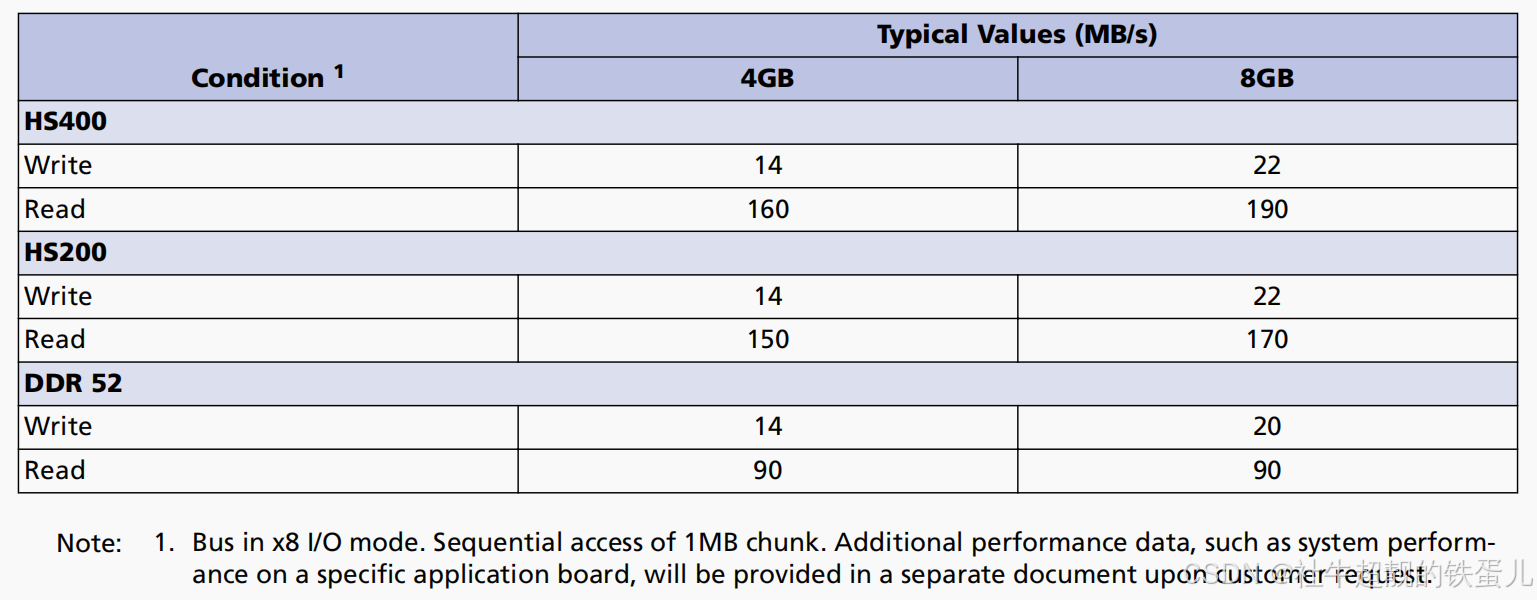

表1:MLC分区顺序性能

注:1.总线处于x8 I/O模式。对1MB块进行顺序访问。其他性能数据,例如特定应用板上的系统性能,将在客户要求时提供在单独的文档中。

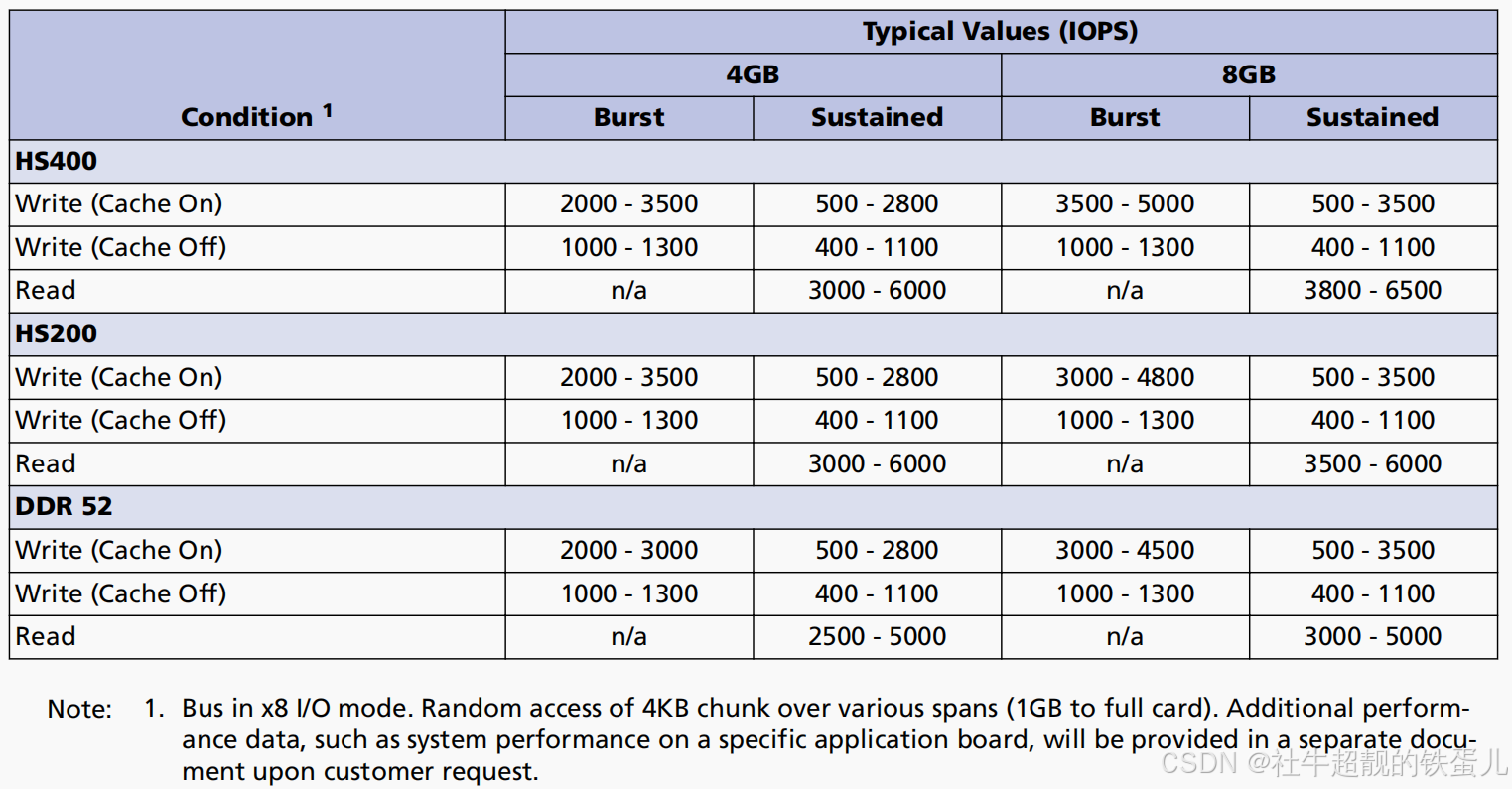

表2:MLC分区随机性能

注:1.总线处于x8 I/O模式。随机访问不同跨度的4KB块(从1GB到整个卡)。其他性能数据,例如特定应用板上的系统性能,将在客户要求时提供在单独文档中。

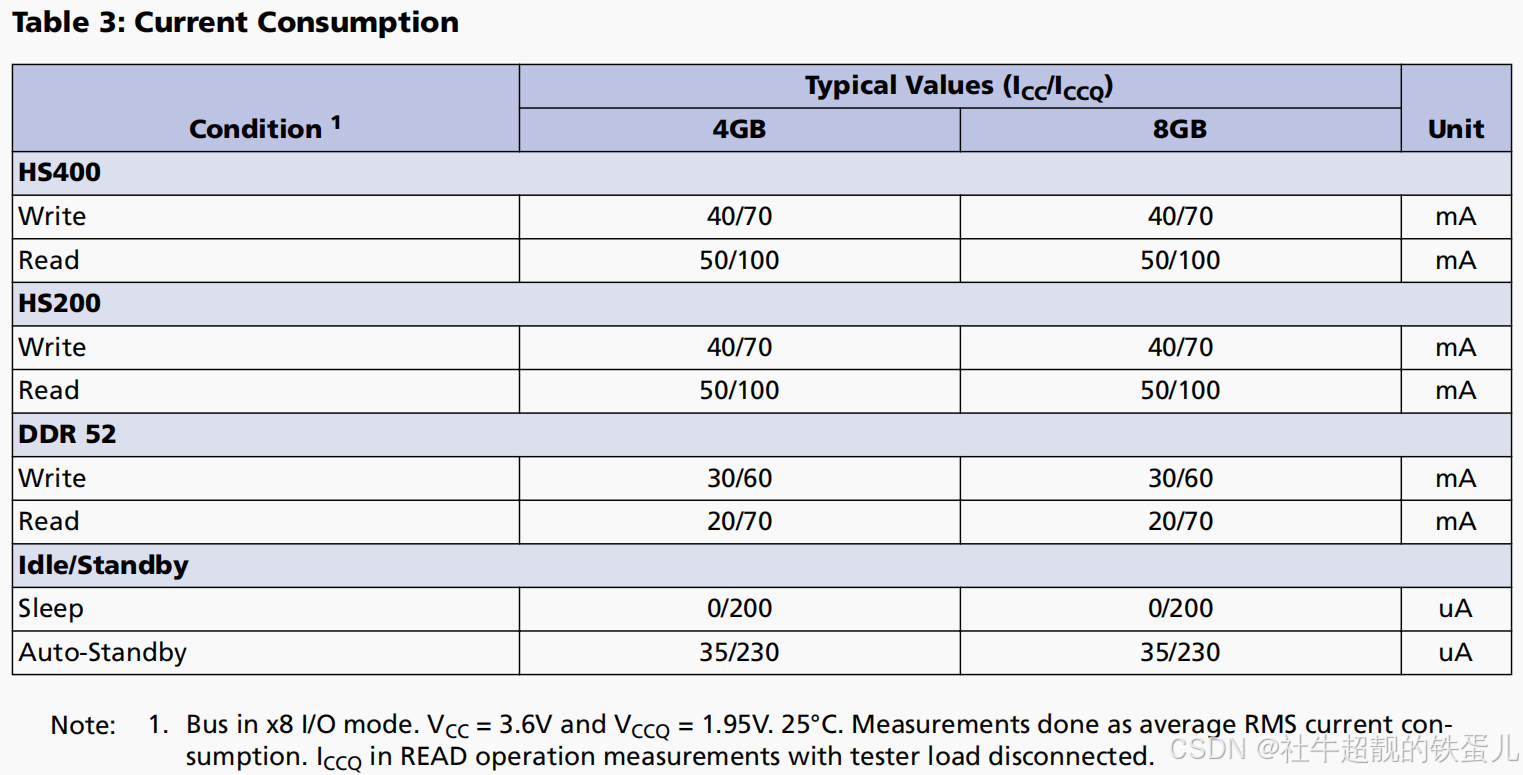

表3:电流消耗

注:1.总线处于x8 I/O模式。VCC = 3.6V,VCCQ = 1.95V,25°C。测量结果为平均RMS电流消耗。ICCQ为在测试仪负载断开时在读取操作的电流测量值。

3、一般说明

美光eMMC是一种通信与大容量数据存储设备,采用符合MMC系统规范的先进11信号总线架构,集成了多媒体卡(MMC)接口、NAND闪存组件及控制器。其每比特成本优势显著、封装体积小巧且可靠性优异,堪称工业应用领域的理想选择,广泛应用于基础设施网络设备、个人电脑服务器等各类工业产品。

这种非易失性存储器在保持数据完整性时无需持续供电,可在宽泛的工作温度范围内稳定运行,并具备抗冲击抗振动的特性。

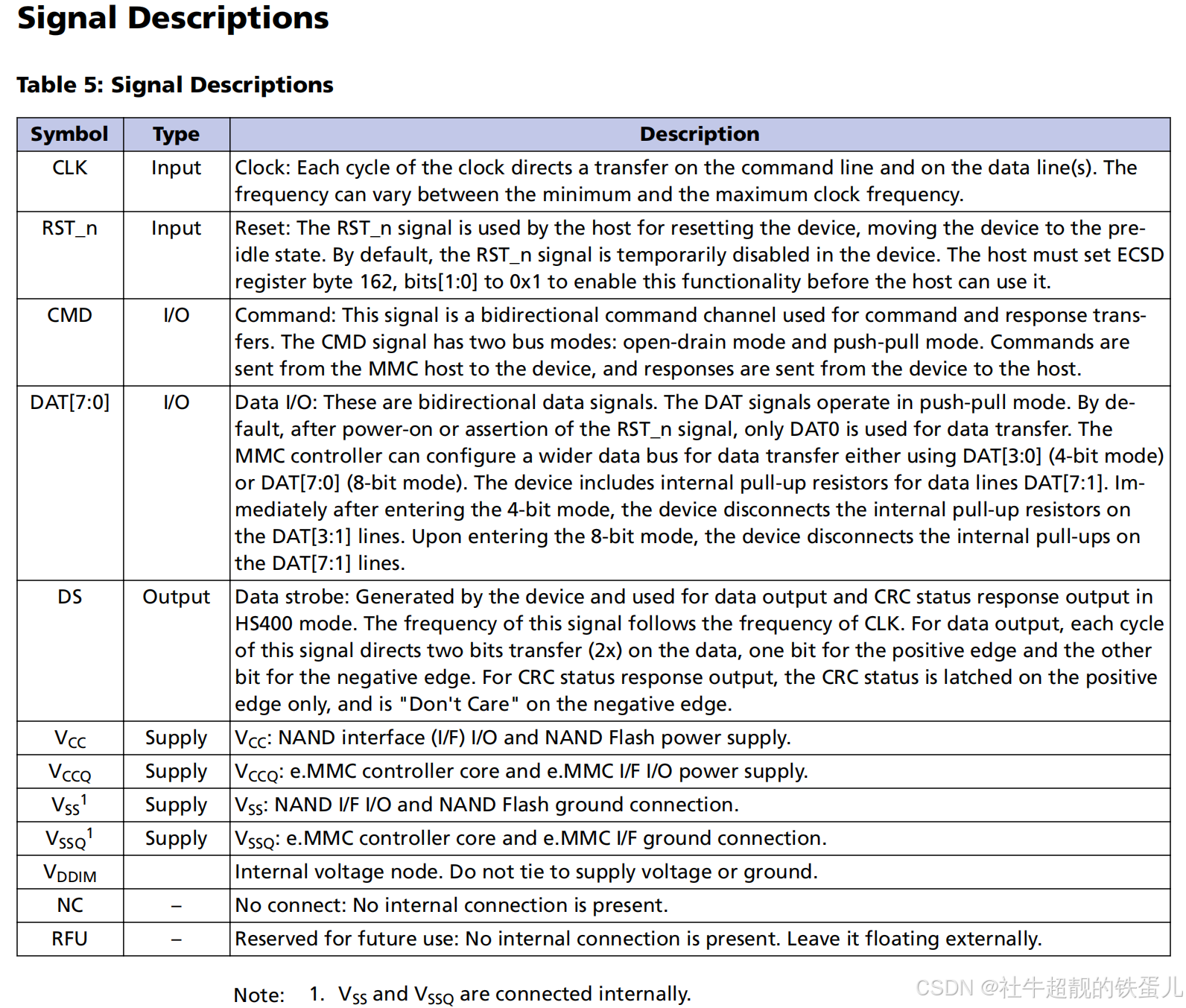

3.1 信号描述

CLK,时钟(输入)。命令行和数据线(s)在每个时钟周期上进行一次传输。频率可在最小和最大时钟频率之间变化。

RST_n,复位(输入)。RST_n信号由主机用来复位设备,将设备移至预空闲状态。默认情况下,设备中暂时禁用RST_n信号。主机必须将ECSD寄存器字节162的bit[1:0]设置为0x1才能启用此功能。

CMD,命令(输入/输出)。此信号是双向的命令通道,用于命令和响应传输。CMD信号有两种总线模式:开漏模式和推挽模式。命令由MMC主机发送到设备,响应由设备发送到主机。

DAT[7:0],数据(输入/输出)。此为双向数据信号。DAT信号采用推挽模式工作。默认情况下,设备通电或RST_n信号被激活后,仅DAT0通道用于数据传输。MMC控制器可通过DAT[3:0](4位模式)或DAT[7:0](8位模式)配置更宽的数据总线进行传输。设备内置用于DAT[7:1]数据线的上拉电阻。设备进入4位模式后,会立即断开DAT[3:1]线路上的上拉电阻。当设备切换至8位模式时,会断开DAT[7:1]线路上的上拉电阻。

DS,数据选通信号(输出)。由设备生成,用于HS400模式下的数据输出和CRC状态响应输出。该信号频率与时钟信号CLK保持同步。在数据输出时,每个信号周期会向数据线传输两个比特(2x),其中正沿传输一个比特,负沿传输另一个比特。对于CRC状态响应输出,CRC状态仅在正沿被锁存,而在负沿则处于"无关紧要"状态。

VCC,电源。NAND接口(I/F)I/O和NAND闪存电源。

VCCQ,电源。e.MMC控制器核心和e.MMC I/F I/O电源。

VSS,地。NAND I/F I/O和NAND Flash接地。

VSSQ,地。e.MMC控制器核心和e.MMC I/F接地。

VDDIM,内部电压节点。勿连接到电源电压或接地。

NC,无连接。不存在内部连接。

RFU,预留将来使用。没有内部连接,保持外部浮动悬空。

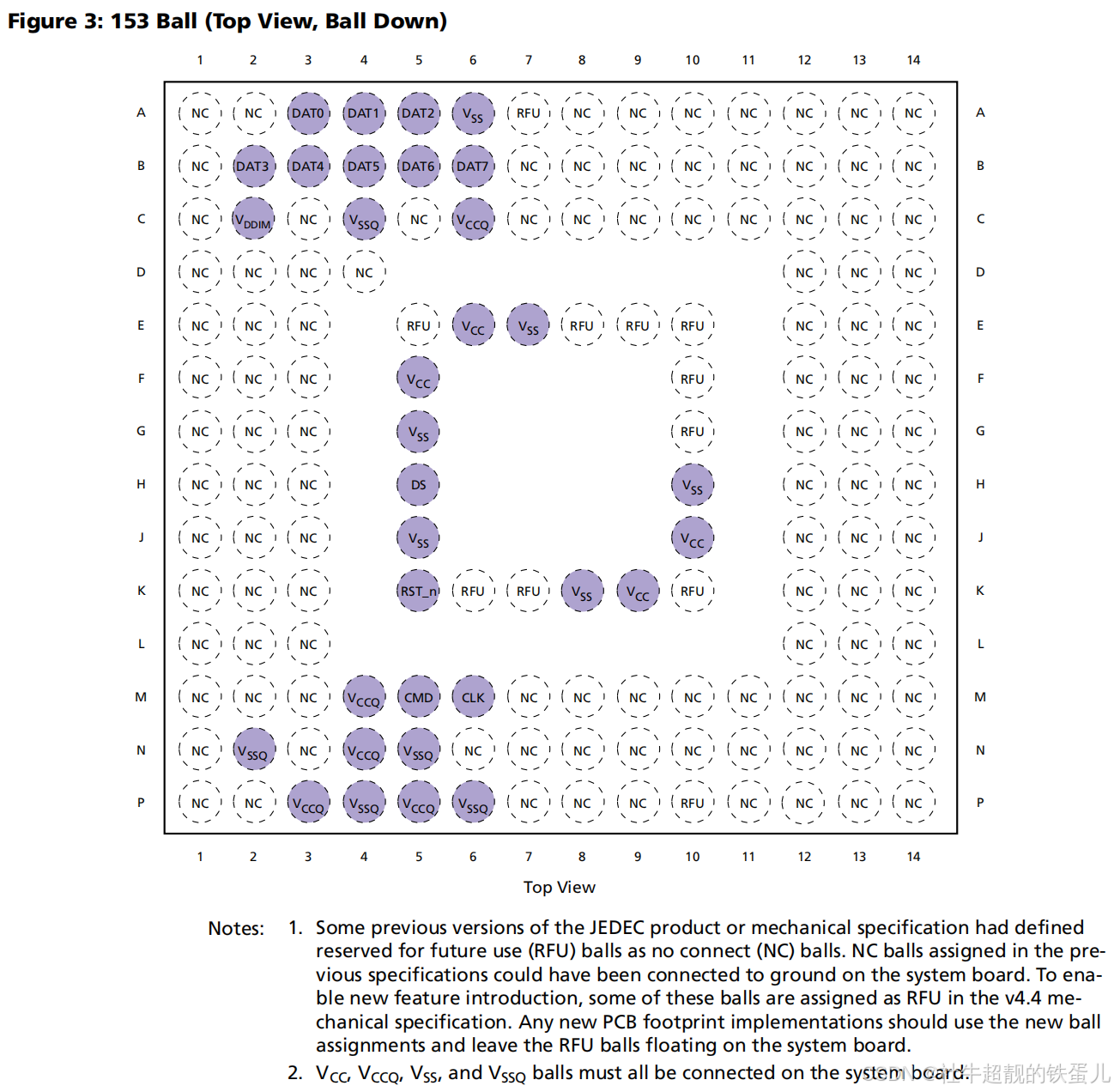

3.2 153个引脚信号分配

注意:

1.早期JEDEC产品或机械规范版本中,预留供未来使用的(RFU)焊球曾被定义为无连接(NC)焊球。根据旧版规范分配的NC焊球原本可直接接到系统地。为支持新功能的引入,v4.4机械规范将部分焊球重新划分为RFU。所有新增PCB焊盘布局均需采用新焊球分配方案,并保持RFU焊球在系统板上的浮动状态。

- VCC、VCCQ、VSS及VSSQ焊球必须全部接入系统板。

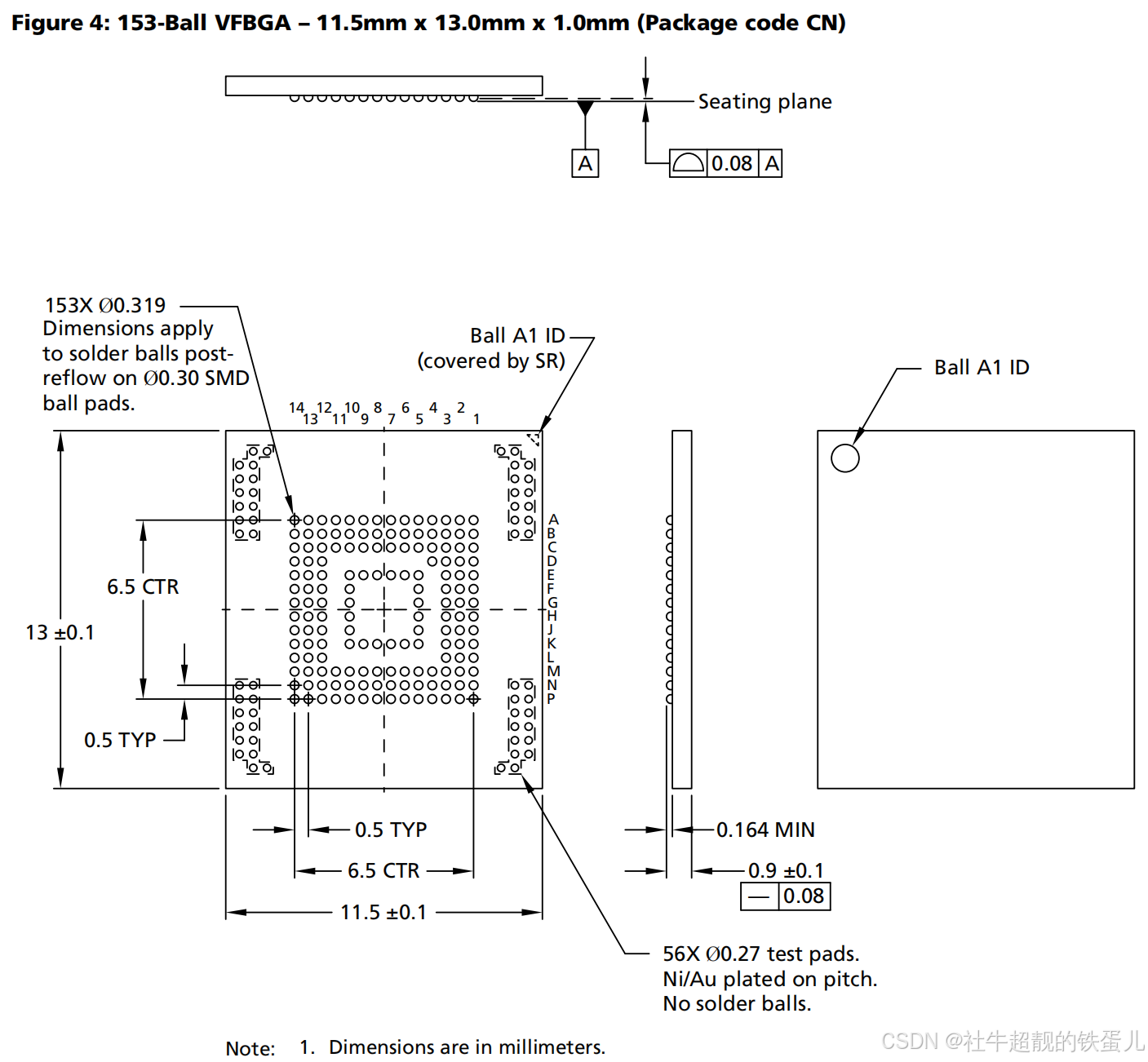

3.3 封装尺寸

153个Ball,VFBGA封装,11.5x13.0x1.0mm。

4、架构

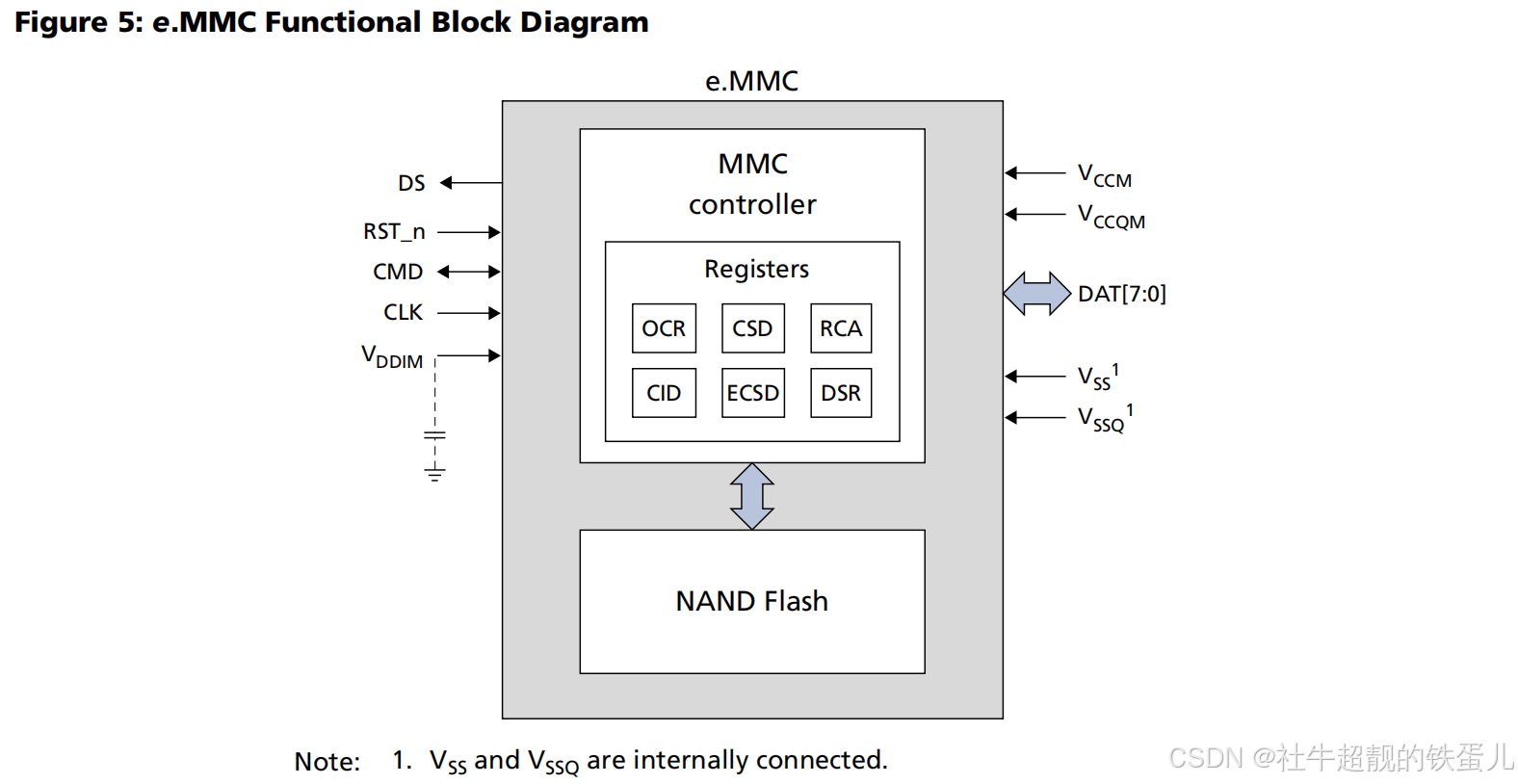

4.1 eMMC功能框图

4.2 MMC协议独立于NAND闪存技术

MMC规范定义了主机与设备之间的通信协议。该协议独立于设备内置的NAND闪存特性,由智能板载控制器统一管理。

控制器也负责逻辑块分配、坏块均衡等块管理功能,这些管理功能需要复杂的算法支持,并完全依赖于NAND闪存的技术规格(包括存储器类型或代数)。

由于这些管理功能由eMMC内部处理,因此对主机处理器而言完全透明。

4.3 缺陷和错误管理

美光电子(Micron e.MMC)采用先进的缺陷与错误管理技术。当检测到缺陷块时,设备会自动用备用块完全替换该缺陷块。这一过程对主机完全透明,不会影响用户分配的数据空间。

设备还内置纠错码(ECC,Error Correction Code)算法,确保数据完整性。为充分发挥这些先进技术的优势,并保障设备全生命周期内的数据正确加载与存储,主机需注意以下事项:

•在写入、读取和擦除操作后检查状态;

•避免在执行写入或擦除操作期间断电。

4.4 操作条件寄存器

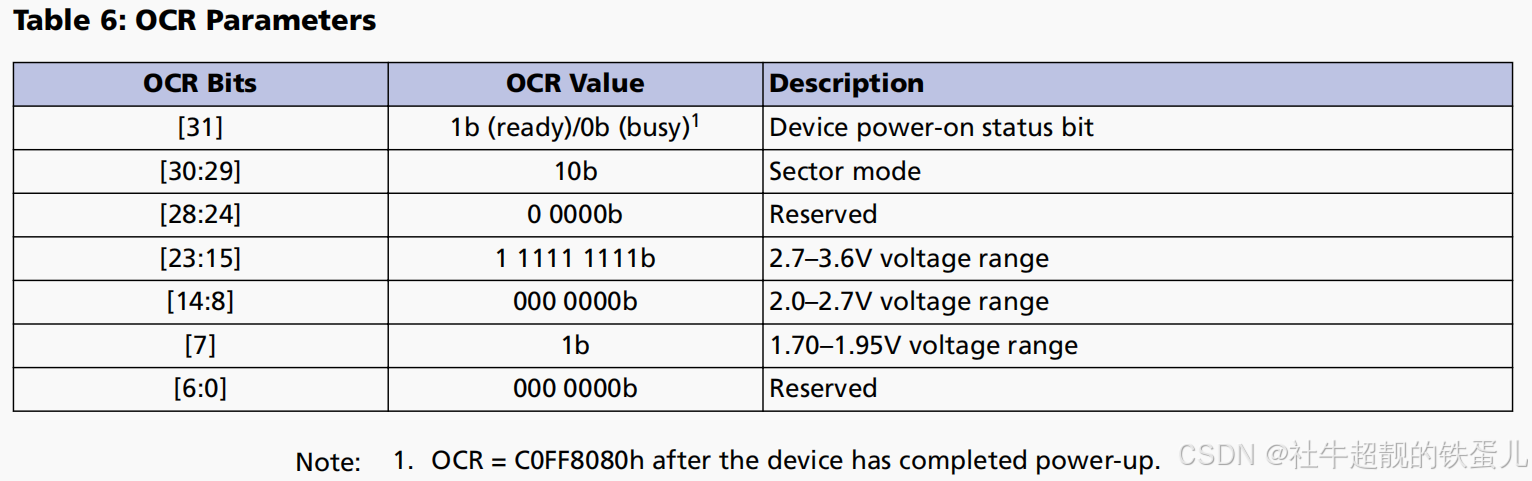

32位操作条件寄存器(OCR,Operation Conditions Register)保持eMMC的电压曲线和访问模式指示,此外,该寄存器还包括状态信息位。

4.5 CID寄存器

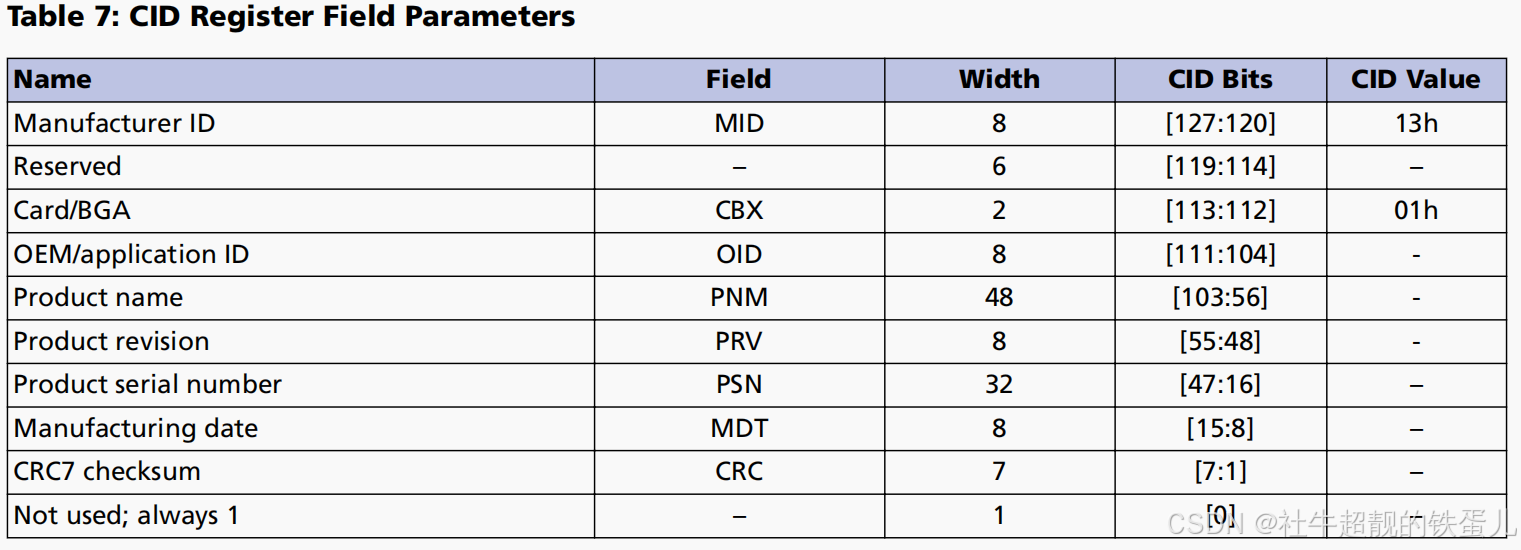

eMMC卡识别(CID,Card Identification Register)寄存器宽128位,它包含在卡识别阶段使用的设备识别信息,这是e.MMC协议所要求的。每个设备创建时都会有一个唯一的识别号。

4.6 CSD寄存器

eMMC卡专用数据(CSD,Card-Specific Data)寄存器用于提供设备内容访问的相关信息。该寄存器定义了数据格式、纠错类型、最大数据访问时长、数据传输速度,以及是否启用DS寄存器等功能。寄存器的可编程部分(Table 8: CSD Register Field Parameters表中标记为W或E的条目)可通过PROGRAM_CSD(CMD27)命令进行修改。

4.7 ECSD寄存器

512字节的扩展卡专用数据(ECSD,Extended Card-Specific Data)寄存器用于定义设备属性和选定模式。最高320字节为属性段,该段定义设备功能且主机无法修改;最低192字节为模式段,用于定义设备运行的配置模式。主机可通过SWITCH命令修改模式段的属性设置。

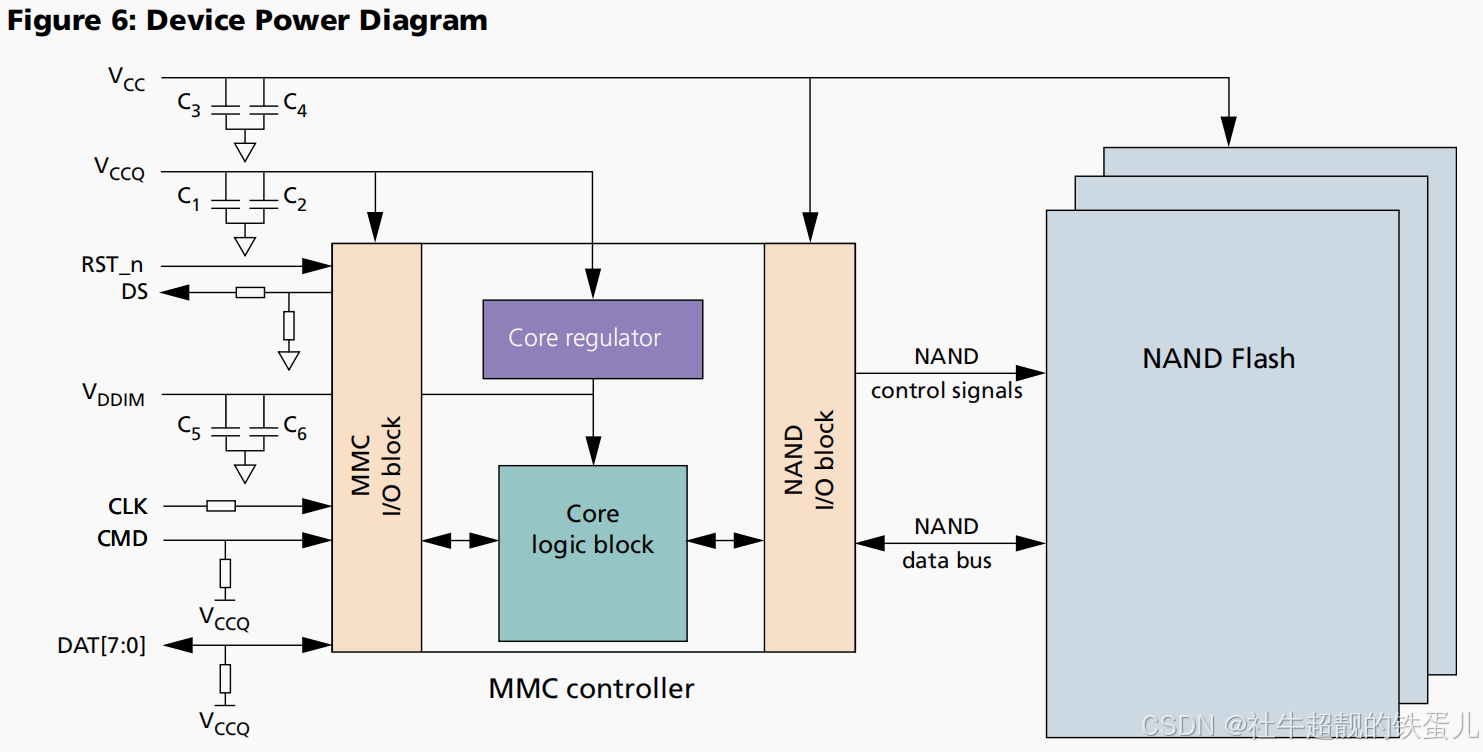

5、DC电气规格-器件电源

不同设备配置的设备电流消耗定义在ECSD寄存器的功率等级字段中。

VCC用于NAND闪存设备及其接口电压;

VCCQ用于控制器和eMMC接口电压。

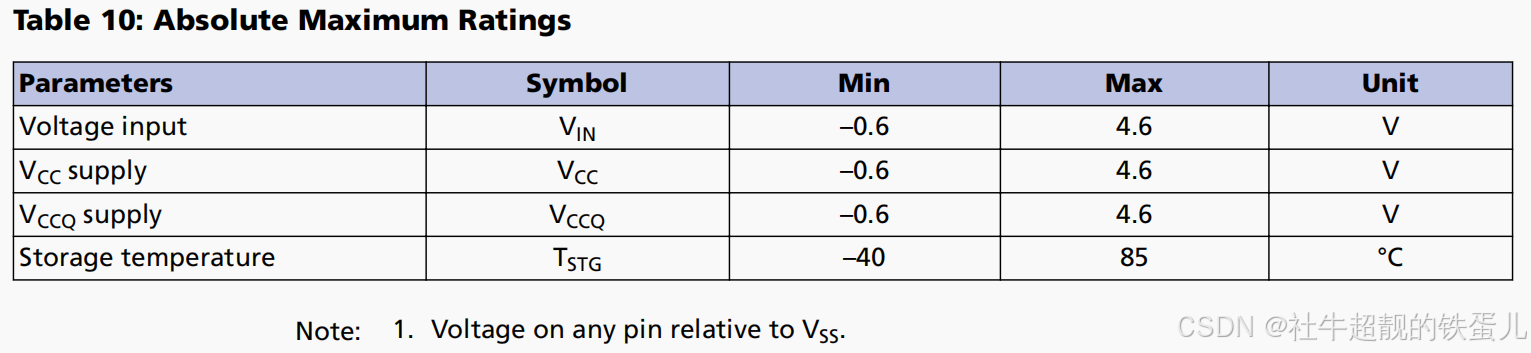

5.1 极限指标

5.2 电容和电阻设置

对CMD信号,上拉10K电阻。

对DAT[7:0]信号,上拉50K电阻。

对RST_n信号,上拉50K电阻。

对CLK/CMD/DS/DAT[7:0]控50Ω阻抗。

对CLK信号,加22Ω串阻。

对DS(DATA STROBE)信号,加22Ω串阻,下拉10~100K电阻。

VCCQ电容,C1=2.2uF,C2=0.1uF。

VCC电容,C3=2.2uF,C4=0.1uF。

VDDIM电容(Creg),C5=1uF,C6=0.1uF。此为内部电压节点不能连接到电源电压或接地。

注意事项:

1.用于防止总线浮空。

2.若主机未使用硬件复位(RST_n),则无需在RST_n线上设置上拉电阻(Extended_CSD[162]=00h)。

3.保持阻抗匹配。

4.建议采用此方案以补偿PCB板可能出现的阻抗失配问题。

5.耦合电容应尽可能与VCCQ和VSSQ端子紧密连接。

6.耦合电容应尽可能与VCC和VSS端子紧密连接。

7.耦合电容应尽可能与VDDIM和VSS端子紧密连接。