前言

PCI Express (PCIe)协议中,EIOS (Electrical Idle Ordered Set) 和 EIEOS (Electrical Idle Exit Ordered Set) 是在高速链路管理和状态切换过程中极为重要的特殊序列。下面做详细解释:

一、EIOS(Electrical Idle Ordered Set)

1. 定义及作用

EIOS是PCIe物理层在发送端进入"电气空闲(Electrical Idle)"状态之前,必须发送的特殊序列。

它用来通知接收端:链路即将进入电气空闲状态(即没有数据传输,线路进入低功耗/待机状态)。

2. EIOS的构成

不同编码模式下的EIOS

1)8b/10b编码(如PCIe 2.x/3.x低速率)

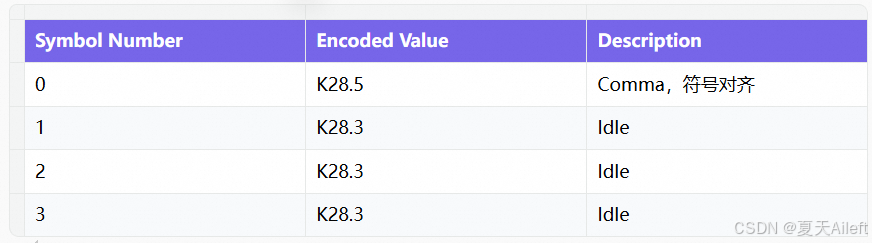

● EIOS = 1个K28.5(COM)符号 + 3个K28.3(IDL)符号。

● 详见下表:

● 发送端需要发出全部4个符号,接收端收到头4个(COM+任意2个IDL)即可视为EIOS已接收。

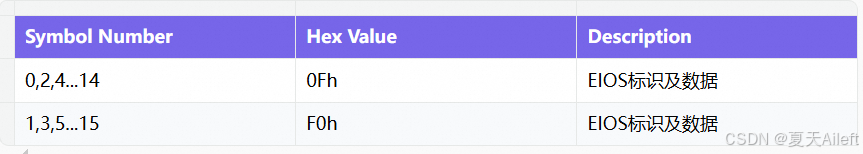

2)128b/130b 编码(如PCIe 4.0及更高速率)

● EIOS是一个特殊的 Ordered Set Block(有序块),具体符号见Table 4-32。

● 这个块的前4个编解码符号用于识别EIOS。

3)1b/1b 编码(PCIe 6.0 极高速率)

3. 截断与接收规则

● 截断(Truncation):最后一个EIOS序列在实际进入Idle状态时,可以在符号14或15提早结束(为支持某些编码模式下的时钟不对齐)。但接收方只要前4个符号匹配EIOS定义就可以正确判定链路进入空闲。

● 状态切换:发送最后一个EIOS所有符号后,发送端必须真正进入Idle状态。

4. 作用意义

● EIOS告知接收方链路即将Idle,可以收尾上一次传输的数据,进行电路省电和同步状态管理。

二、EIEOS(Electrical Idle Exit Ordered Set)

1. 定义及作用

EIEOS是从"电气空闲"状态返回到正常数据传输状态前要发送的特殊有序序列。

它通知接收器:链路即将退出Idle,准备恢复正常通信。

2. EIEOS的构成

● 8b/10b编码下,EIEOS包含:

○ K28.7(EIE)等特定标识符(不同协议版本有所不同)。

○ EIEOS会在你想要退出Idle、准备发恢复训练序列(FTS)之前发送。

● 其余编码下,用有序块识别。

● 详见协议相关章节,通常和FTS配套出现。

3. 与EIOS的区别

● EIOS:Idle前发,进入空闲

● EIEOS:Idle结束发,退出空闲、恢复数据传输

4. 作用意义

● EIEOS确保接收方正确检测到链路恢复,同步时钟和准备下一帧训练(FTS)或数据交换。

三、EIOS与EIEOS在链路训练和状态管理中的流程

- 正常数据传输

- 准备进入Idle

○ 发送EIOS (通知即将Idle) - 实际进入Idle状态

- 准备恢复数据传输

○ 发送EIEOS (通知即将恢复) - 发送FTS或数据帧,链路恢复激活

四、常见应用场景

● PCIe设备省电自动管理

● PCIe链路训练/恢复同步

● 热插拔、链路异常恢复

五、简明总结