系列文章目录

文章目录

PCI总线所存在的问题与PCIe的优势

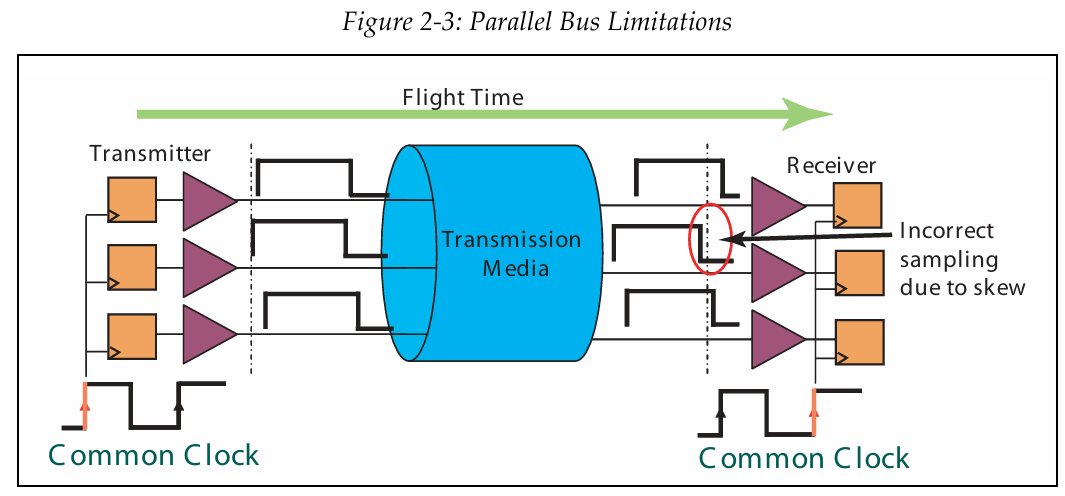

1. PCI总线的问题

- PCI总线要求信号从发送端到接收端所花费的时间(渡越时间)要小于一个始终周期,所以这就限制了频率的提升

- PCI总线使用的是公共时钟,因为时钟走线的原因,这就不可避免的产生了时钟偏斜,导致收发双方的时刻不一致。

- PCI总线采用的是并行总线,因为每条线路的走线不一样,所以信号到达接收端的延迟就不一样,这个就是信号偏斜。

2. PCIe总线的优势 - PCIe总线将时钟隐藏在信号中,在接收端可以通过信号跳变得到时钟,因此时钟频率不在收到限制;

- PCIe将时钟隐藏在数据中,接收端使用恢复后的时钟进行采样,因此也不会存在时钟偏斜的问题了;

- PCIe是串行传输总线,因此不再存在信号偏斜的问题。

PCIe链路

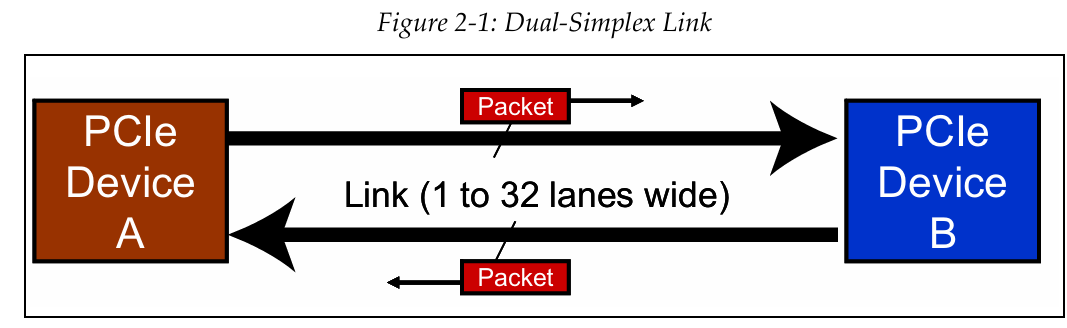

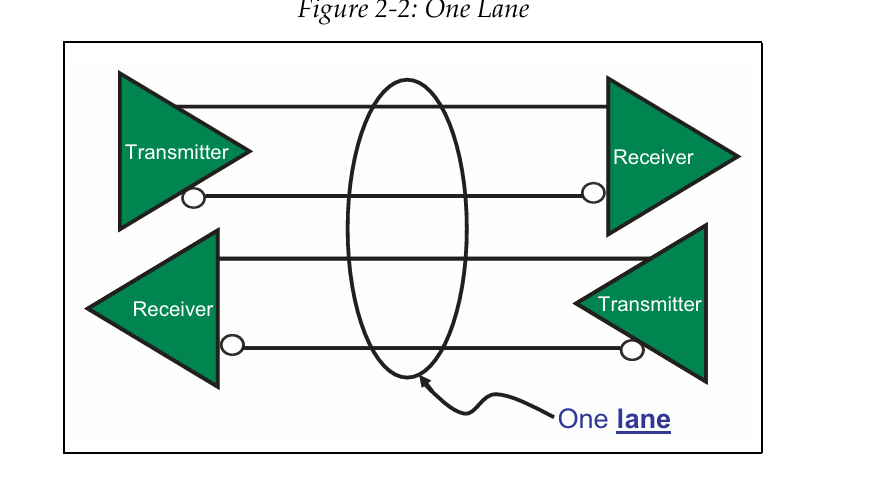

PCIe中用于描述设备之间信号传输路径的术语为"链路(Link)",它由一个或以上的接收发送对组成。这样的一对接收和发送被称为一个"通道(Lane)",协议规范允许一条链路内有 1、2、4、8、12、16 或 32 个通道。链路内通道的数量称为链路宽度,通常用 x1、x2、x4、x8、x16 以及 x32 来进行表示。

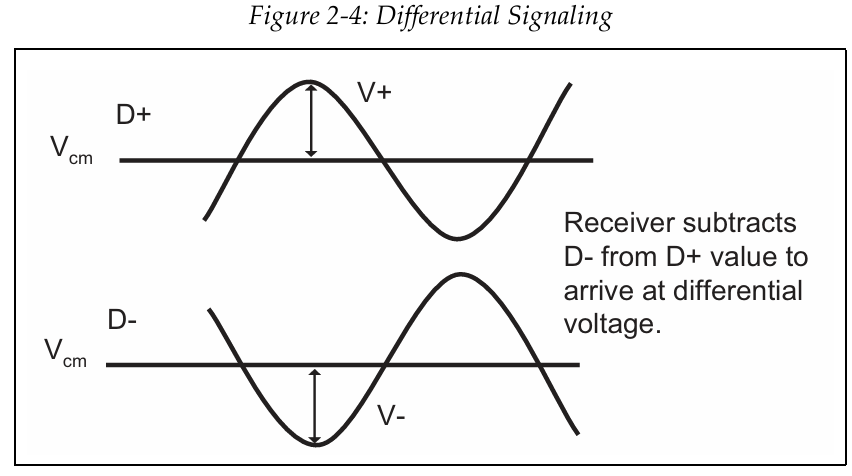

PCIe每个通道都使用差分信号进行传输,差分信号是指每次传输一个信号时同时发送它的正信号和负信号(D+ 和 D-,这两种信号振幅相同相位相反),当然,这样会将引脚增加一倍,但是相对于单端信号而言,差分信号在高速传输上的两个明显的优点足以抵消其引脚数方面的不足:它提高了噪声容限,并降低了信号电压。

差分信号是使用两根信号的差值进行传输的,所以若有一根信号线受到噪声的影响,另外一根也必然受到噪声的影响,这样电压差值是没有发生变化的,也就是信号传输不会变化。

PCIe带宽计算

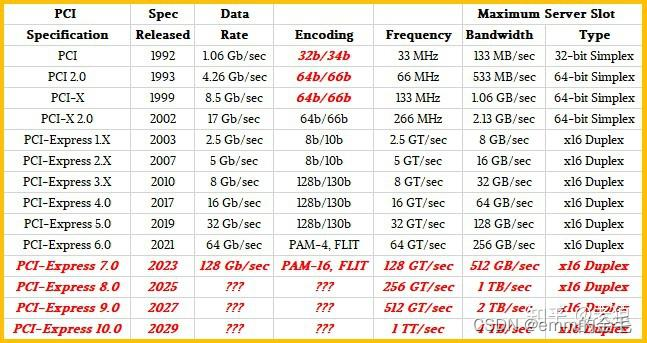

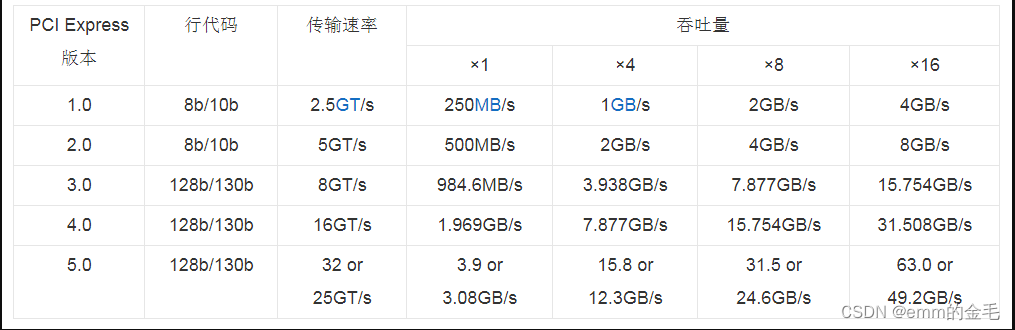

PCIe发展至今已经发展到第7代,1.0、2.0版本编码都采用的8B/10B编码,但是由于8B/10B编码带宽利用率低,所以在之后采用的是128B/130B编码。但是从PCIe6.0采用的是PAM-4,FLIT编码,之后的版本编码可能也会继续采用PAM编码。

可以看到PCIe每迭代一代,其传输速率是翻倍增长的。而PCIe常说的x1、x4、x8、x16代表的是通道的数量先来看一下PCIe1.0-PCIe5.6不同的通道个数的传输速率:

带宽计算:

GT/s代表的是"Giga Transfers Per Second"(编码后每秒传输多少个bit),对于PCIe1.0 x1来说,GT与GB之间的换算关系为:(2.5GT / 10)*8 = 2000 Mbps = 250MB/s,所以x4就是1GB/s,x8就是2GB/s。

到了PCIe3.0,因此采用的编码是128b/130b,2bit的开销可以忽略掉,所以换算公式可以变换为:8GT / 8 = 1Gbps

PCIe时钟恢复

前文说到PCIe总线是通过信号的跳变来恢复出时钟的,所以这就对传输的码字有了要求,那就是不能出现长连0,长连1,否则无法从信号中会恢复出时钟。所以从PCIe1.0就需要对所要传输的码字进行编码。

PCIe1.0采用的是8b/10b编码,这种编码采用映射的方式,保证每个10位块中"0"和"1"的数量差不超过2,并确保码流中长连1或0的数量不能超过5个,是一种确定的、非常严格的直流平衡编码。

但是8b/10b的冗余开销过大,所以PCIe3.0之后使用的是128b/130b编码,这种编码减少了冗余开销,但是128b到130b的映射结果太多,因此没有严格控制码字中1和0的数量,所以需要进行特殊的加扰处理,从而使得码字在统计结果上出现的概率为50%。

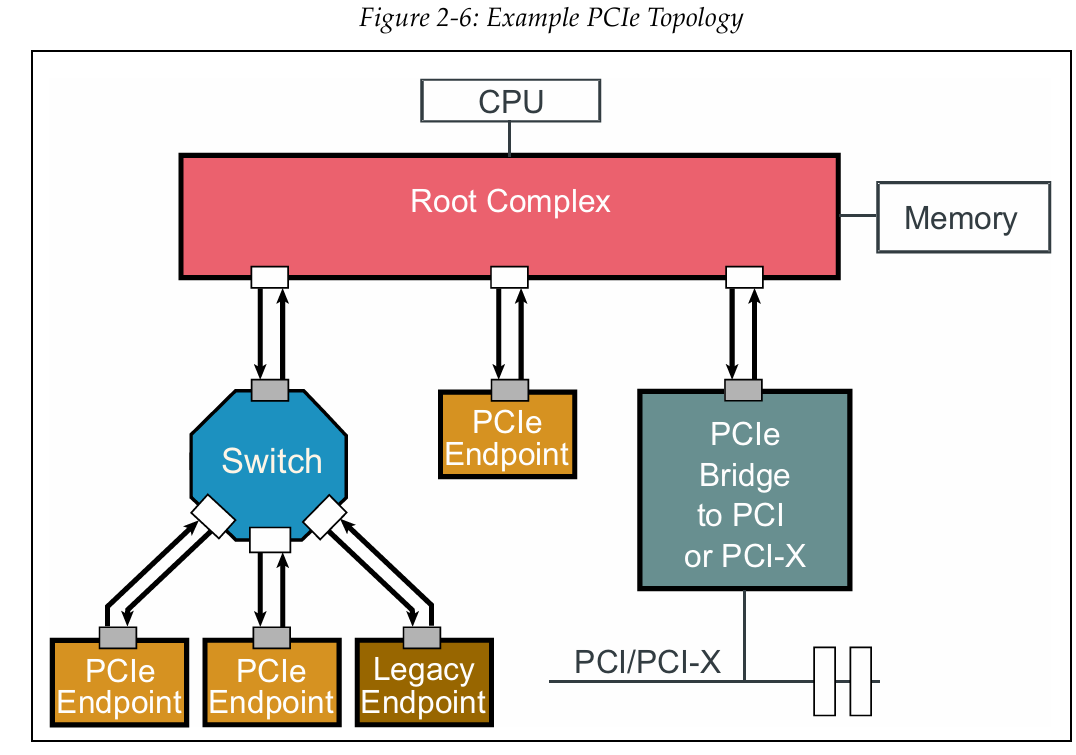

PCIe拓扑结构

下图是一个简单的PCIe拓扑结构,其中CPU被认为是PCIe层次结构的顶端,整体结构为树形结构,其主要目的是为了保持与PCI结构的后向兼容性。主要的组件包含如下:

- Root Complex:CPU与PCIe总线之间可能包含一系列的组件(处理器接口,DRAM接口等等),甚至包含多个芯片。将这些组件结合起来,称这一组件为根组件(Root Complex,RC)。其主要功能包括:启动枚举、地址翻译、数据路由、中断转发、电源 / 错误管控等。

- Switch:主要作用是为PCIe总线提供扩展能力,让一个总线能挂载更多的设备。主要包括1个Upstream Port(上游口),主要连接RC 或上层 Switch;多个Downstream Port(下游口),连接设备或下层 Switch主,要功能包括:扩展端口、路由转发、拓扑构建等。

- Bridge:桥的主要作用是为其他总线提供接口,例如PCI或者PCI-X,主要起到了协议转换的作用。

- Endpoint:端点就是PCIe总线结构中的一些设备了,例如网卡、声卡等。这些端点既可以作为总线上事务的发起者、也可以作为是事务的完成者。Endpoint又分为Native PCIe Endpoint(原生PCIe端点)和Legacy PCIe Endpoint(传统PCIe端点)。原生PCIe端点是指那些一开始就是PCIe总线量身适配的端点,也可以说是"亲儿子"。而传统PCIe端点就是指代那些一开始为PCI或PCI-X设计的端点,可以说是"前朝遗孤",还保存着一些不好的习惯,例如:支持IO空间、支持IO事务等。

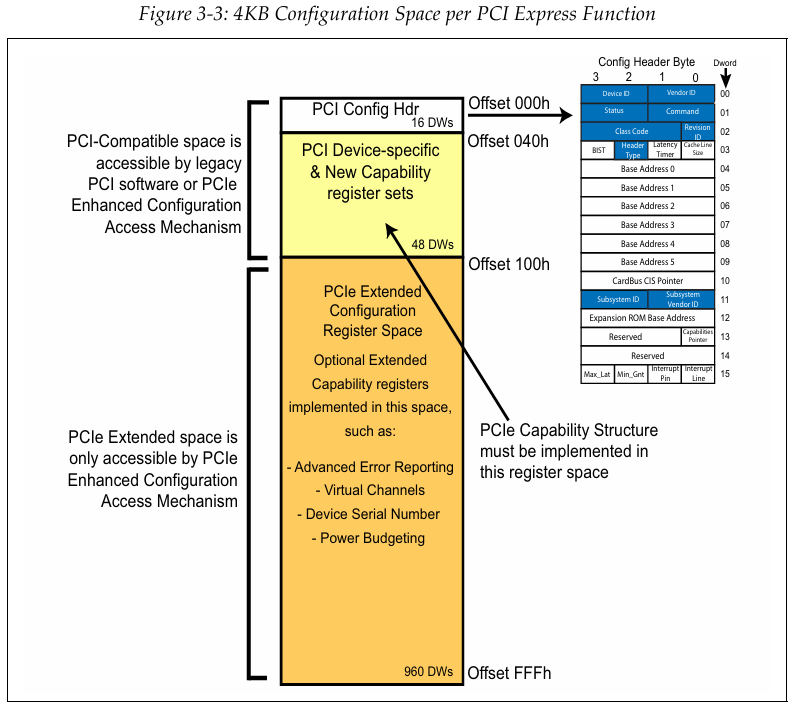

PCIe配置空间

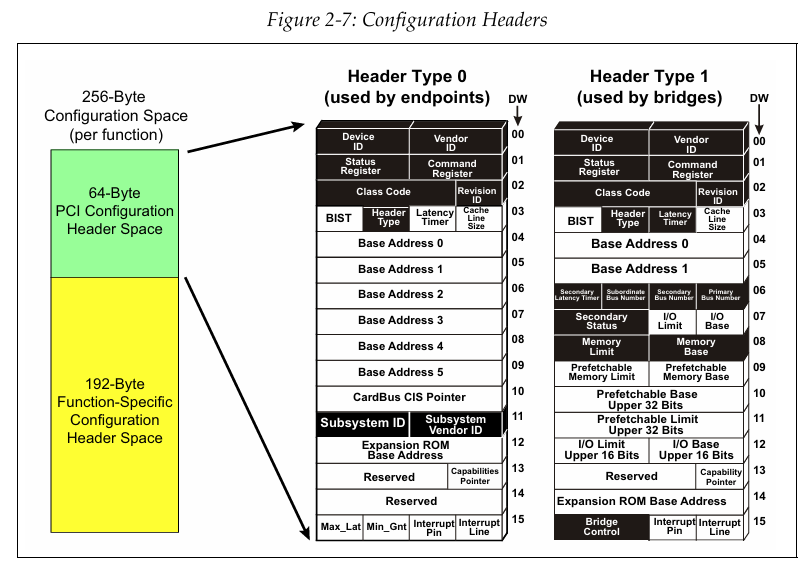

PCIe总线为了与PCI总线保持前向兼容,所以前256Byte的配置头是和PCI基本一致的,但是PCIe的配置空间扩展至了4096Byte,并且PCIe明确了Type0和Type1这两种配置空间的主要用途,Type0主要用于Endpoint,Type1主要用于Brige。一句话:PCIe 配置空间 = PCI 256 字节 + 3.75KB 新特性空间,既保证了老设备能用,又支撑了所有高速、复杂的新功能。

后面的东西之后再看~