曼彻斯特编解码:数字世界的"摩斯密码"与FPGA高效实现

一串简单的电平跳变,如何承载时钟与数据的双重奥秘?

在数字通信的世界里,数据的可靠传输离不开高效的编码技术。曼彻斯特编码(Manchester Encoding)作为一种经典的自同步编码方案,凭借其独特的设计思想,解决了数据传输中的时钟同步与直流平衡难题。

本文将带您深入探索曼彻斯特编码的奥秘,并揭秘如何利用现场可编程门阵列(FPGA)实现高效的编解码系统。

一、曼彻斯特编码:数据与时钟的完美共舞

编码原理:跳变即信息

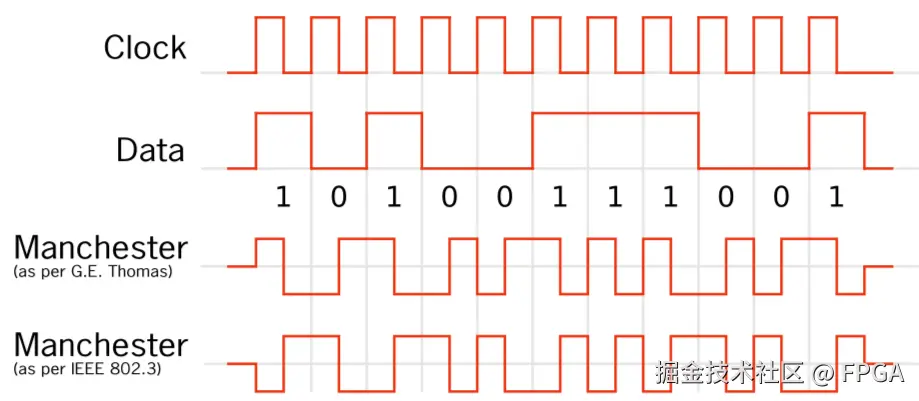

曼彻斯特编码的核心在于利用电平跳变传递双重信息 。在每一位数据的中点位置,都会发生一次强制性的电平跳变,这个跳变既提供了时钟同步信号 ,也携带了数据信息本身:

- "0"的编码:从低电平跳变到高电平(↑)

- "1"的编码:从高电平跳变到低电平(↓)

图示:曼彻斯特编码中"0"和"1"的波形表示,每个比特中点都有跳变

技术优势:为何选择曼彻斯特?

- 自同步能力:每个比特中间的跳变使接收端能够精确提取时钟信号,无需独立的时钟传输通道。

- 无直流分量:编码中"0"和"1"的对称设计确保了信号中不存在直流偏移,适合变压器耦合传输和长距离通信。

- 强抗干扰性:通过检测中点跳变而非绝对电平值,有效抵抗噪声和信号畸变。

- 错误检测机制:异常跳变模式(如缺失跳变)可被识别为传输错误。

编码效率的代价

曼彻斯特编码的主要缺点是编码效率仅为50% 。由于每个数据位需要两个电平状态表示,实际传输带宽仅有一半用于数据传输。

例如,在10Mbps的以太网中(使用曼彻斯特编码),实际数据速率仅为5Mbps。

编码家族:曼彻斯特的变体

根据应用场景的不同,曼彻斯特编码发展出多种变体:

表:曼彻斯特编码家族对比

| 编码类型 | 跳变规则 | 代表应用 | 核心优势 | 技术特点 |

|---|---|---|---|---|

| 标准曼彻斯特 | 比特中间跳变: • 上升沿(低→高)= 0 • 下降沿(高→低)= 1 | IEEE 802.3以太网 | 标准化程度高 | 每个比特周期包含两次电平变化 |

| 曼彻斯特Ⅱ型 | 数据位同标准曼彻斯特 同步头: • 命令字:1.5T高+1.5T低 • 数据字:1.5T低+1.5T高 | MIL-STD-1553B航空总线 | 通过同步头区分命令/数据 | 同步头包含1.5比特宽度的电平变化 |

| 差分曼彻斯特 | 比特中间始终跳变 比特开始处: • 有跳变 = 0 • 无跳变 = 1 | IEEE 802.5令牌环网 | 抗极性反转干扰 | 时钟信息更稳定,对信号极性不敏感 |

| Bi-φ-L码 | 比特中间始终跳变 比特开始处: • 有跳变 = 1 • 无跳变 = 0 | RFID ISO 14443 | 与差分曼彻斯特逻辑相反 | 高频RFID常用 |

| G.E. Thomas变体 | 比特中间跳变: • 上升沿(低→高)= 1 • 下降沿(高→低)= 0 | 早期专有系统 | 与标准曼彻斯特逻辑相反 | 现已较少使用 |

表:各类型时钟恢复机制对比

| 编码类型 | 时钟提取方式 | 抗时钟抖动能力 |

|---|---|---|

| 标准曼彻斯特 | 依赖每个比特中间的固定跳变 | 中等 |

| 曼彻斯特Ⅱ型 | 同步头提供粗同步 + 数据位跳变精同步 | 高 |

| 差分曼彻斯特 | 比特开始处的可选跳变 + 中间强制跳变 | 最高 |

| Bi-φ-L码 | 同差分曼彻斯特 | 最高 |

应用场景补充说明:

差分曼彻斯特作为曼彻斯特编码的改进版本,通过比特起始处的电平变化表示数据:起始处有跳变代表0,无跳变代表1。这一设计解决了极性反转时的译码错误问题,特别适合电气环境恶劣的工业场景。

二、无处不在的身影:曼彻斯特编码应用场景

1. 航空电子神经:1553B数据总线

在军用和民用飞机中,MIL-STD-1553B总线采用曼彻斯特Ⅱ型码作为物理层编码标准,传输速率1Mbps35。总线上传输三种类型字:命令字、状态字和数据字,每种字长20位(3位同步头+16位数据+1位奇校验)。

曼彻斯特编码在这里的独特价值在于:

- 通过同步头方向(先正后负或先负后正)区分字类型

- 丰富的跳变确保变压器耦合可靠工作

- 严格的时序规范满足航空安全要求

2. 工业控制网络:稳定传输的守护者

在工业现场控制网络中,曼彻斯特编码因其无直流分量 和抗干扰能力强的特性,成为恶劣环境下的理想选择。典型应用包括:

- 数控测井系统

- 井下数据传输

- 电力线通信

- 工业传感器网络

例如,在油井测量中,曼彻斯特编码能够抵抗井下高温高压环境下的信号畸变,确保数据可靠上传。

3. 射频识别(RFID)系统

125kHz低频RFID系统(如门禁卡)广泛采用曼彻斯特编码。读卡器通过谐振电路发射载波,卡片通过负载调制返回曼彻斯特编码的ID信息。其解码过程包括:

- 谐振电路接收信号

- 检波与滤波放大

- 同步头检测(9个连续"1")

- 曼彻斯特码到二进制转换

三、FPGA实现:灵活高效的硬件方案

为何选择FPGA?

传统曼彻斯特编解码方案存在明显局限:

- 专用芯片(如HD-6408/6409):速率受限(≤1Mbps),灵活性差

- 微处理器软件方案:受CPU时钟限制,速率通常低于1Mbps

FPGA方案凭借其并行处理能力 和硬件可编程特性,成为高速曼彻斯特编解码的理想平台:

- 可实现超过10Mbps的高速编解码

- 支持灵活协议定制

- 可集成编解码与协议处理于单一芯片

- 资源消耗低(通常仅需200-400逻辑单元)

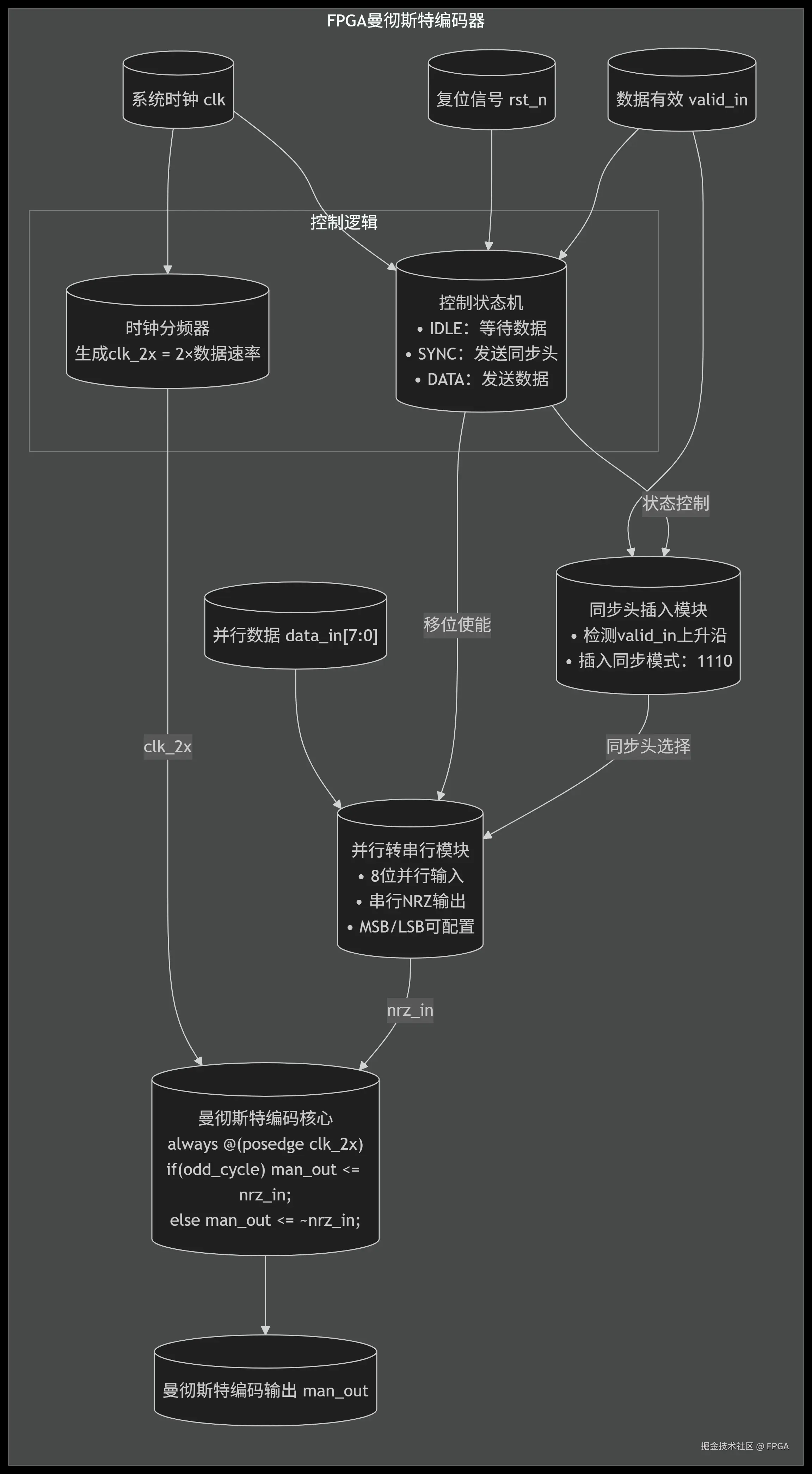

FPGA编码器设计

图示:基于FPGA的曼彻斯特编码器结构框图

编码器核心模块包括:

1. 同步头添加

- 在有效数据前添加2-4个周期的同步头(如高电平)

- 提供帧起始标志,辅助接收端时钟同步

2. 并行转串行(P2S)

- 使用移位寄存器将并行数据转为串行NRZ码

- 支持MSB/LSB优先可配置

3. 曼彻斯特编码核心

创新编码逻辑避免传统异或方式产生的毛刺:

arduino

// 基于双倍时钟的毛刺消除编码

always @(posedge clk_2x) begin

if(odd_cycle) // 奇数周期

man_out <= nrz_data;

else // 偶数周期

man_out <= ~nrz_data;

end此方案利用二倍于数据速率的时钟,交替输出NRZ码及其反相。

FPGA解码器设计:三大技术路线

路线1:数字锁相环(DPLL)方案

传统方案采用数字锁相环从信号中恢复时钟:

ini

// 超前-滞后锁相环核心

edge_detector u1 (.data_in(data), .clk(clk_16x), .edge_pulse(e));

assign d = ~c;

assign g = e & c; // 生成滞后脉冲

assign h = e & d; // 生成超前脉冲

phase_adjust u2 (.add(h), .sub(g), .clk(clk_16x), .clk_out(c));该方案通过调整时钟相位跟踪跳变沿,但消耗资源较多且需精密时序控制。

路线2:数字积分判决法(创新方案)

新型数字积分方案无需时钟恢复,具有优异抗噪性能:

arduino

// 数字积分器核心代码

always @(posedge clk_96M) begin

if(syn_detected) begin

if(data_in)

integrator <= integrator + 1; // 高电平+1

else

integrator <= integrator - 1; // 低电平-1

// 跳变沿检测与判决

if(edge_detected) begin

if(integrator > THRESH_HIGH)

decoded_bit <= 1'b1;

else if(integrator < THRESH_LOW)

decoded_bit <= 1'b0;

integrator <= 0; // 重置积分器

end

end

end工作原理:

-

用高频时钟(≥16×数据率)采样

-

高电平+1,低电平-1

-

在跳变沿时刻判断积分值:

- 正大值 → 解码为"1"

- 负大值 → 解码为"0"

-

加入误差容限(如±N/4)抵抗噪声

路线3:采样计数器法

折中方案采用高频采样与多数判决:

-

16倍过采样每个比特

-

前8次采样高电平计数为tHigh

-

判决规则:

- tHigh ≥ 6 → 解码为"1"

- tHigh < 6 → 解码为"0"

表:FPGA曼彻斯特解码方案对比

| 方案 | 资源消耗 | 最高速率 | 抗噪能力 | 时钟同步要求 |

|---|---|---|---|---|

| DPLL锁相环 | 高(~350LE) | 10Mbps | 中等 | 严格同步 |

| 数字积分法 | 中(~230LE) | 6Mbps@96MHz | 强 | 宽松(±10%误差) |

| 采样计数器 | 低(~200LE) | 2Mbps | 中等 | 中等 |

四、性能优化与工程实践技巧

1. 同步头增强设计

为提升帧同步可靠性,可采用复合同步头:

r

// 改进的同步头结构

同步头 = 1.5T高电平 + 1.5T低电平 + 正常数据1553B总线使用此方式区分命令/状态字与数据字。

2. 并行CRC校验

为保障数据完整性,FT3帧格式采用多项式X¹⁶+X¹³+X¹²+X¹¹+X¹⁰+X⁸+X⁶+X⁵+X²+1生成CRC校验码。FPGA实现时采用并行CRC算法大幅提升效率:

ini

// 并行CRC-16计算模块

module crc16_parallel(

input [7:0] data_in,

input crc_en,

output reg [15:0] crc_out

);

always @(posedge clk) begin

if(crc_en) begin

crc_out[0] = data_in[0]^data_in[1]^...^crc_out[15];

crc_out[1] = data_in[1]^data_in[2]^...^crc_out[0];

// ... 优化组合逻辑

end

end

endmodule3. 状态机优化

采用Mealy状态机高效控制解码流程:

ini

// 四状态解码状态机

parameter [3:0]

IDLE = 4'b0001, // 空闲态:等待同步头

SYNC_DETECT = 4'b0010, // 同步头检测态

DATA_DECODE = 4'b0100, // 数据解码态

FRAME_CHECK = 4'b1000; // 帧校验态

// 状态寄存器声明

reg [3:0] current_state, next_state;

// 状态转移逻辑

always @(posedge clk or posedge rst) begin

if(rst)

current_state <= IDLE;

else

current_state <= next_state;

end

// 下一状态逻辑

always @(*) begin

next_state = current_state; // 默认保持当前状态

case(current_state)

IDLE: if(sync_pulse) next_state = SYNC_DETECT;

SYNC_DETECT: if(valid_sync) next_state = DATA_DECODE;

// ... 状态转移

endcase

end此设计在1553B接口中广泛应用。

五、未来发展与挑战

随着工业物联网和5G的发展,曼彻斯特编码面临新机遇与挑战:

-

高速化需求:通过FPGA流水线和并行处理,将曼彻斯特编解码速率提升至100Mbps以上

-

自适应能力:开发速率自适应解码器,动态调整采样频率

-

IP核标准化:构建可配置的曼彻斯特编解码IP核,支持:

- 多协议兼容(I/Ⅱ型、差分)

- 可编程同步头

- 在线速率检测

-

AI增强解码:利用机器学习算法处理畸变信号,如:

- 深度学习波形识别

- 神经网络时钟恢复

结语:古老编码的新生

曼彻斯特编码作为数字通信领域的"古典技术",在FPGA等现代硬件平台上焕发出新的生命力。其优雅的设计思想------将时钟与数据合二为一------依然影响着新一代通信协议的制定。

通过FPGA实现曼彻斯特编解码不仅具有工程实用价值,更是理解数字通信底层原理的绝佳途径。无论是工业控制、航空航天还是物联网传感网络,这种简洁可靠的编码技术仍在守护着比特流的精确传输。

技术的生命力不在于复杂,而在于解决本质问题的智慧。