一、简介

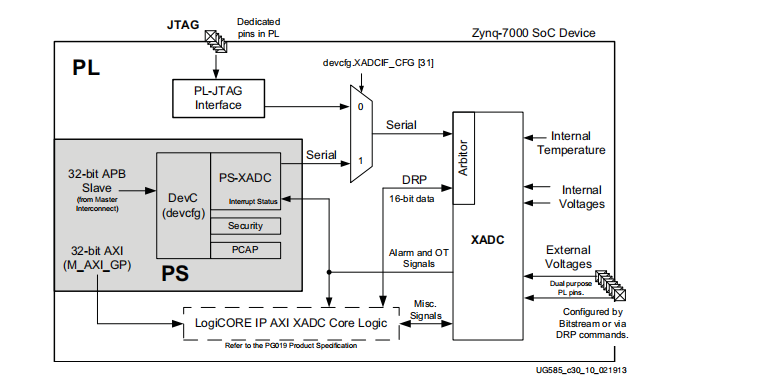

Xilinx模拟混合信号模块(简称XADC)是一个硬宏。它具有JTAG和DRP接口,用于访问7系列fpga中的XADC状态和控制寄存器。Zynq-7000 SoC器件增加了第三个接口PS-XADC接口,用于PS软件控制XADC。Zynq-7000 SoC器件结合了灵活的模数转换器和可编程逻辑,以满足广泛的模拟数据采集和监控要求。XADC是更大的模拟混合信号(AMS)主题的一部分,它是模拟和数字电路的组合。

XADC具有两个12位每秒1兆采样(MSPS)的adc,带有独立的轨道和保持放大器,一个模拟多路复用器(多达17个外部模拟输入通道),以及片上热传感器和片上电压传感器。两个adc可以配置为同时采样两个外部输入模拟通道。轨道和保持放大器支持一系列模拟输入信号类型,包括单极,双极和差分。模拟输入可以在1 MSPS的采样率下支持500 KHz的信号带宽。外部模拟多路复用器可用于增加支持的外部通道数量,而无需额外的封装引脚成本。

XADC可选地使用片上参考电路,从而消除了对基本片上温度和电源轨监测的外部有源元件的需求。为了充分发挥adc的12位性能,建议使用外部1.25V参考IC。

XADC是用硬逻辑实现的,位于PL电源域中。PS- xadc接口是PS的一部分,可以在不编程PL的情况下由PS APU访问。配置PS-XADC接口、使用PL- jtag或DRP接口、操作XADC都需要上电。系统级框图如上图所示。

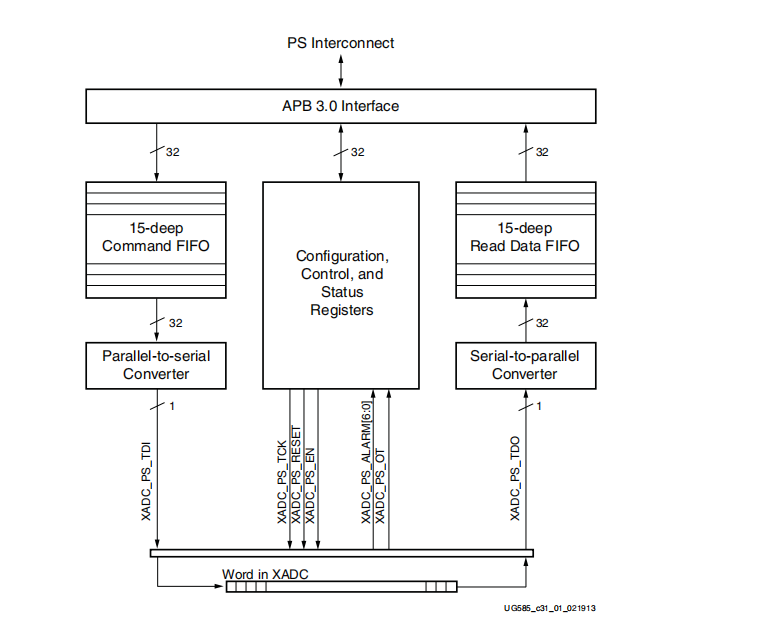

PS-XADC接口通常由在APU中执行的软件控制。软件将32位命令和nop写入命令FIFO。命令FIFO输出由串行通信通道序列化为XADC的32位数据包。数据包之间有一个可编程的空闲间隙(IGAP)时间,允许XADC有时间加载读取数据以响应前一个数据包。对于从命令FIFO移出的每一个相应的字被移入读数据FIFO。在DRP读命令的情况下,当它被移出命令FIFO时,XADC_DRP的DR寄存器的旧内容被移出。在IGAP时间之后,当前DRP读取的结果在XADC DRP的DR寄存器中可用。当TXFIFO的下一个命令被移出时,DR寄存器中当前读取的结果被移到RDFIFO中。

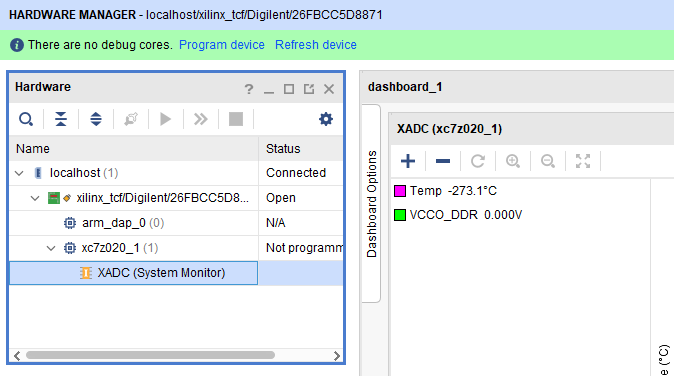

二、第一种是用vivade观察。烧录程序后通过JATG的方式观察温度和各种值。

1、进入VIVADE下载程序界面,下载程序。

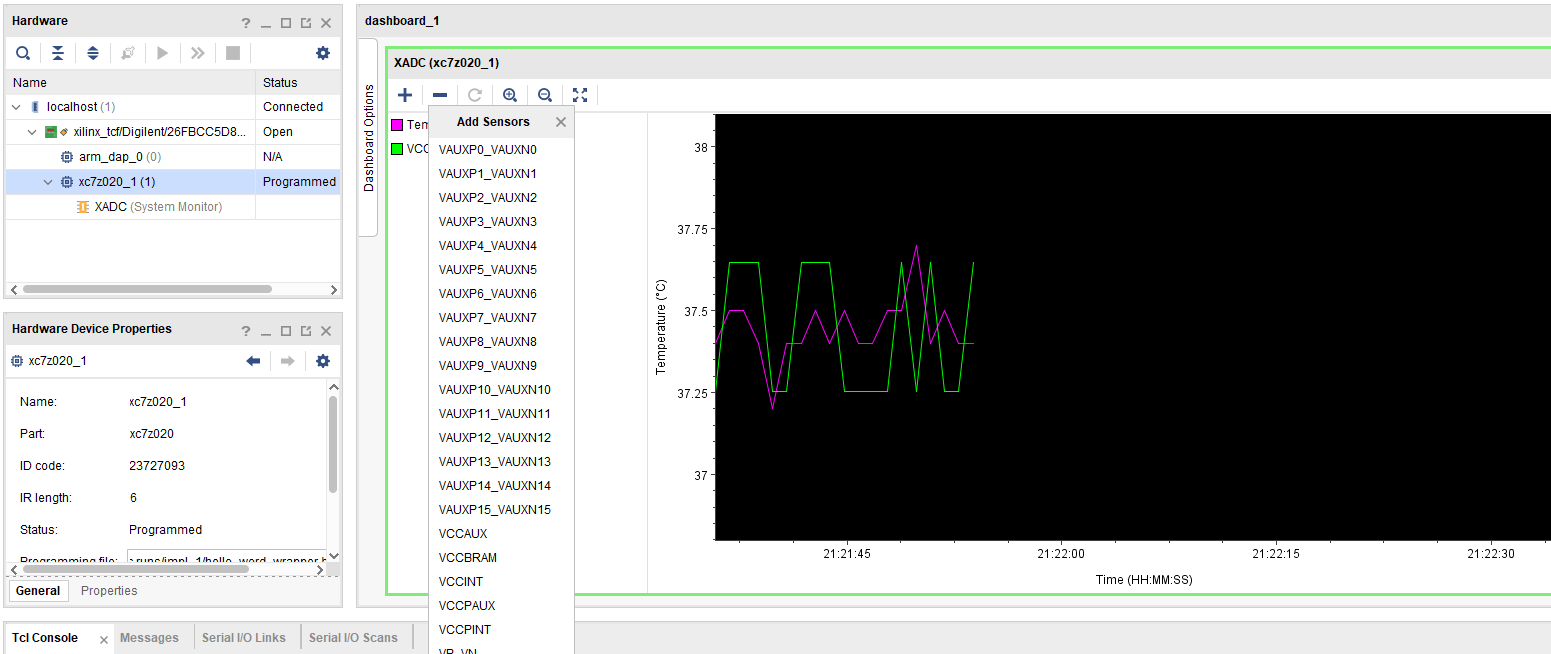

2、双击XADC后默认点击OK。右侧就是芯片内部温度等数值。可以自己手动添加需要观察的值。

三、第二种是通过PS侧编写软件代码通过写入命名读取数值。烧录打开串口可以看见数据。我这里不知道为什么读取不到数据但是代码又没有问题。

#include "stdio.h"

#include "xparameters.h"

#include "xadcps.h"

#include "xstatus.h"

#include "sleep.h"

#define XADC_DEVICE_ID XPAR_XADCPS_0_DEVICE_ID

XAdcPs_Config *ConfigPtr_xadc;

XAdcPs xadc;

int main()

{

printf("start\n");

u32 temp_chip_u;

u32 temp_ddr_u;

float temp_chip_f;

float temp_ddr_f;

//XADC初始化

ConfigPtr_xadc = XAdcPs_LookupConfig(XADC_DEVICE_ID);

if (ConfigPtr_xadc == NULL) {

return XST_FAILURE;

}

XAdcPs_CfgInitialize(&xadc, ConfigPtr_xadc,ConfigPtr_xadc->BaseAddress);

//设置为安全模式

XAdcPs_SetSequencerMode(&xadc, XADCPS_SEQ_MODE_SAFE);

while(1)

{

temp_chip_u = XAdcPs_GetAdcData(&xadc, XADCPS_CH_TEMP);

temp_chip_f = XAdcPs_RawToTemperature(temp_chip_u);

temp_ddr_u = XAdcPs_GetAdcData(&xadc, XADCPS_ATR_VCCPDRO_LOWER);

temp_ddr_f = XAdcPs_RawToTemperature(temp_ddr_u);

printf("On Chip Temperature: %f\n",temp_chip_f);

printf("VCCPDRO Lower Alarm Reg , Zynq: %f\n",temp_ddr_f);

sleep(5);

}

return XST_SUCCESS;

}