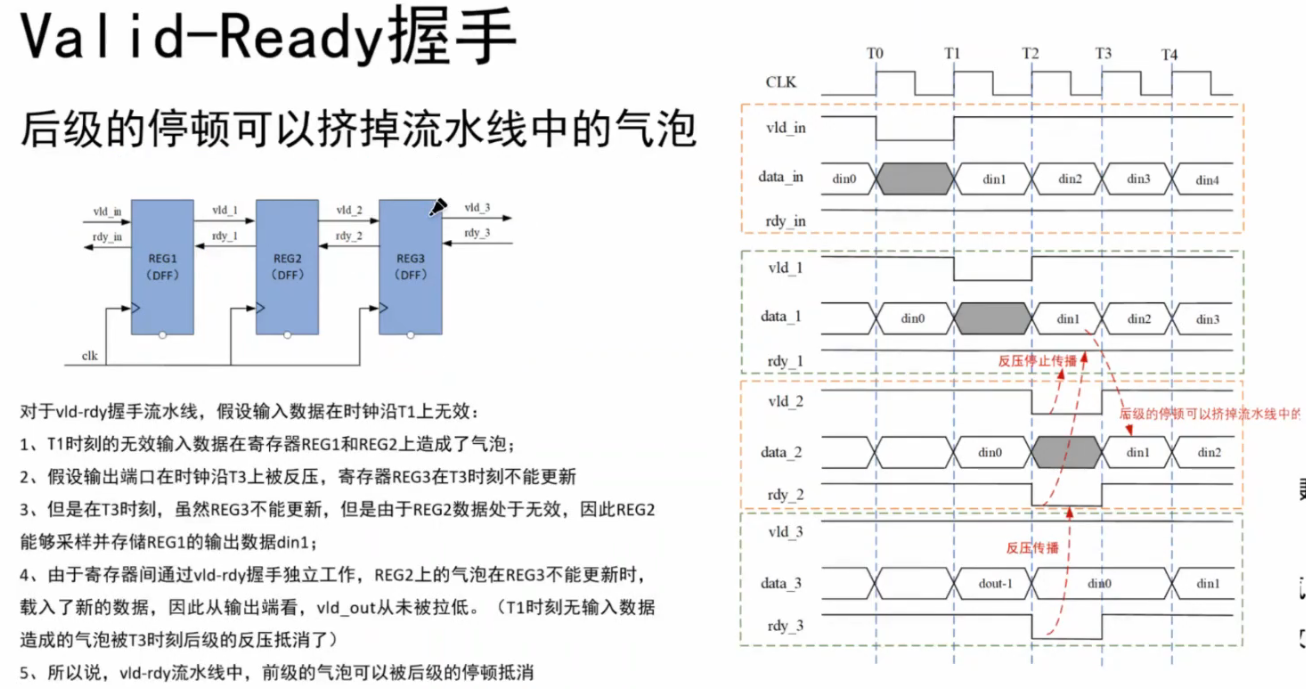

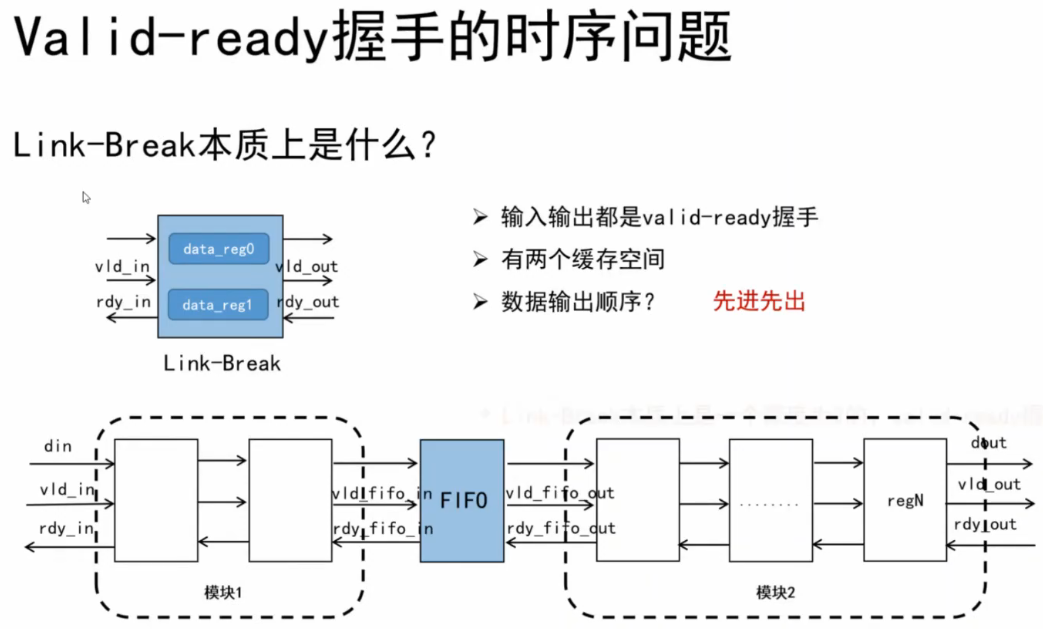

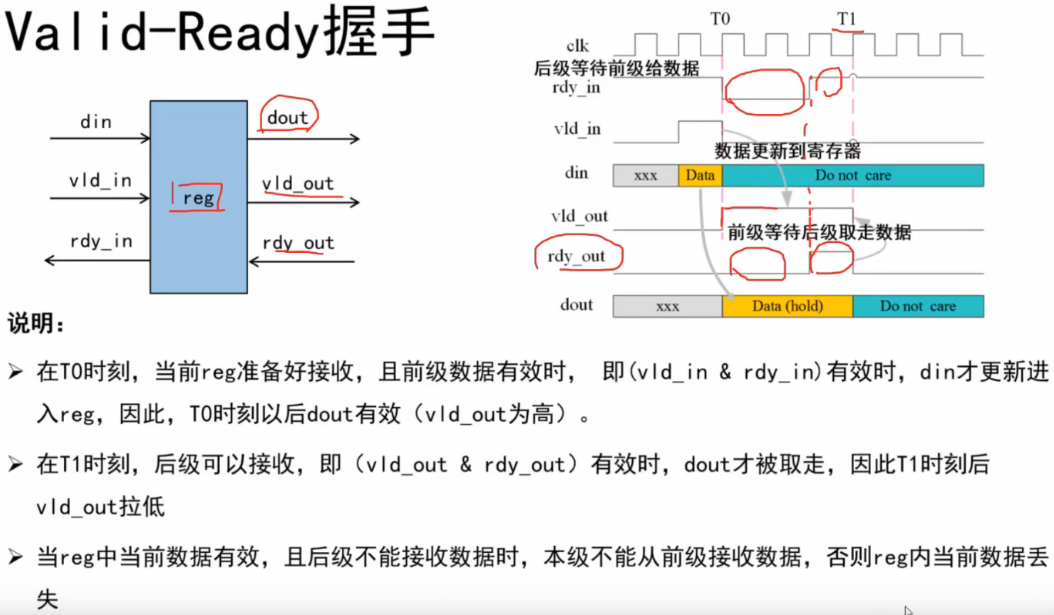

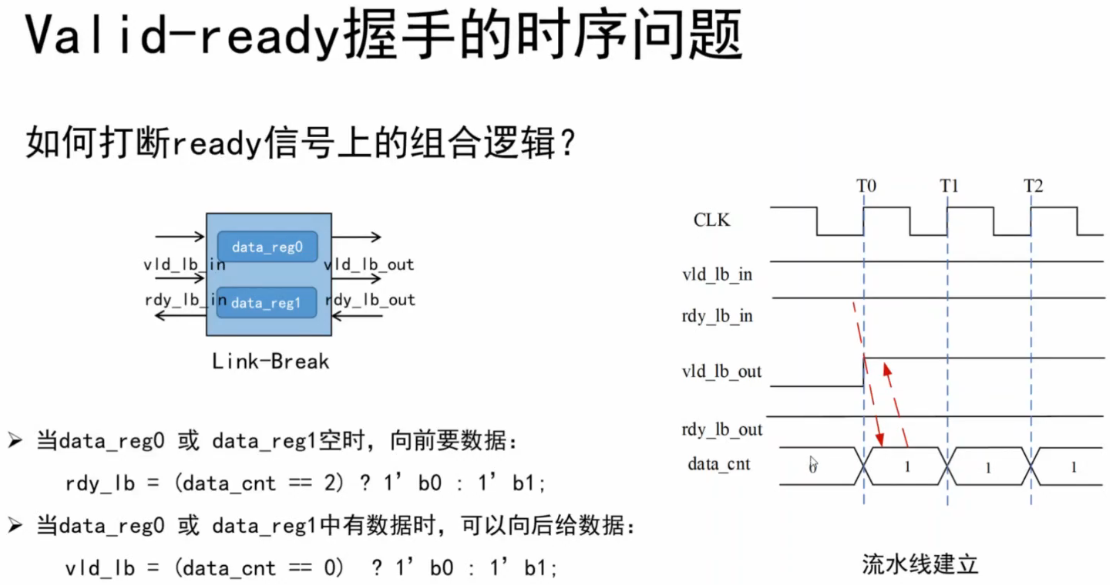

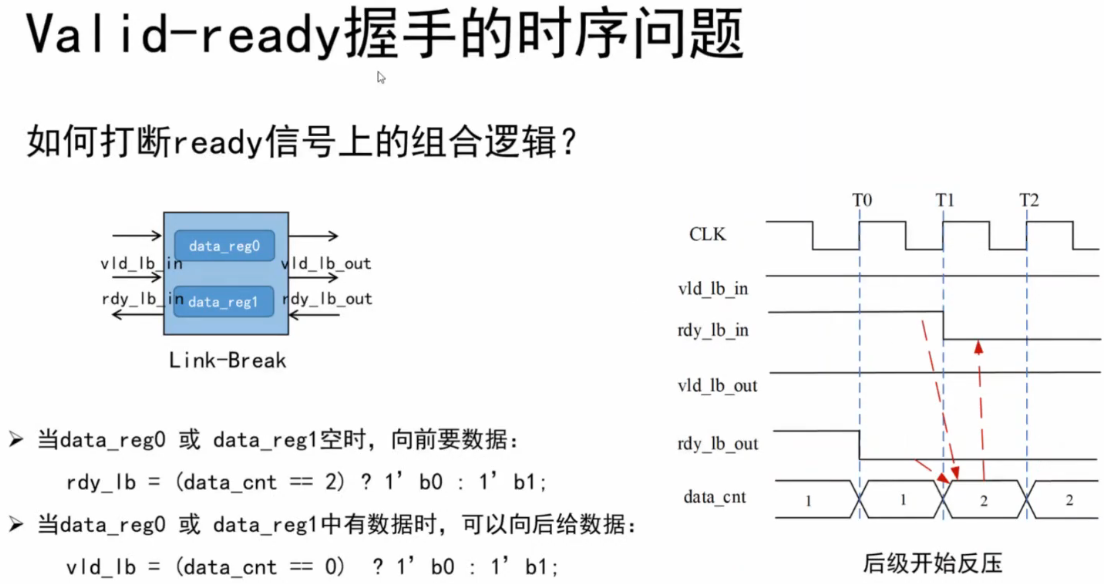

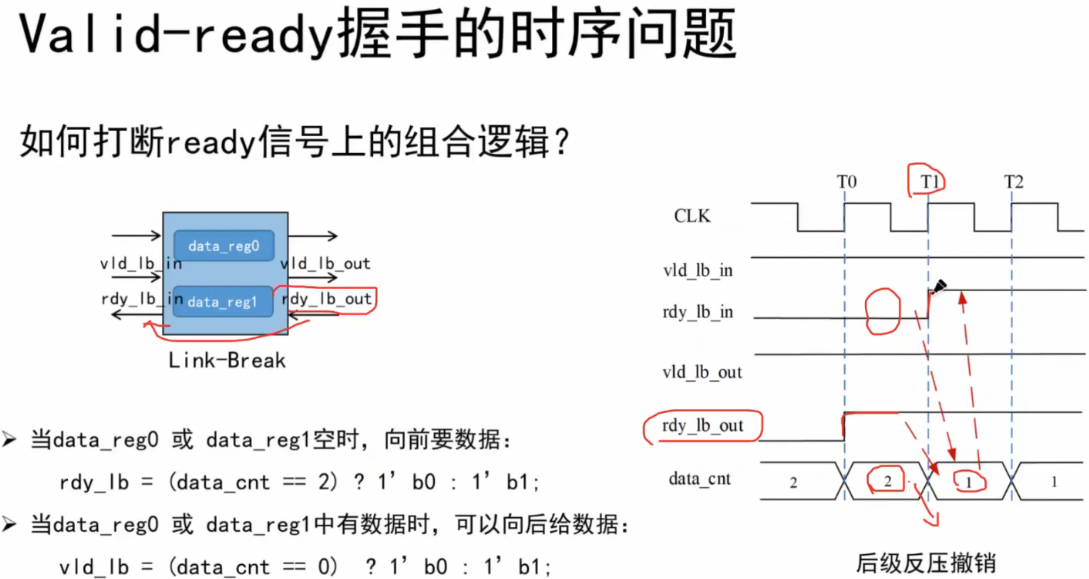

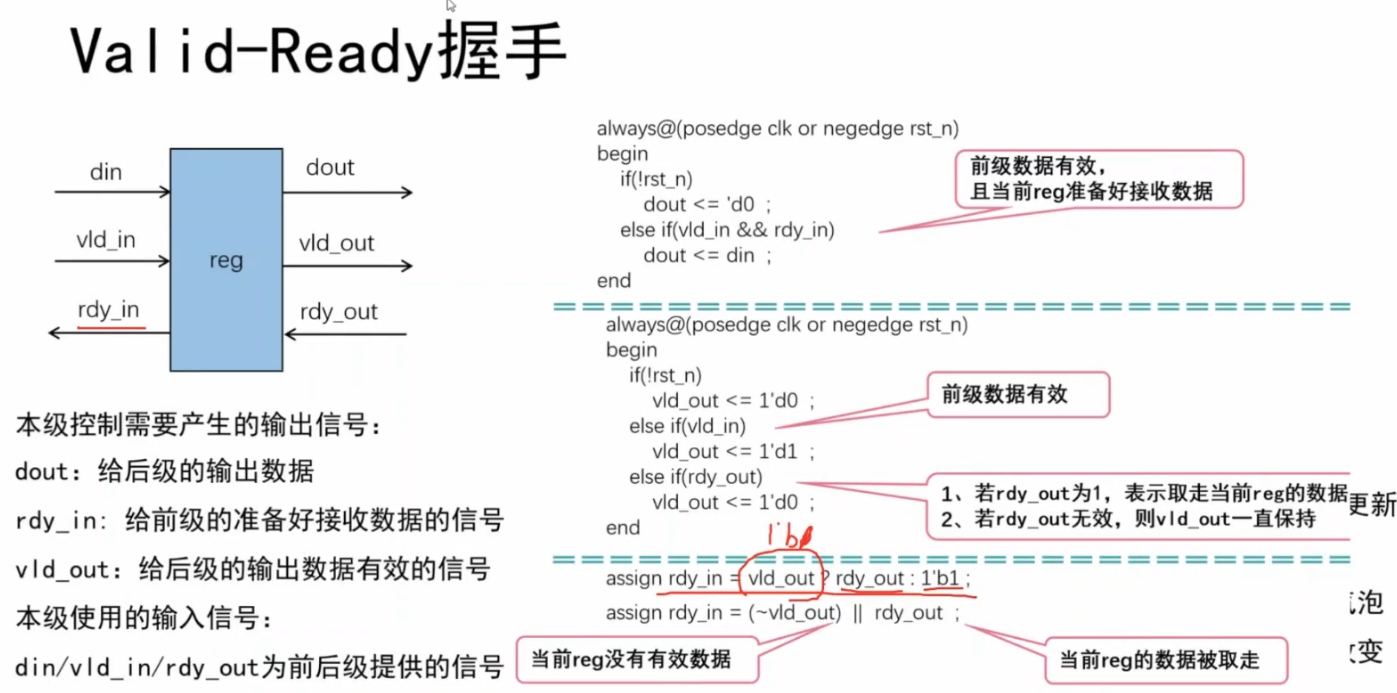

忽略各级电路之间的组合逻辑电路

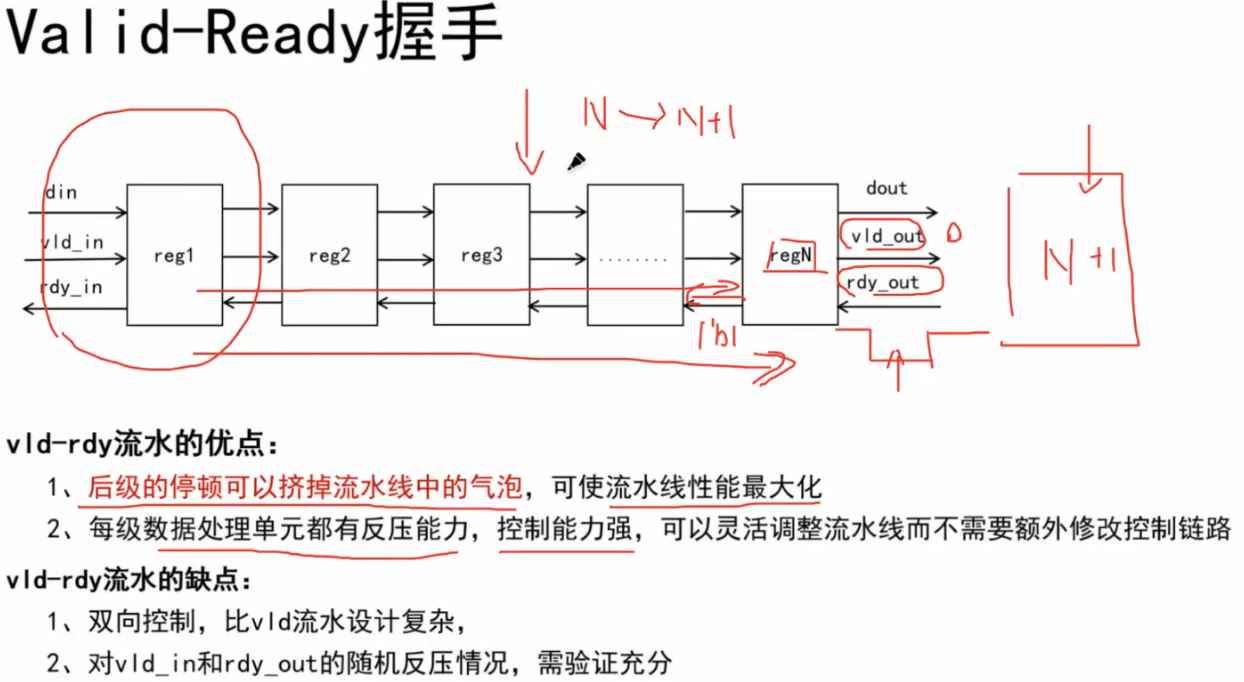

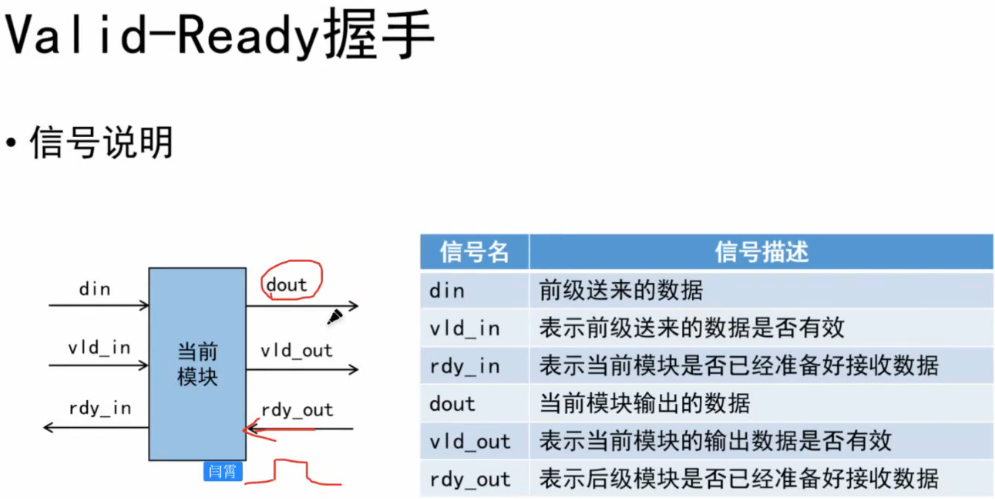

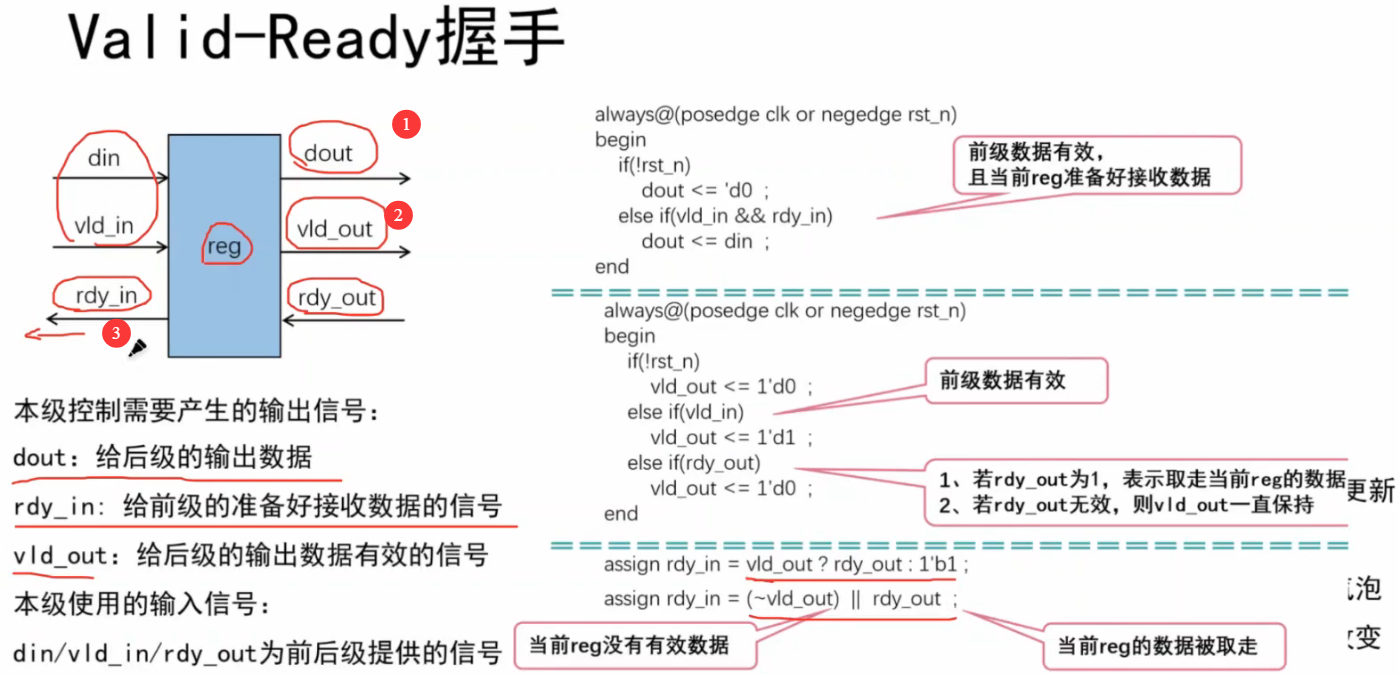

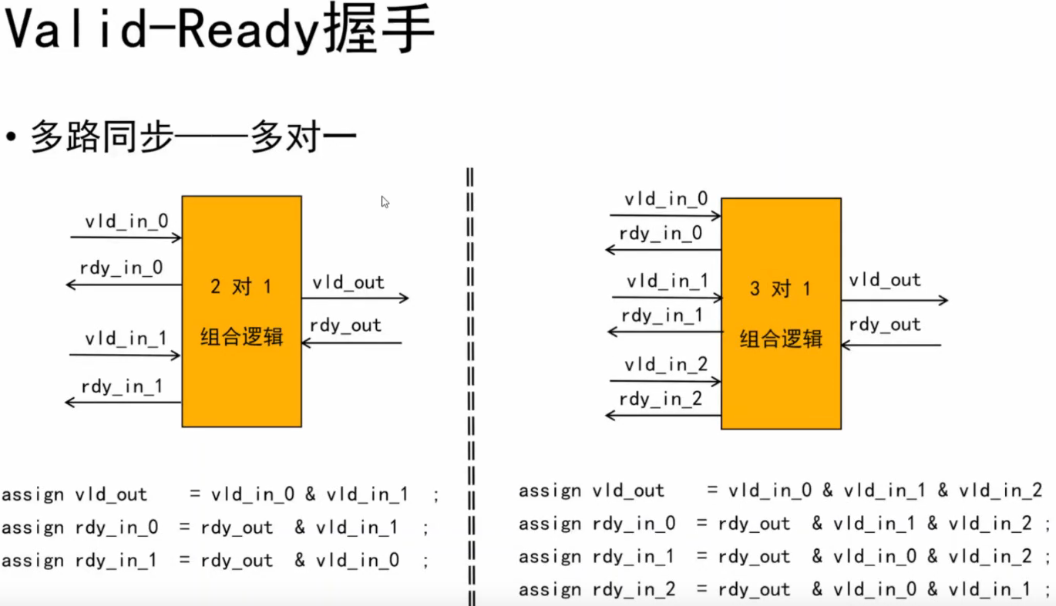

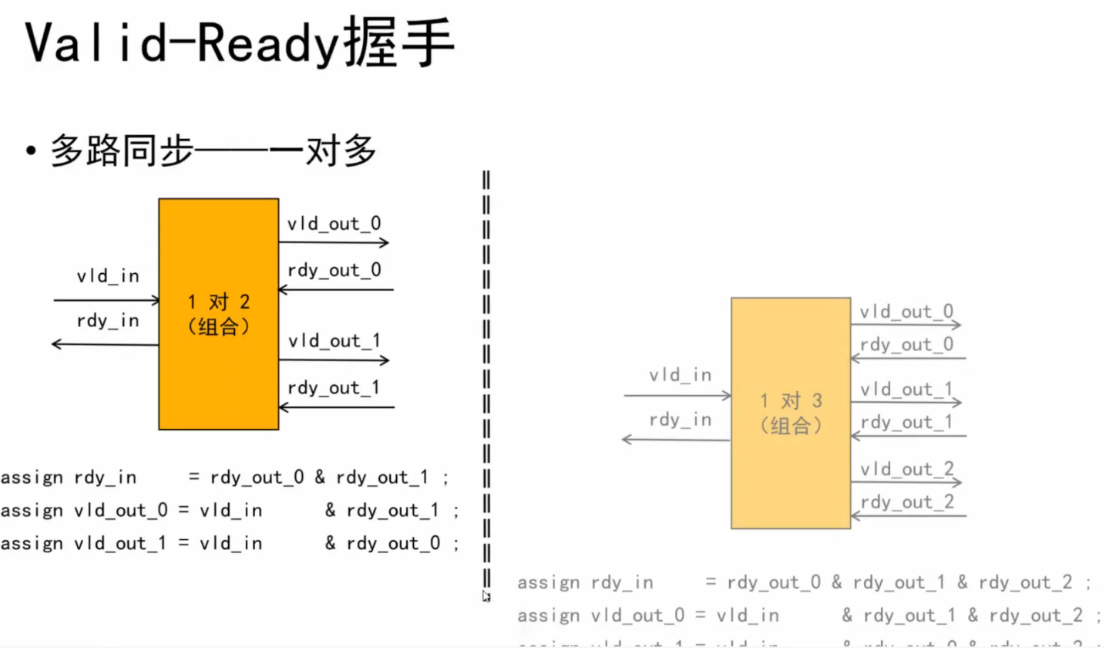

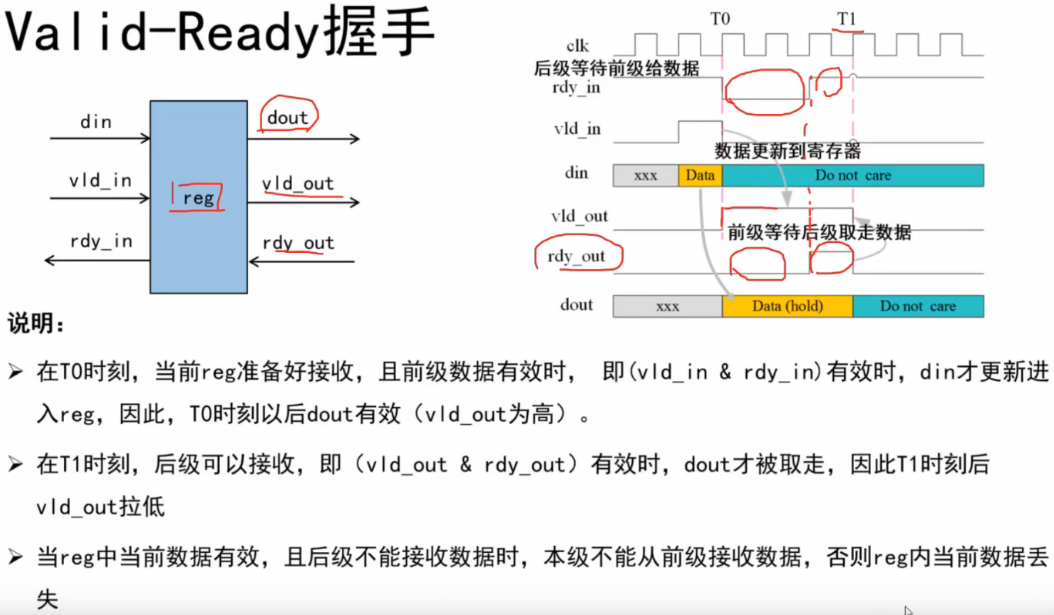

当 rdy_in == 1 时,代表当前模块准备完成,可以进行工作。

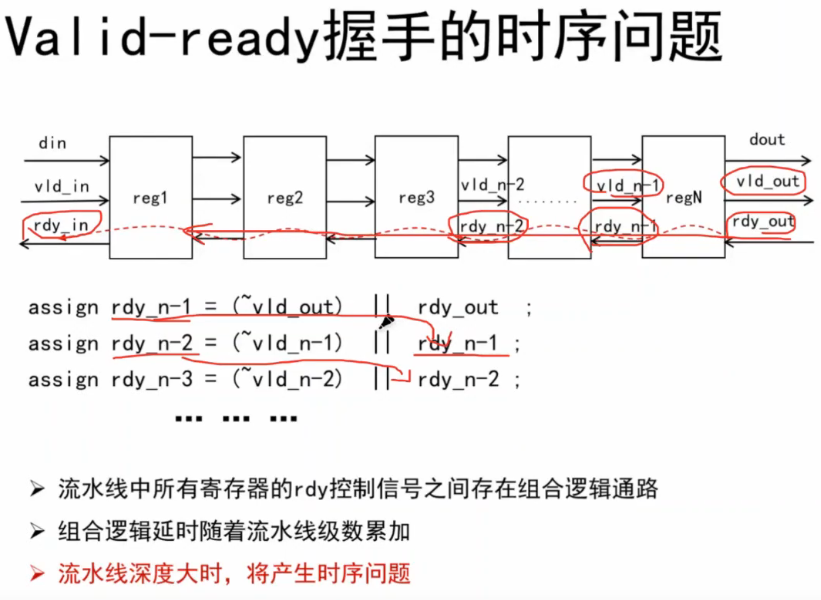

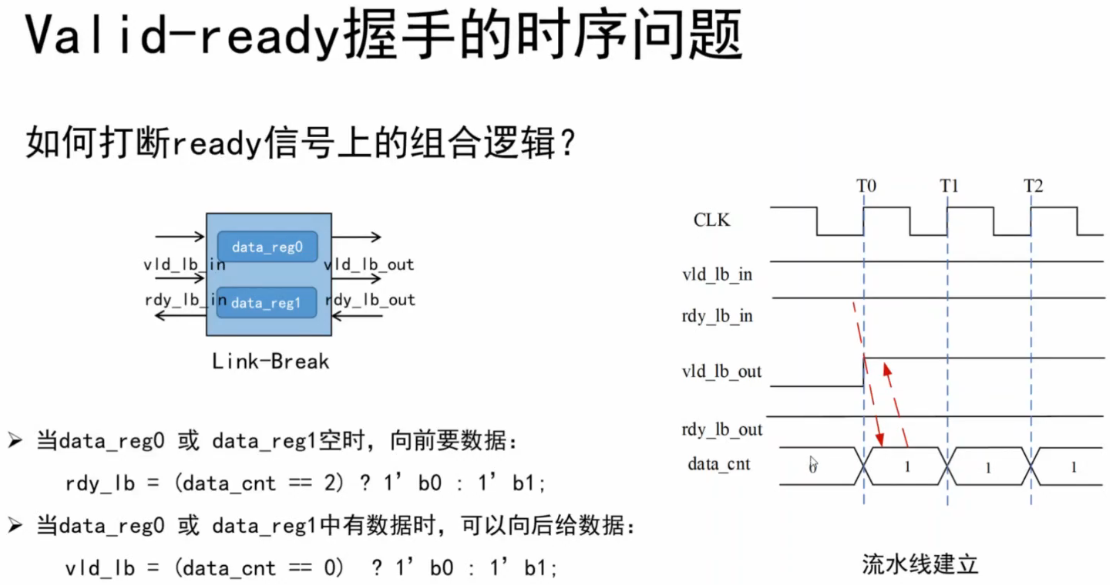

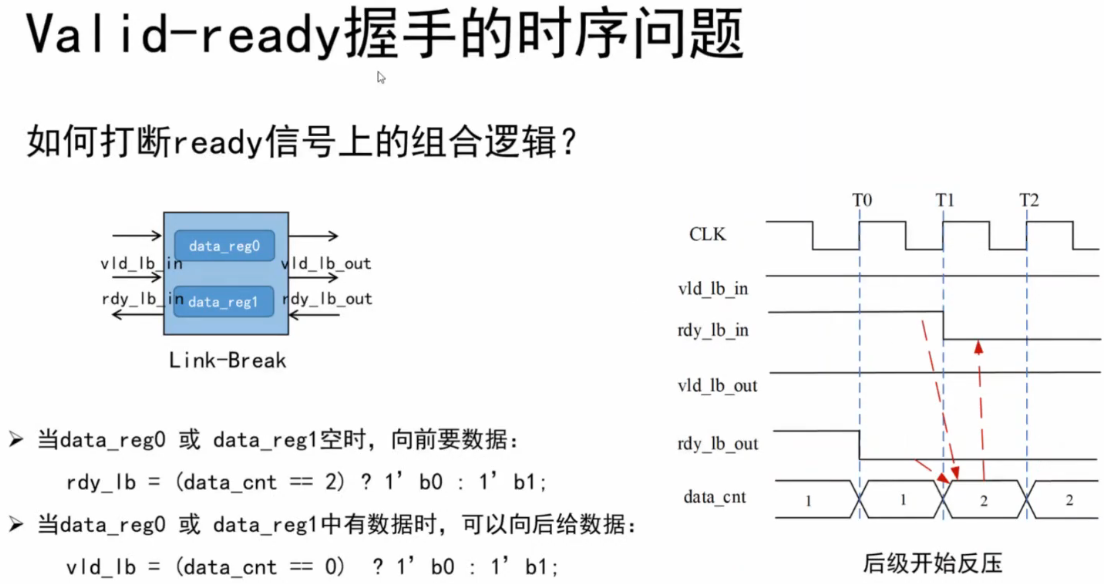

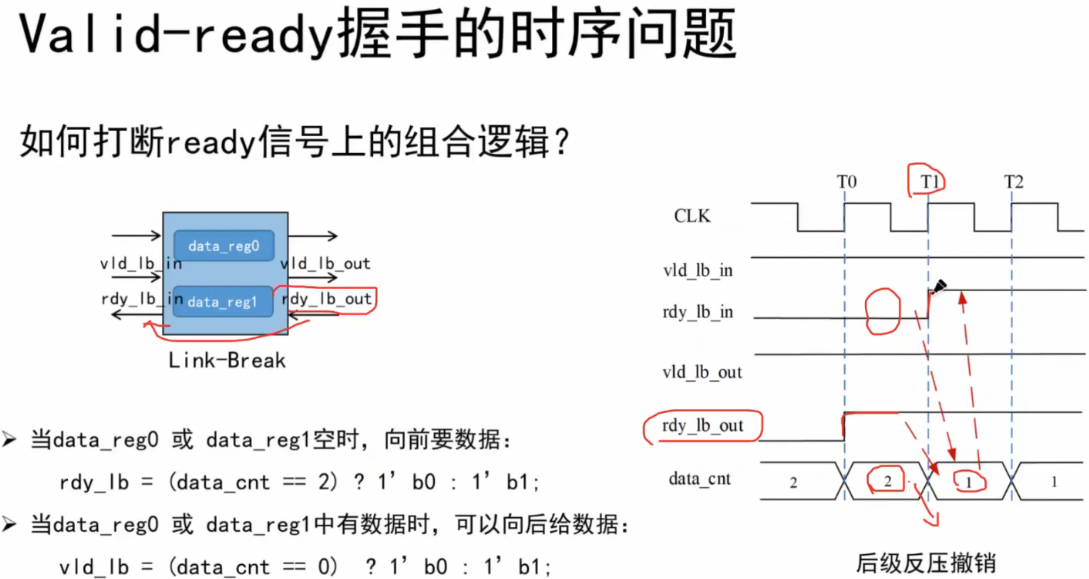

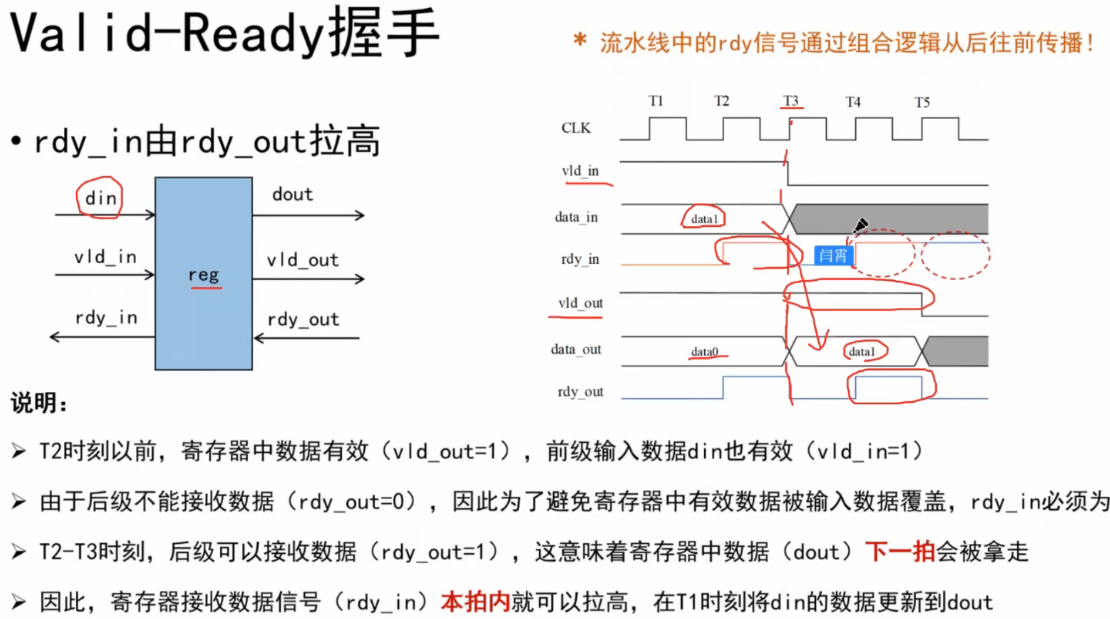

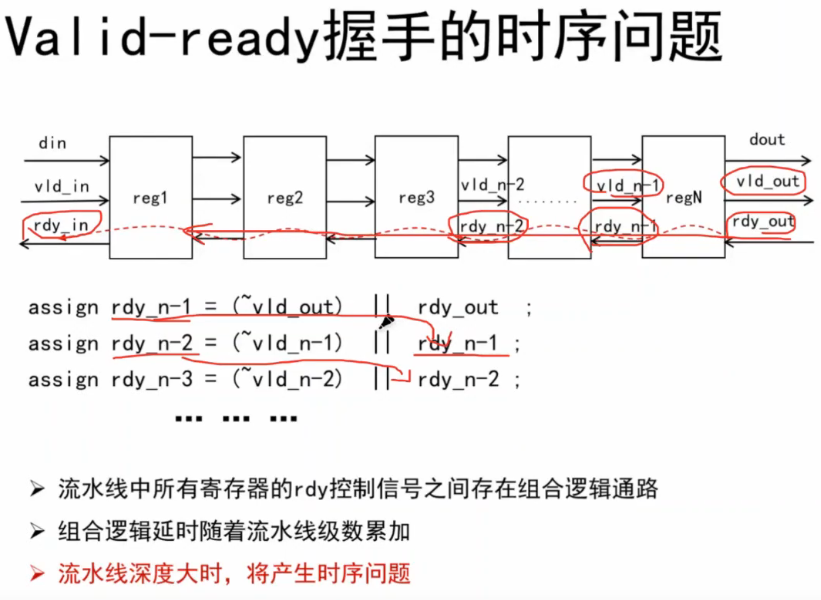

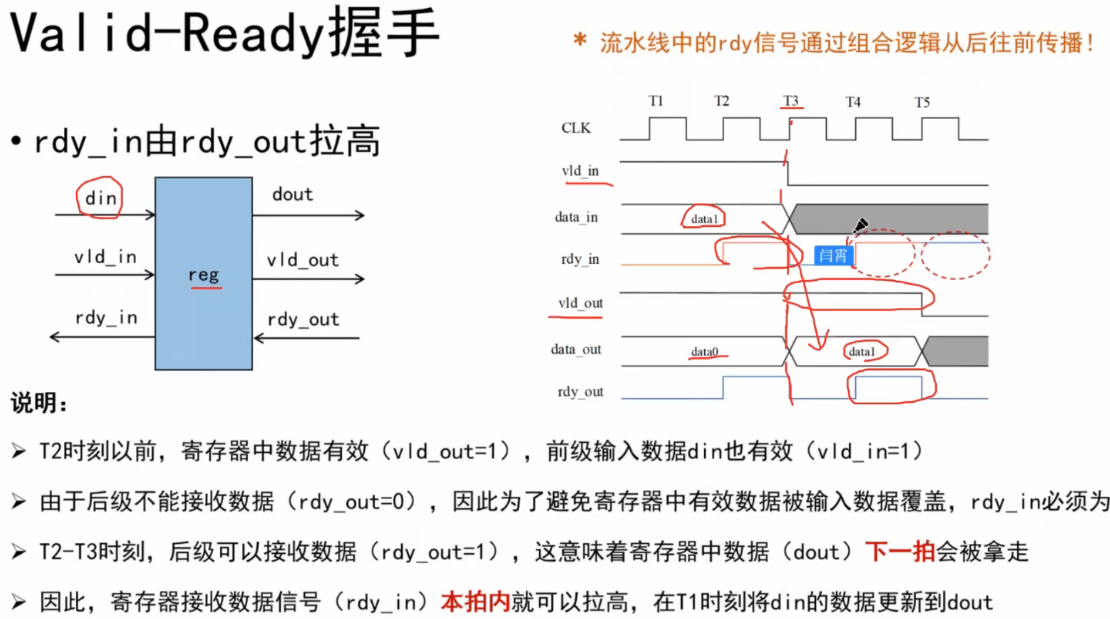

【注意】流水线中的rdy信号通过组合逻辑从后往前传播。

当rdy_out 信号被拉高之后,rdy_in信号也会被拉高操作。

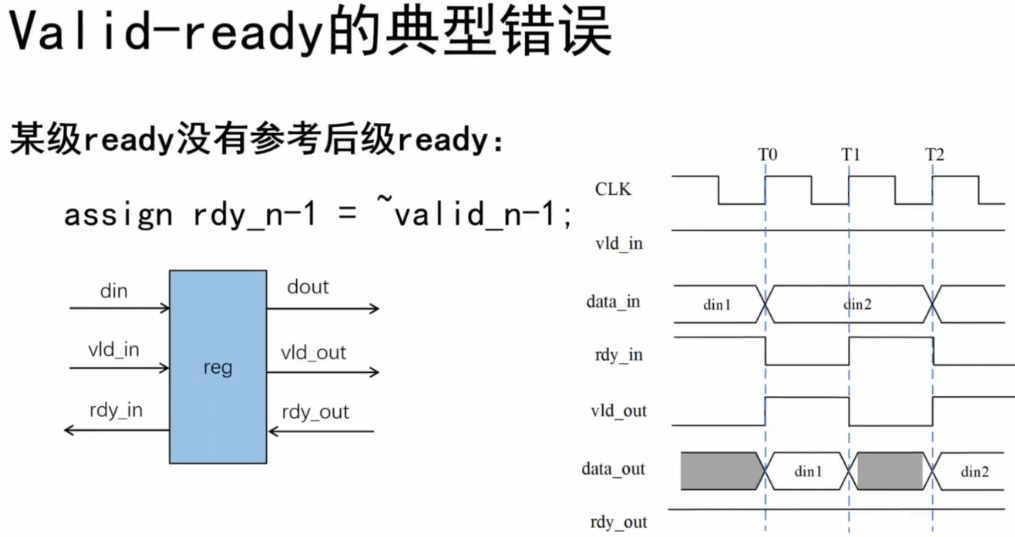

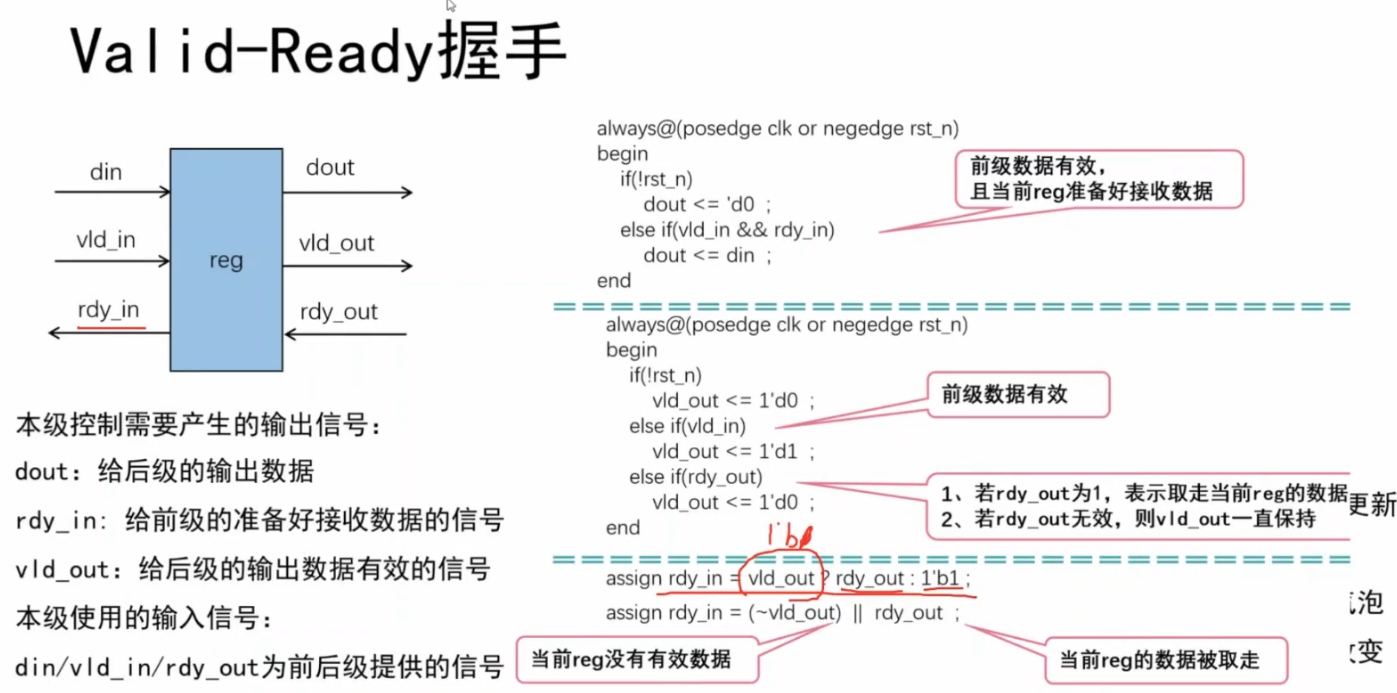

序号1,2,3是本级需要产生的输出信号线,是需要控制信号进行跳变输出。

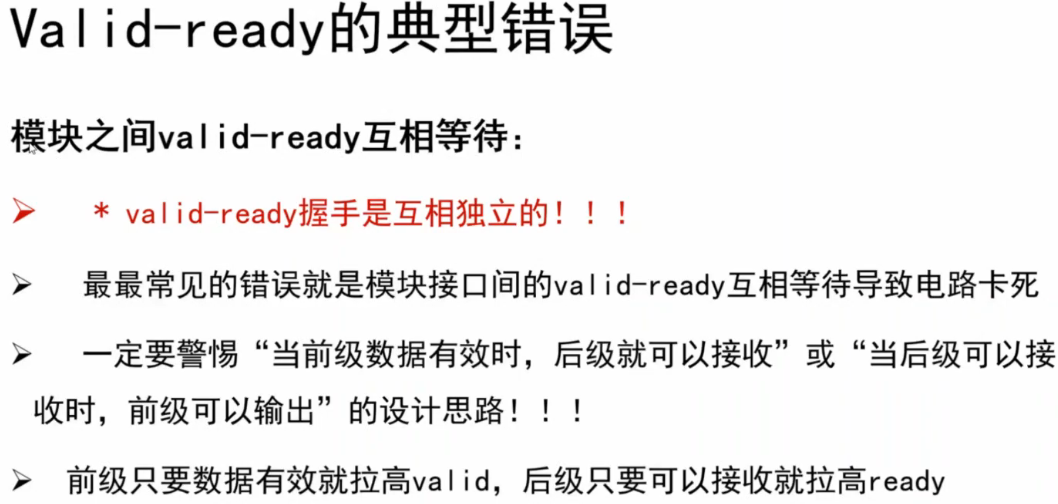

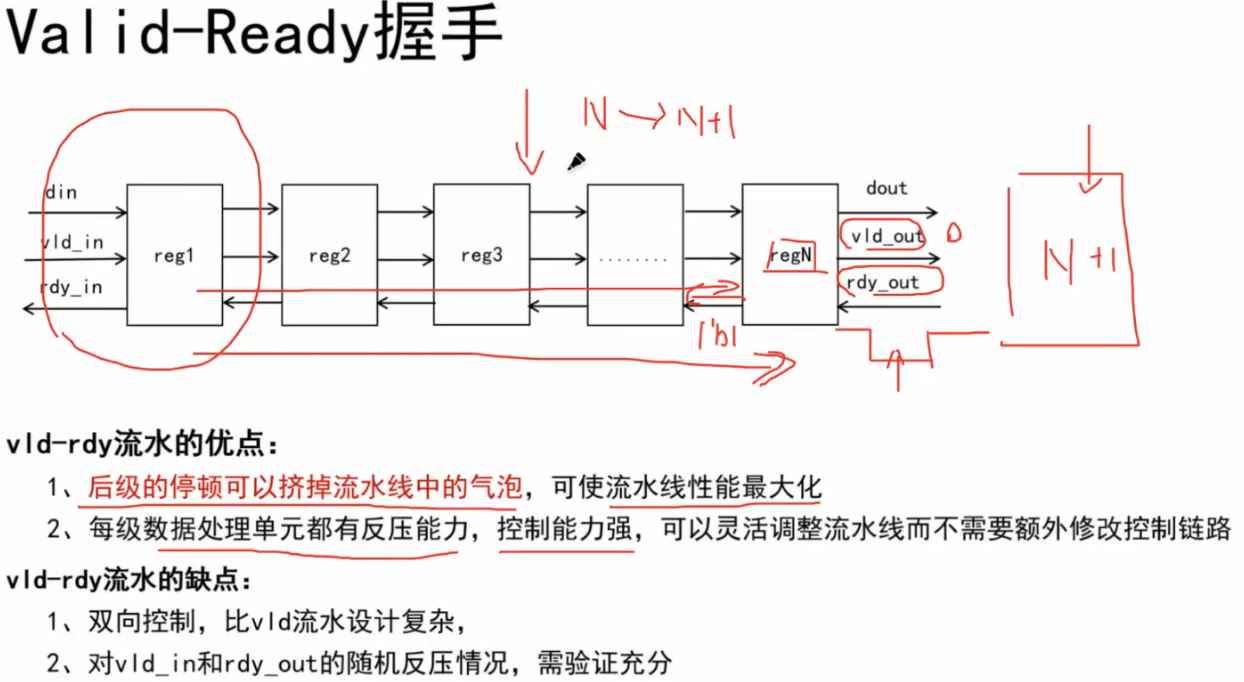

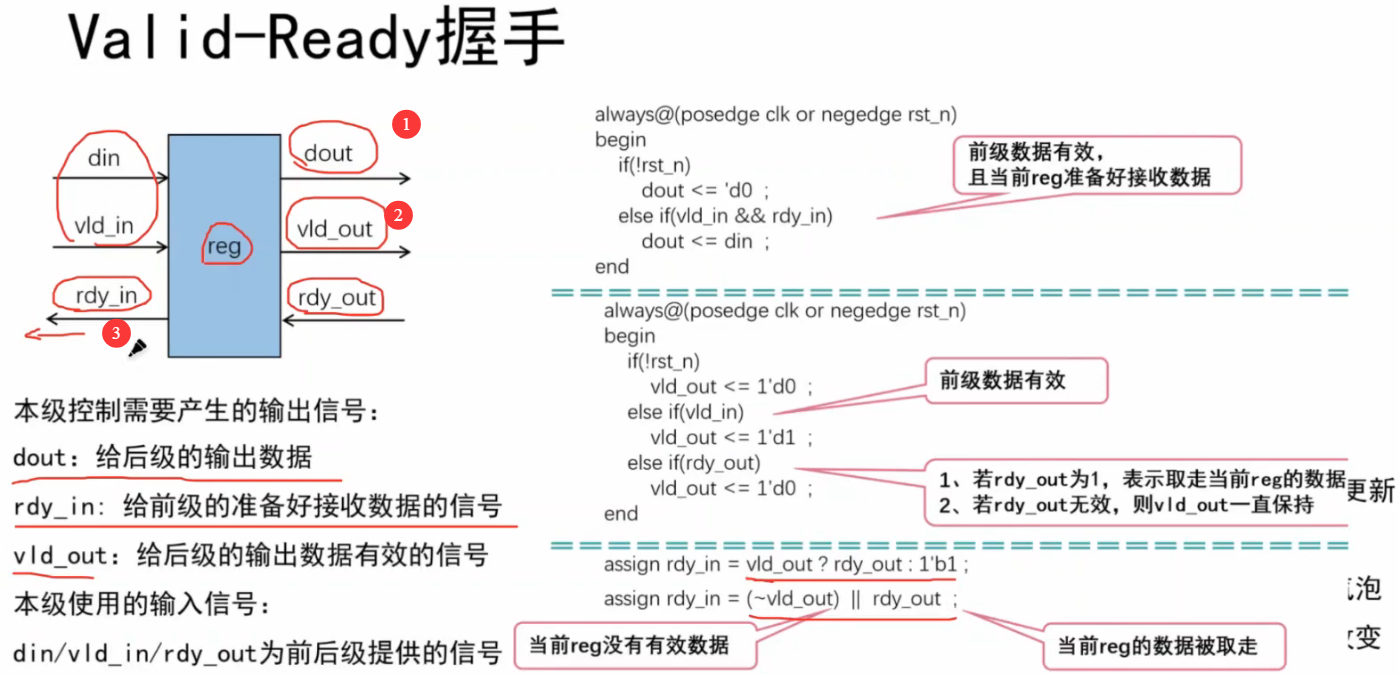

忽略各级电路之间的组合逻辑电路

当 rdy_in == 1 时,代表当前模块准备完成,可以进行工作。

【注意】流水线中的rdy信号通过组合逻辑从后往前传播。

当rdy_out 信号被拉高之后,rdy_in信号也会被拉高操作。

序号1,2,3是本级需要产生的输出信号线,是需要控制信号进行跳变输出。