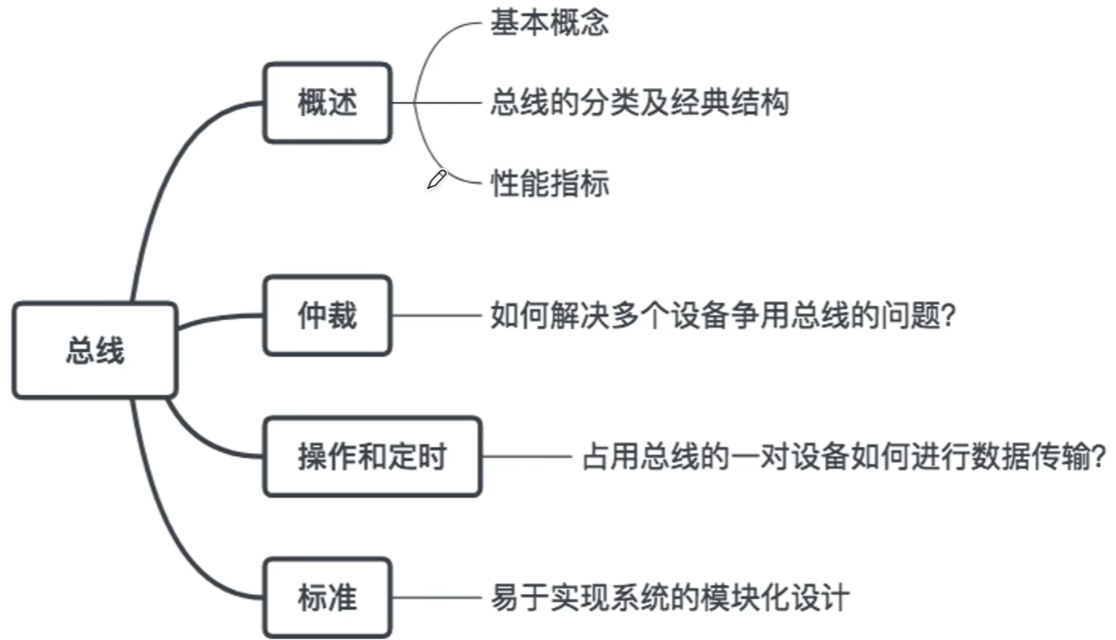

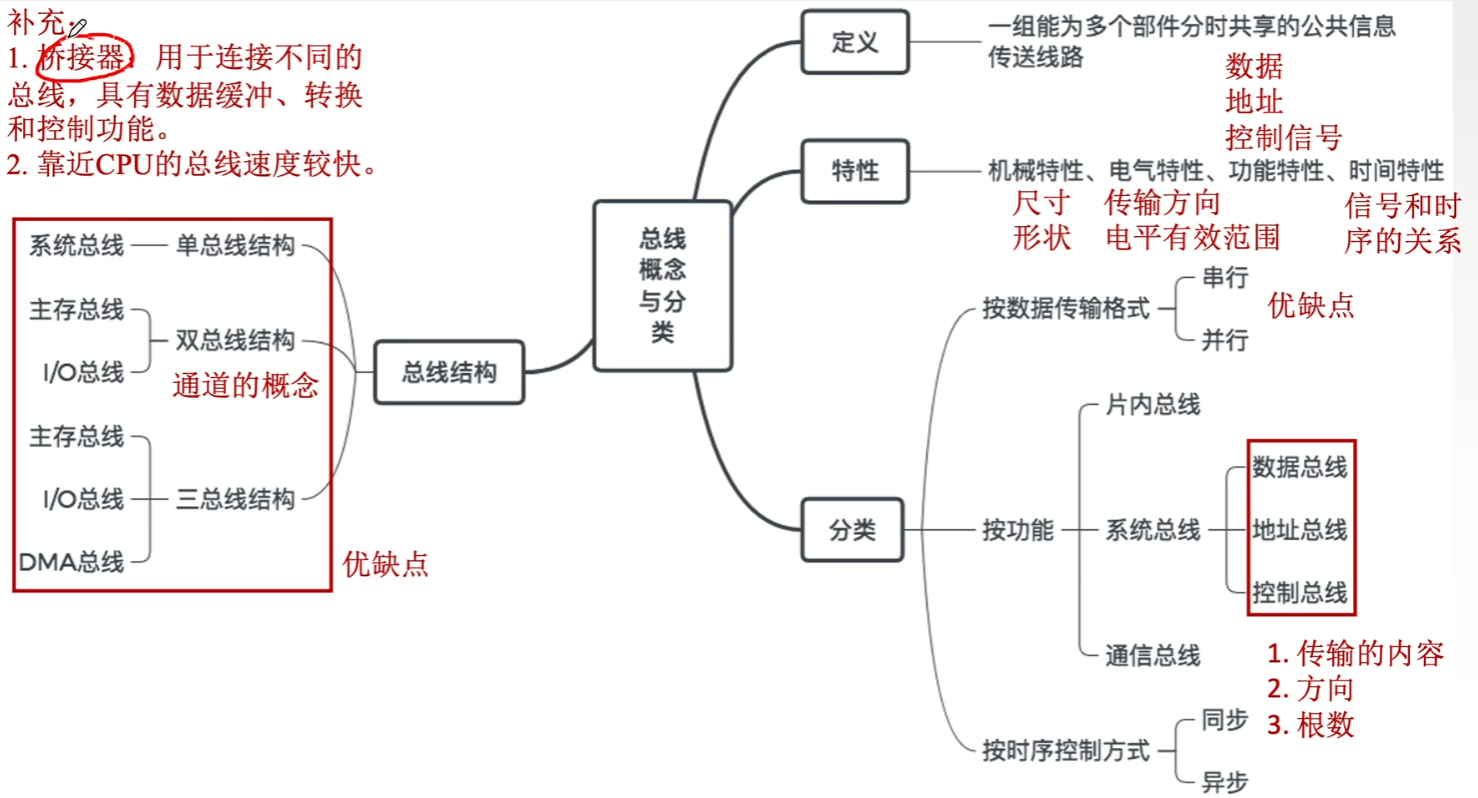

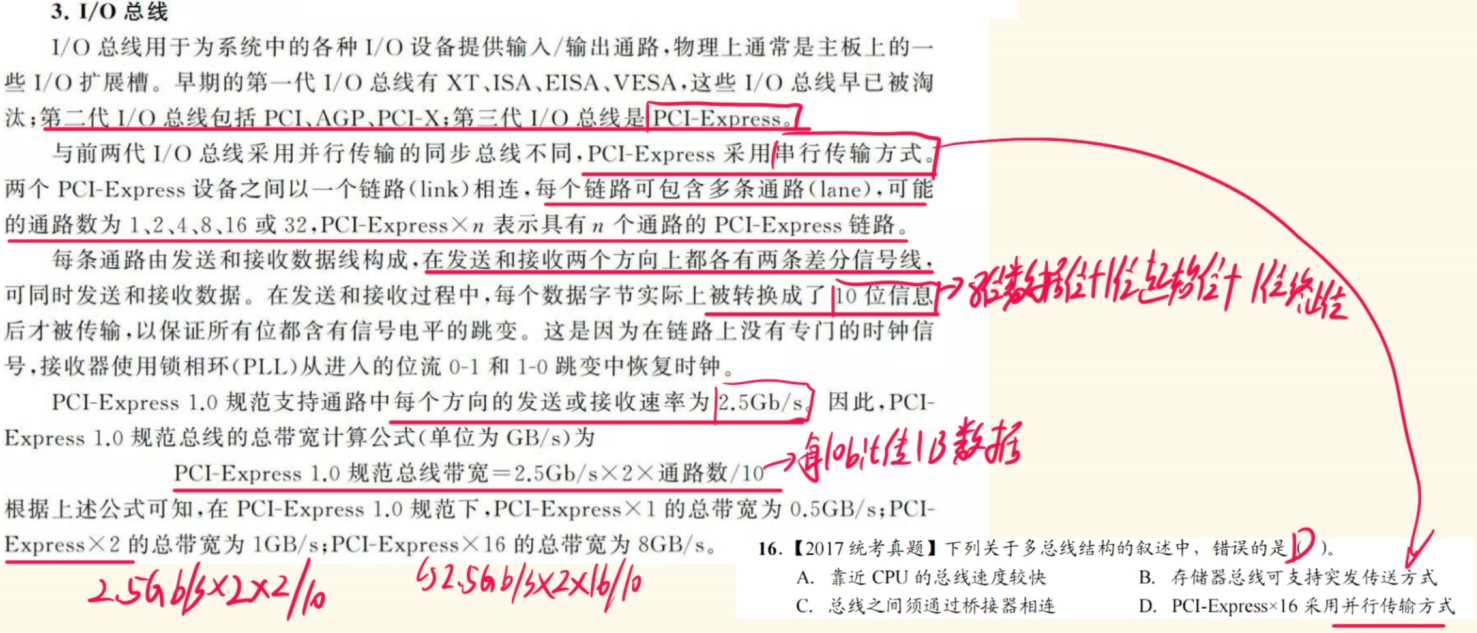

一、总线知识体系框架

二、总线相关基本概念

1、总线是啥

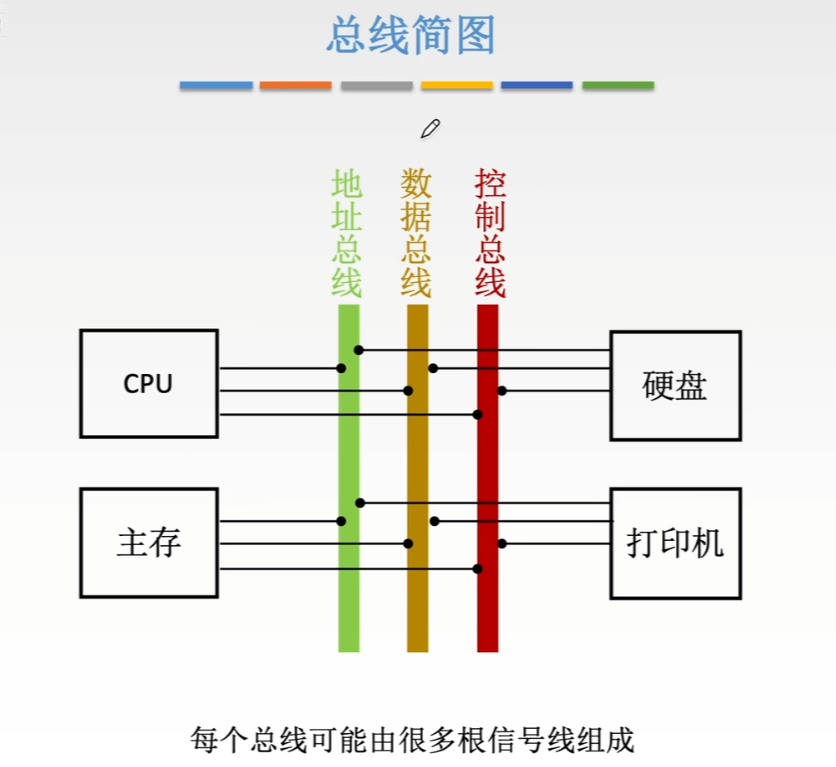

**简单理解:**顾名思义,多根线合成一根总线

(其中【一根系统总线】包含【3种信号线】)

【地址总线】:传输地址信息

【数据总线】:传输数据信息

【控制总线】:CU传输控制信息

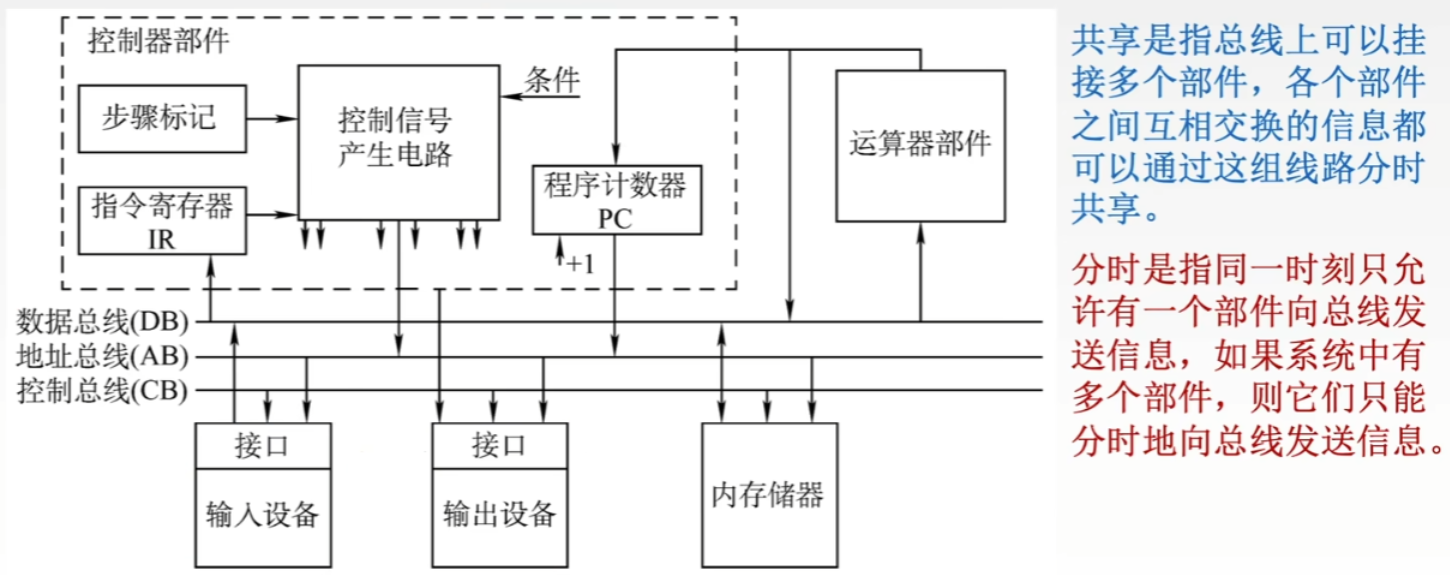

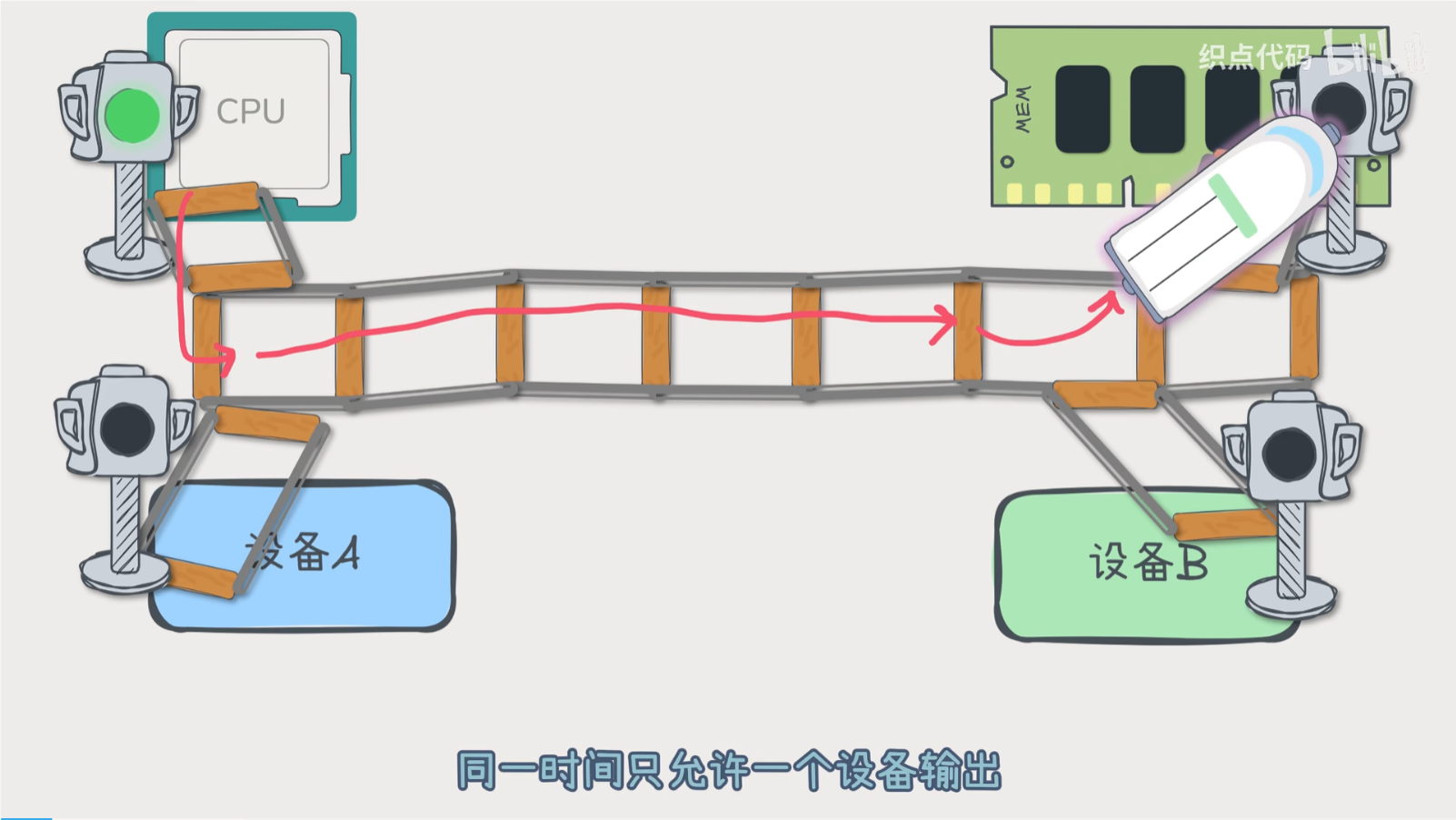

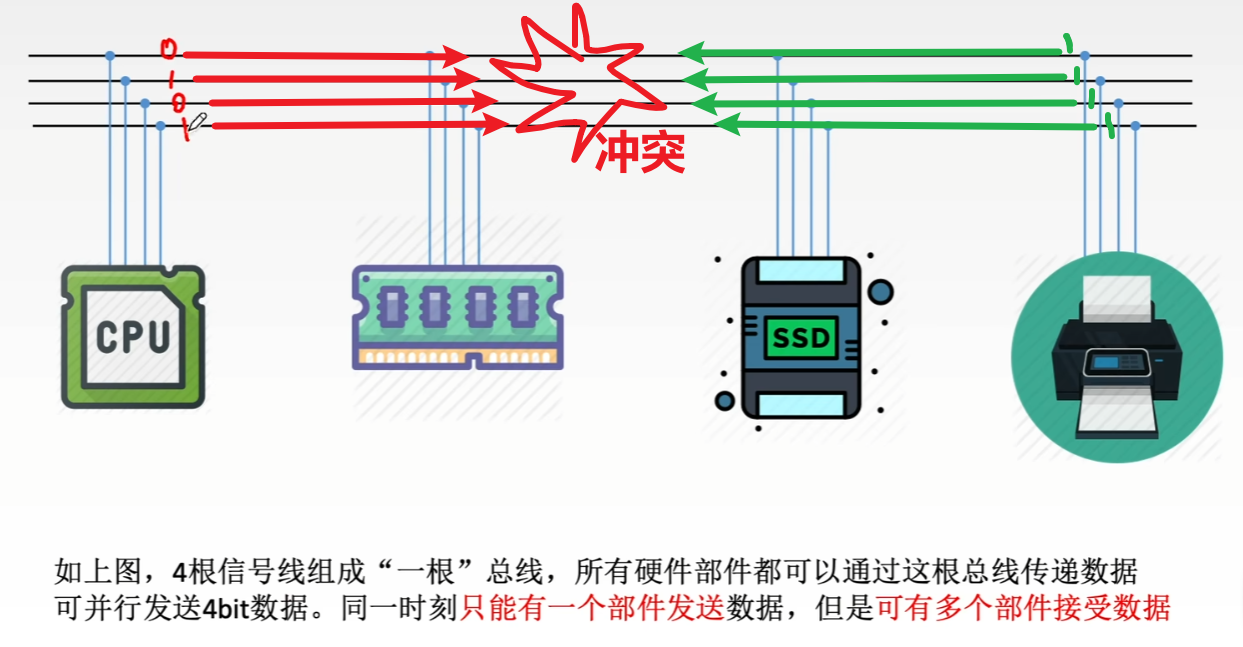

完整标准的概念:总线是一组为多个部件【分时】+【共享】的公共线路

- 怎么看【共享】?

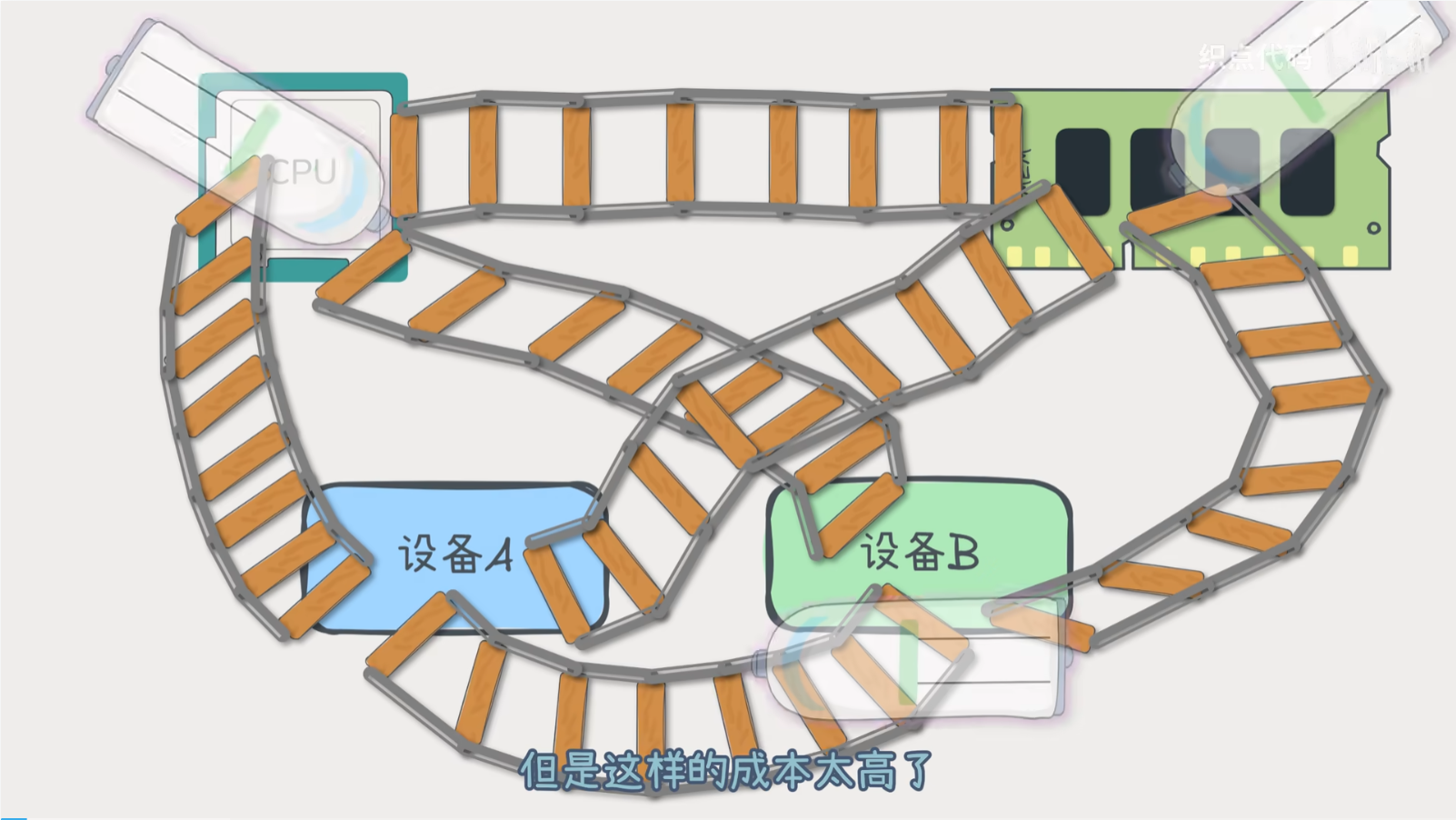

- 当多个部件如果分别单独用专门的线路连接,成本就太高了;

- 所以还是合成一整组线路成低 ,这就是【共享】!!

- 怎么看【分时】?

- 同一时刻(1个时钟周期)只允许一个部件使用总线发数据,如果多个部件同时发,就会冲突!(就像计算机网络的总线结构局域网容易冲突一样)

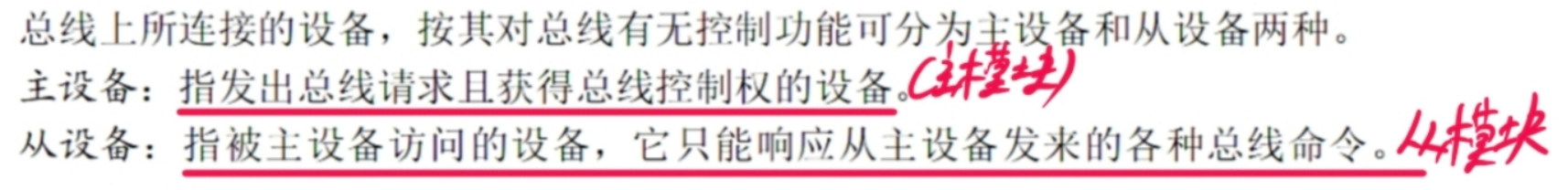

2、总线设备(理解)

也就是【发送方(主设备)】和【接收方(从设备)】

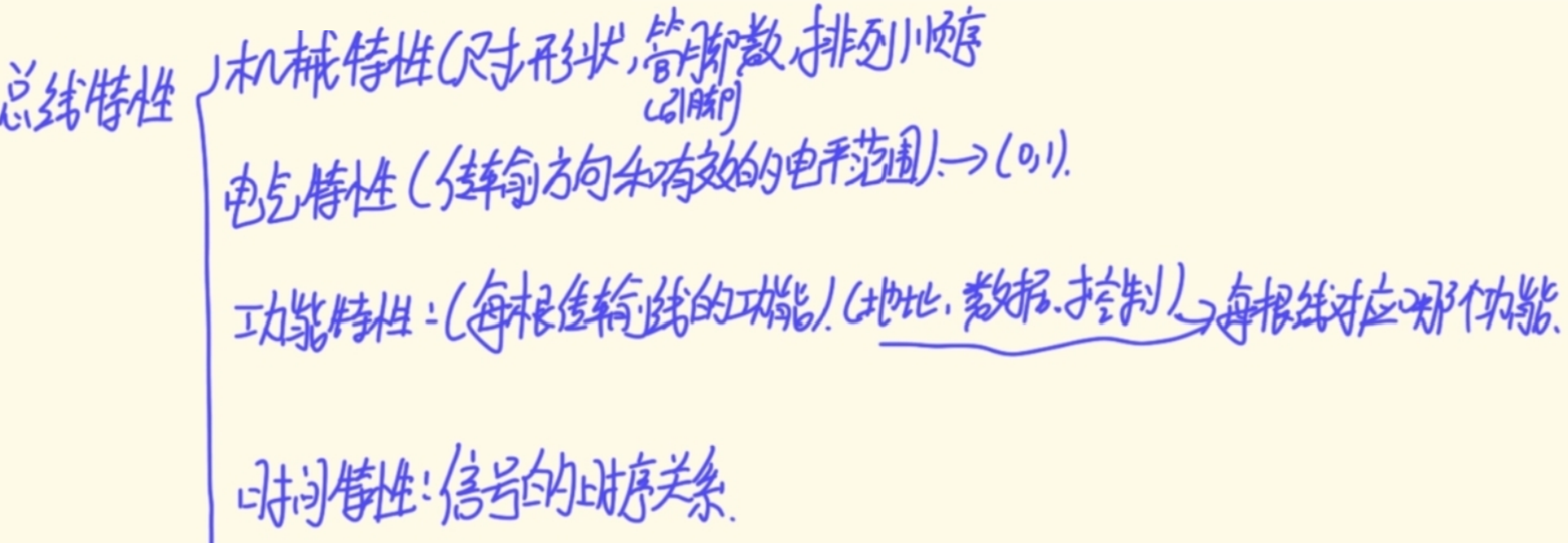

3、总线特性(理解)

**计算机网络的【物理层功能特性】**也提到过,很像,如果学过计网的应该看这里比较透彻,这里我懒得解释了

(注意这里有一个易错点:【功能特性 】强调的是对 "单根线" 的功能解释;【电器特性】 也会描述线的电平功能含义,但是注意强调的是 "多根线")

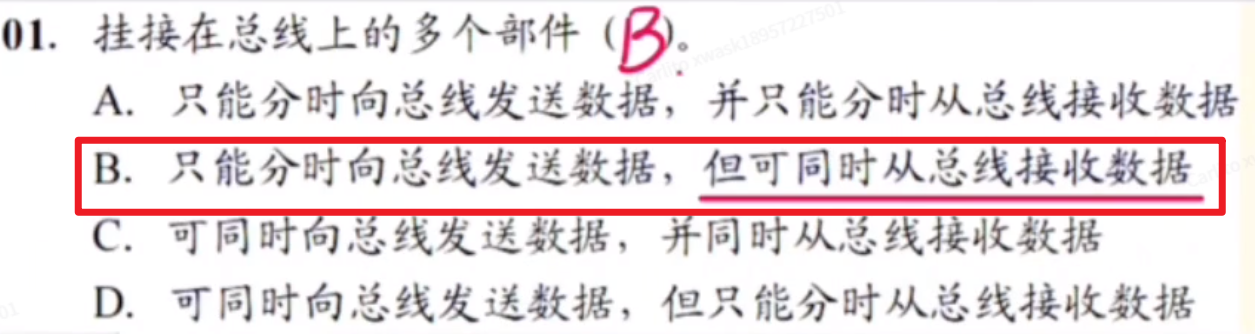

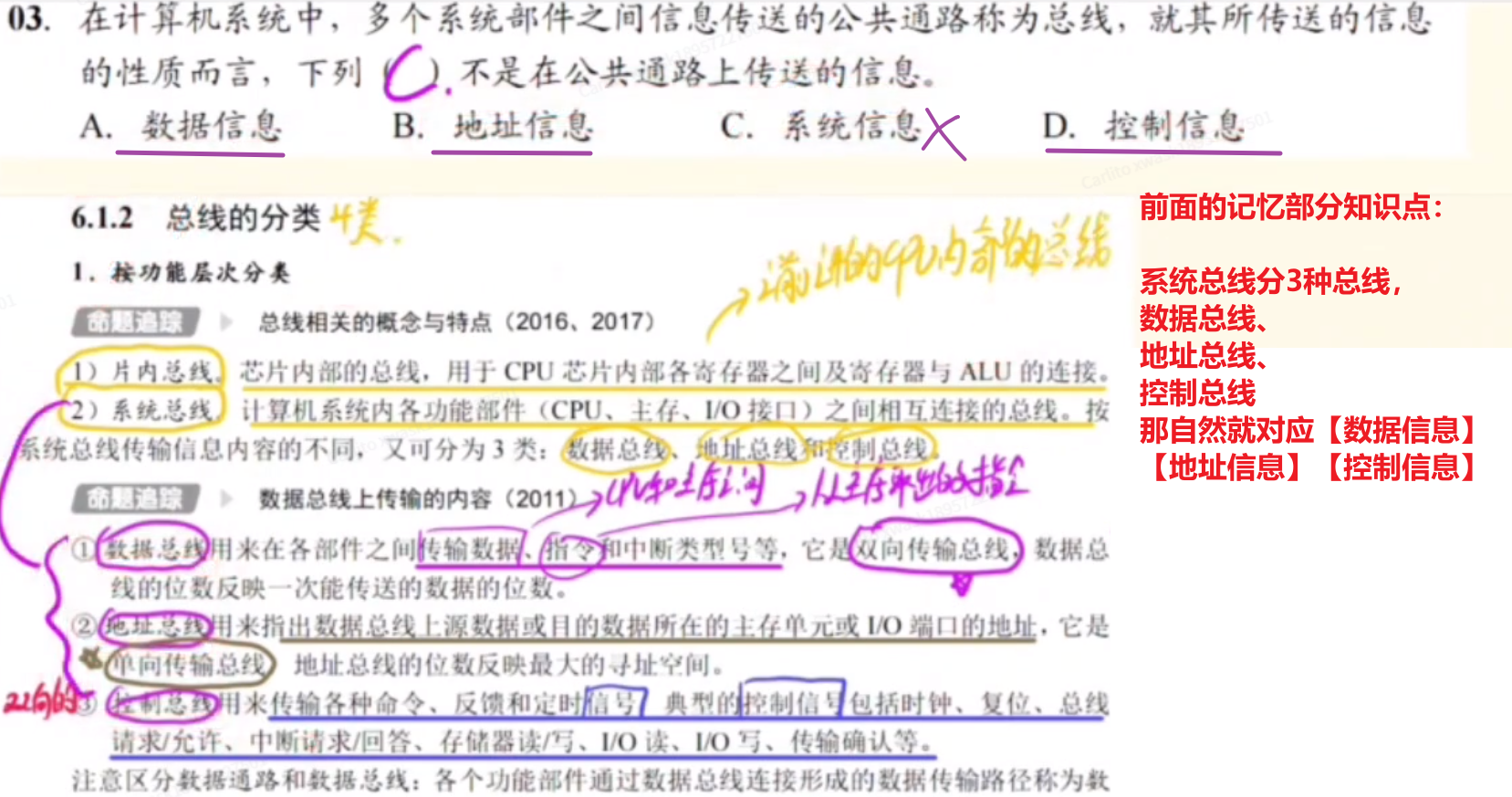

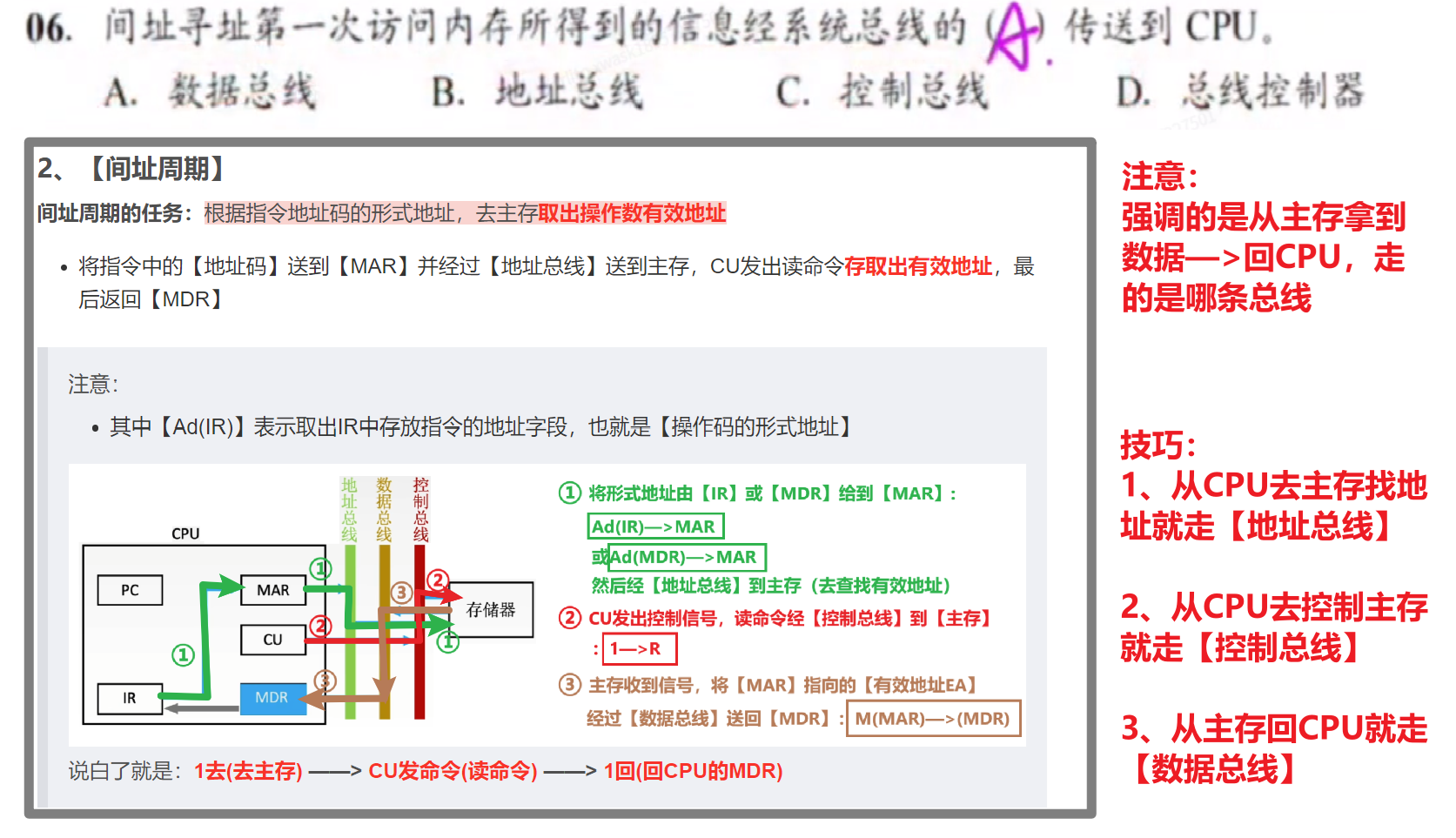

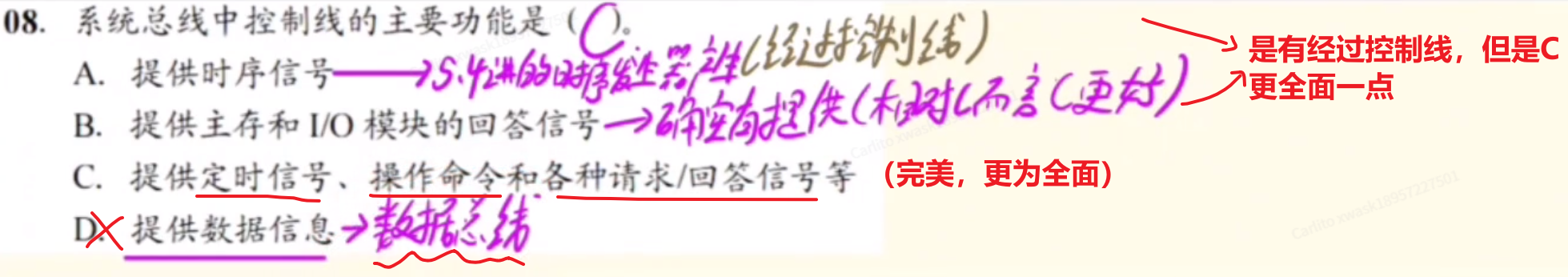

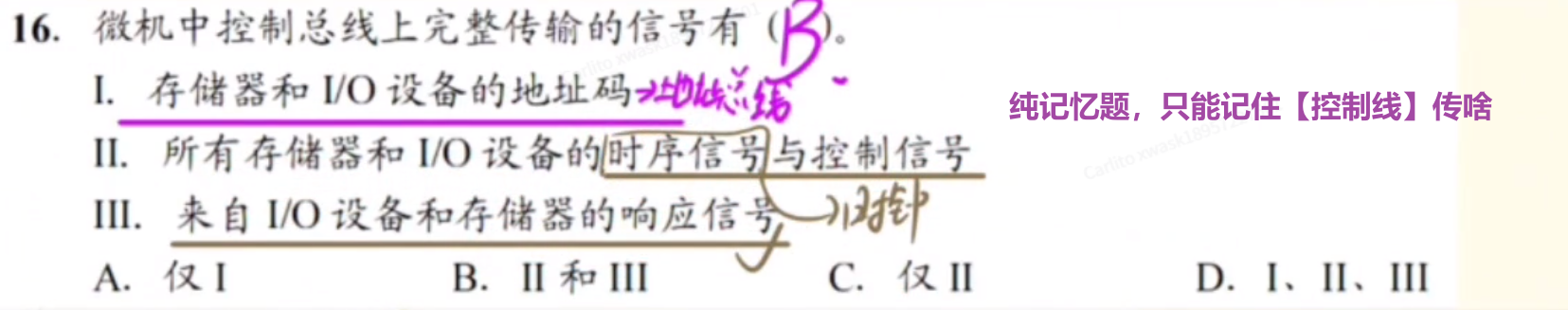

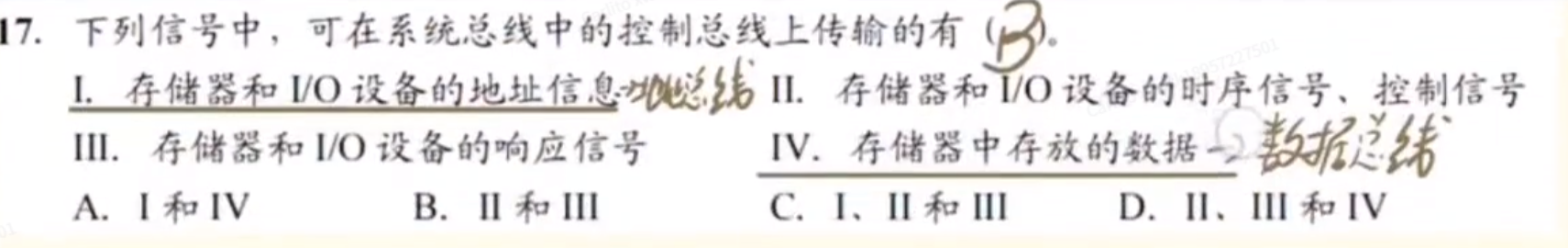

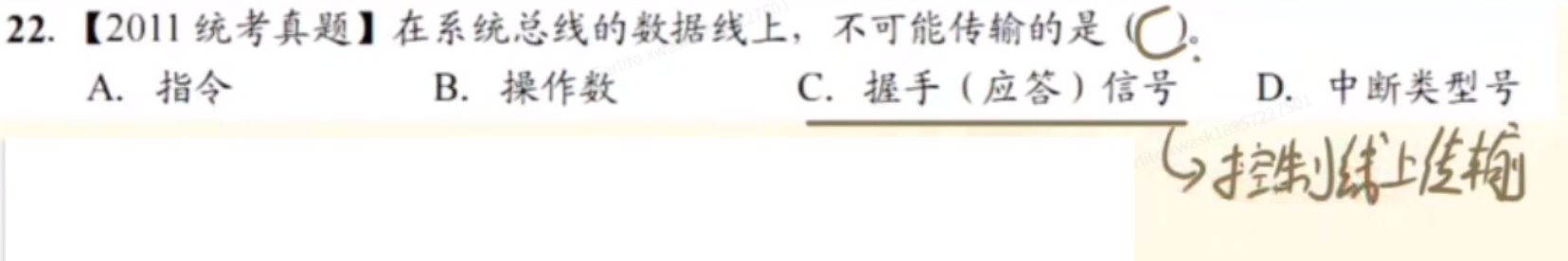

4、例题

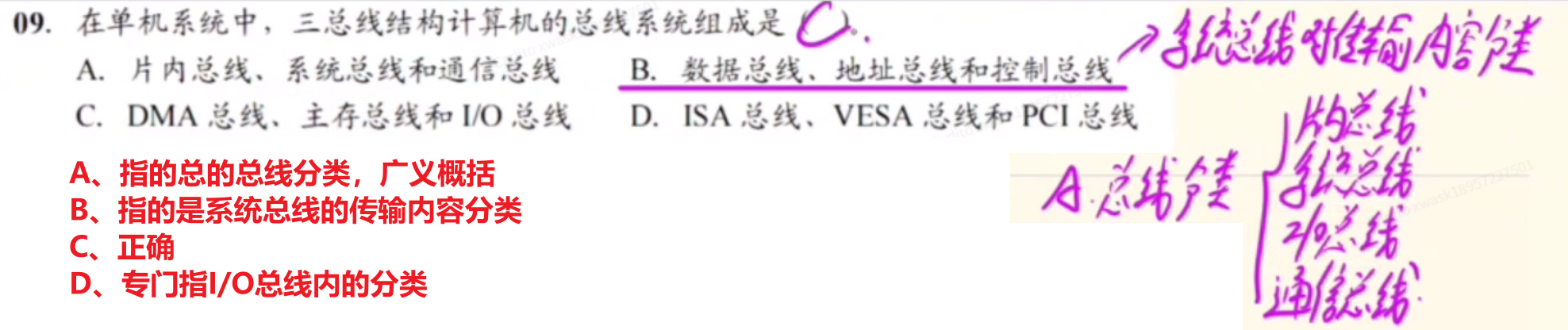

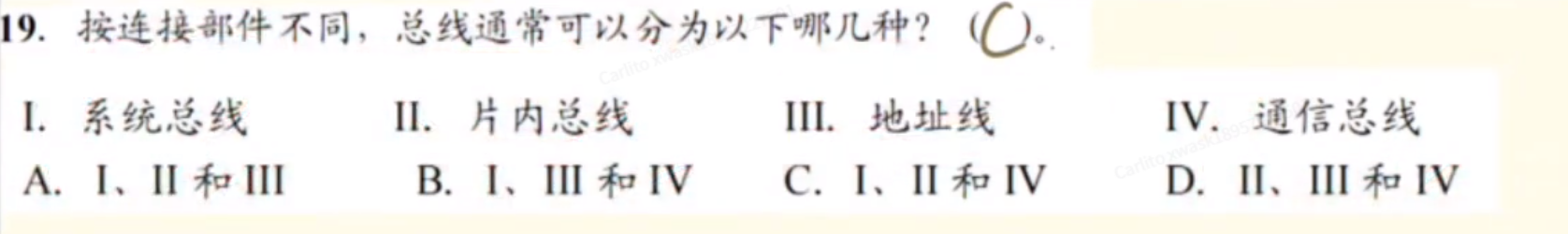

三、总线的分类

1)按总线功能分类

总体上按【连接部件】分类,一共就四种:

1、【片内总线】:

- 前面CPU那一章说过,就是【CPU芯片内部】的总线

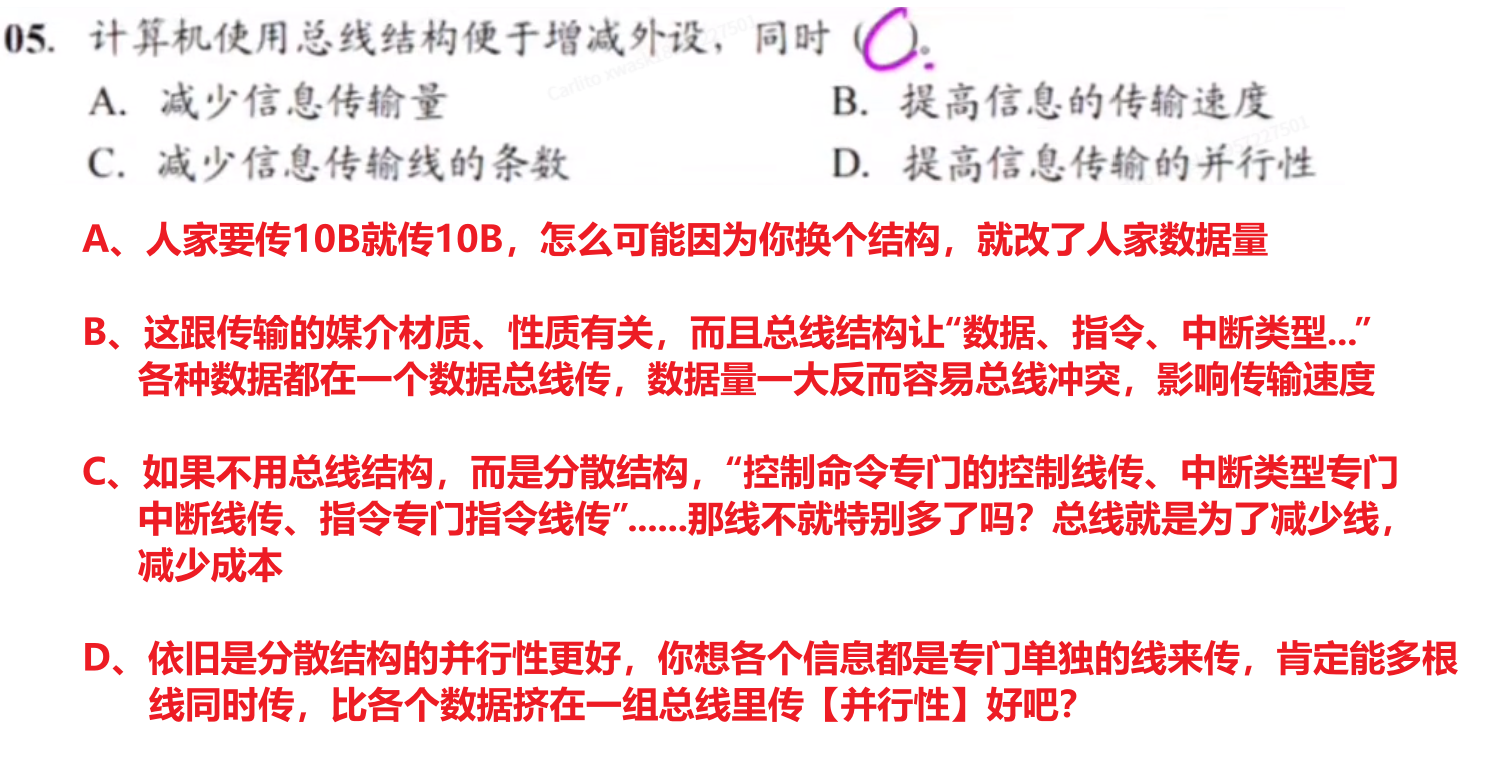

2、【系统总线】:

- 前面CPU那一章也说过,就是计算机【内部】和【外部】之间连接的总线(比如:CPU、主存、I/O之间的总线)

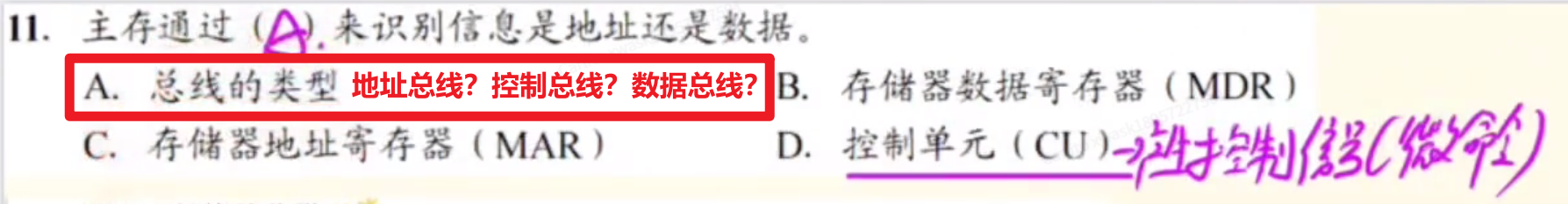

- 按照传输内容的不同,【系统总线】又可以分为3类

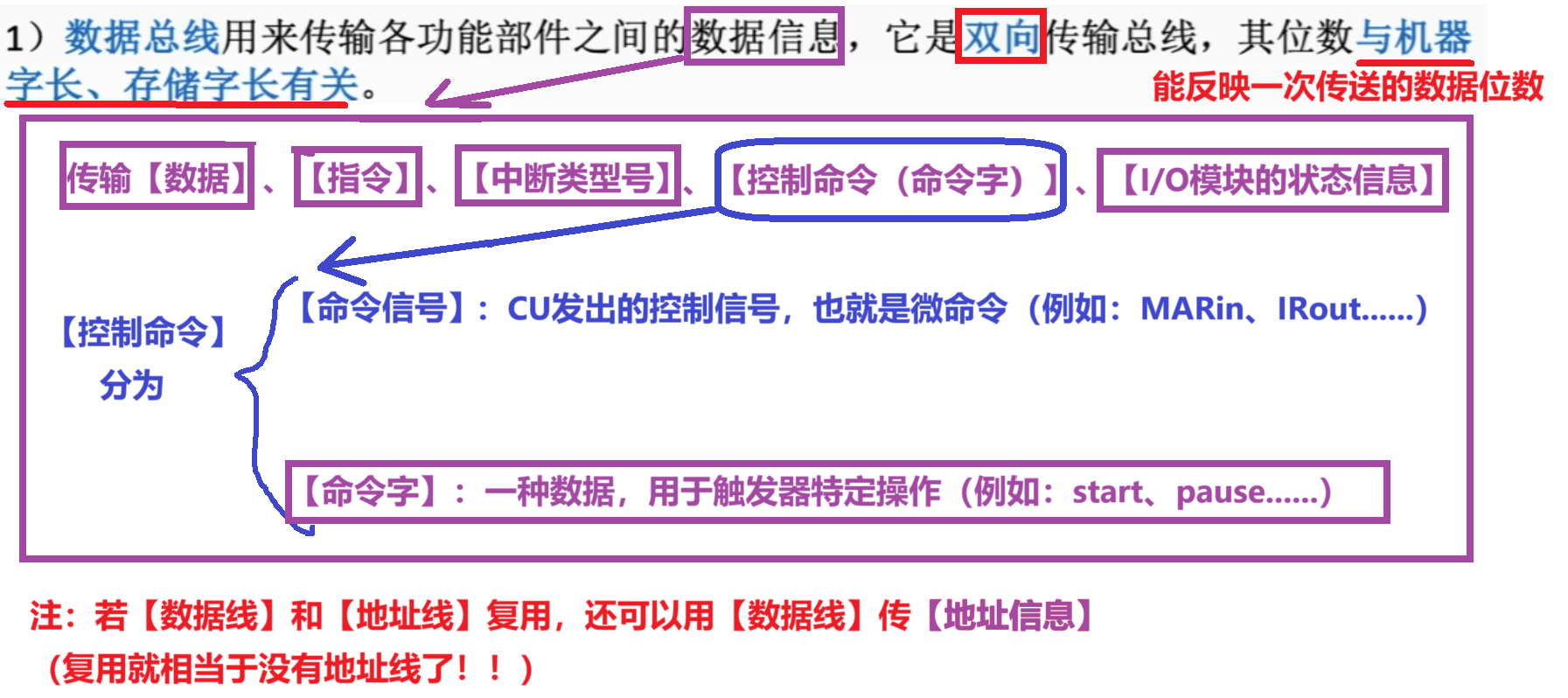

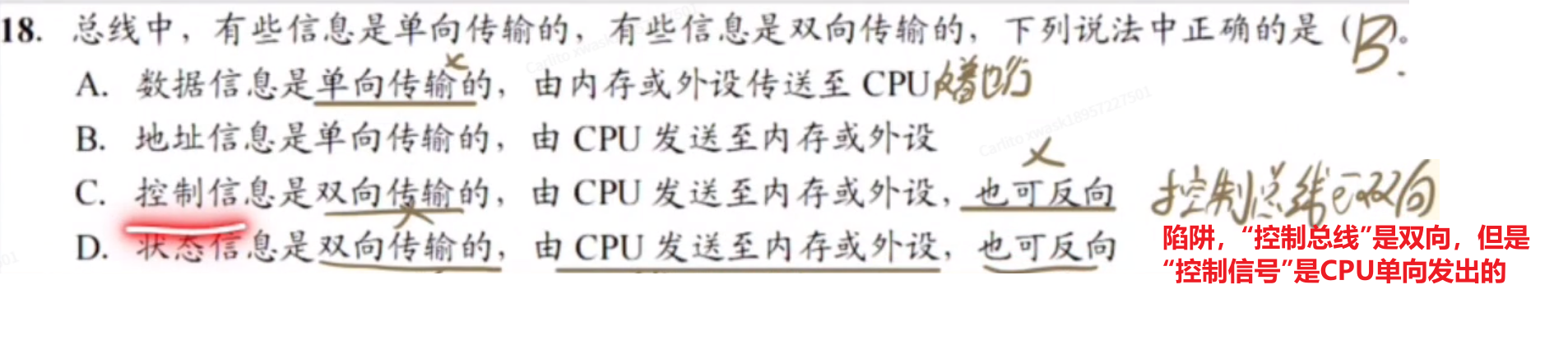

- 【数据总线】:

- 传输【数据信息】,但是要注意**【数据】包含很多种** (比如:纯数据、指令、中断类型、⭐控制命令里的【命令字】......)

- 还要注意,它是**【双向的】,因为有【读出】和【写入】**!!!

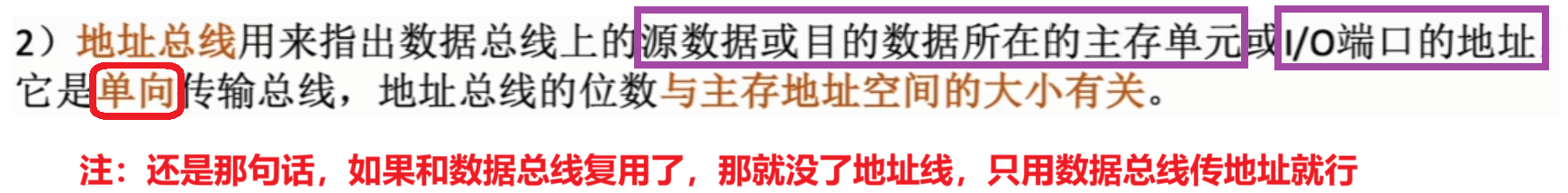

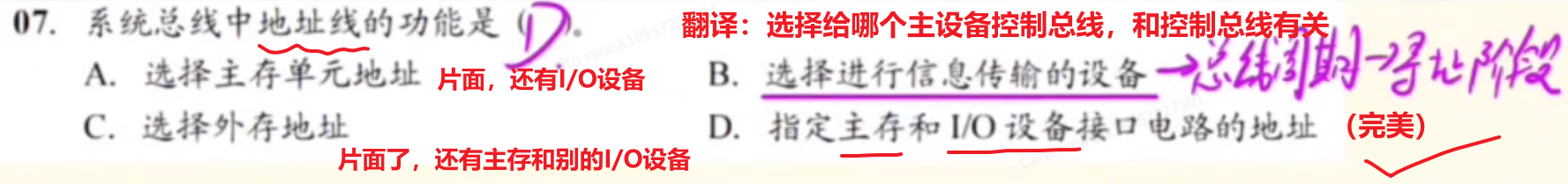

- 【地址总线】:

- 传输**【数据所在的 地址信息】**

- **注意!不止是主存的地址,而是包括了【主存单元】+【I/O设备接口】**2大类的地址!!!!!

- 就【主存】有地址,你找地址也不可能去CPU里找,所以是**【单向】**的

- 【控制总线】:

- 通俗理解:【CU "传出去" 的控制信息】以及【主存(或外设) "返回" CPU的反馈信号】

- 注意也是**【双向】** 的(注意!!!【双向】指的是【控制信息 + 反馈/响应信息】2种信号双向,但是**【控制信号】明确规定只能是CPU单向发出**,下面例题18就有这个坑🕳)

这个图那么多命令信号可能记不住,那么关于【控制总线主要功能】完美的概括说法可以记熟:【主要提供定时信号、操作命令、各种请求 / 回答信号...等等】(下面例题第8题有)

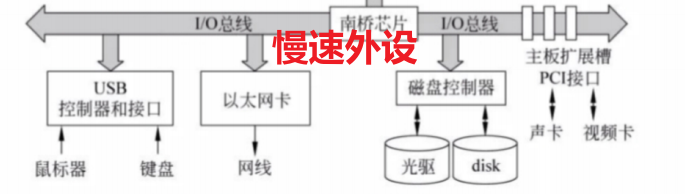

3、【I/O总线】:

- 用于连接【低速外设】,通过I/O接口和系统总线连接

- 目的分离【低速外设】和【高速系统总线】,以提高系统性能

- 常见的有:USB总线、PCI总线

- 注:高速外设用DMA连接

4、【通信总线】:

- 用于【计算机系统之间】或【计算机系统与其他系统(如远程通信设备、测试设备)】之间传信息

- 也被称为【外部总线】

;

注意:

- 【数据通路】是:组合逻辑元件、时序逻辑元件这些东西

- 【数据总线】是:单纯只是传数据的线路而已

【系统总线】结构

系统总线是重点,这里先分清楚它的三种结构!!!

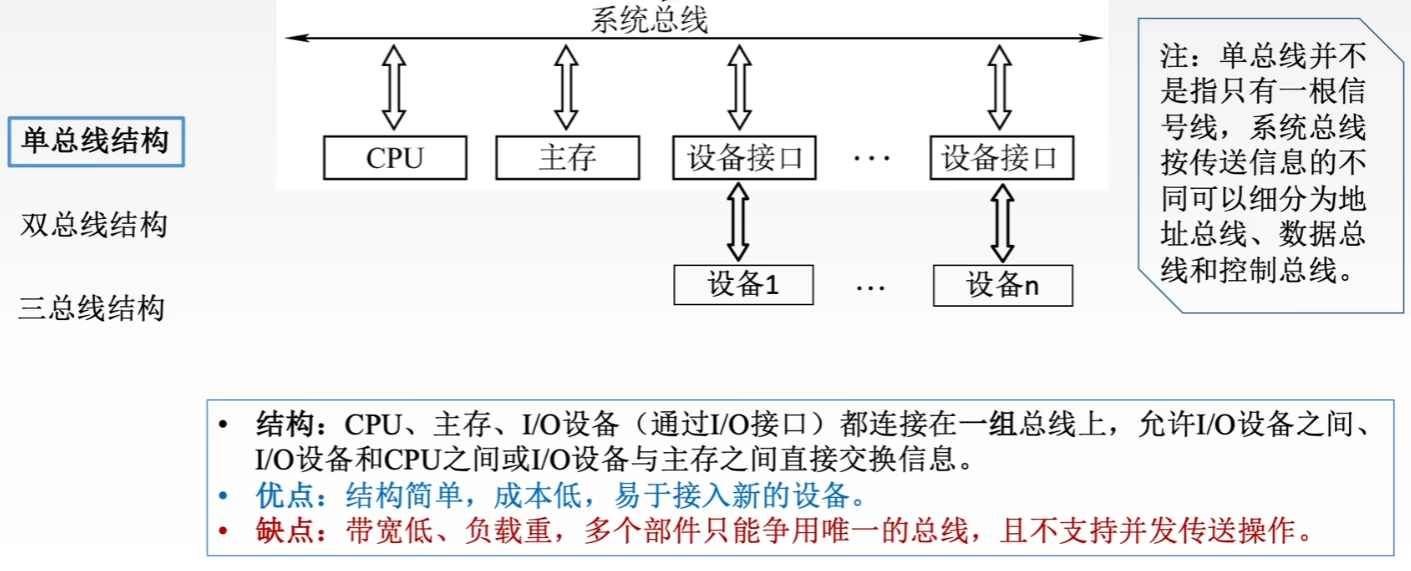

- 【单总线结构】

- 就是所有部件全连一组总线(注意我这里说得是【组】,而不是【1根】!!!)

- 特点就是:

- 容易总线争用、数据冲突!!不支持并发传输!!

- 但是够简单,成本低

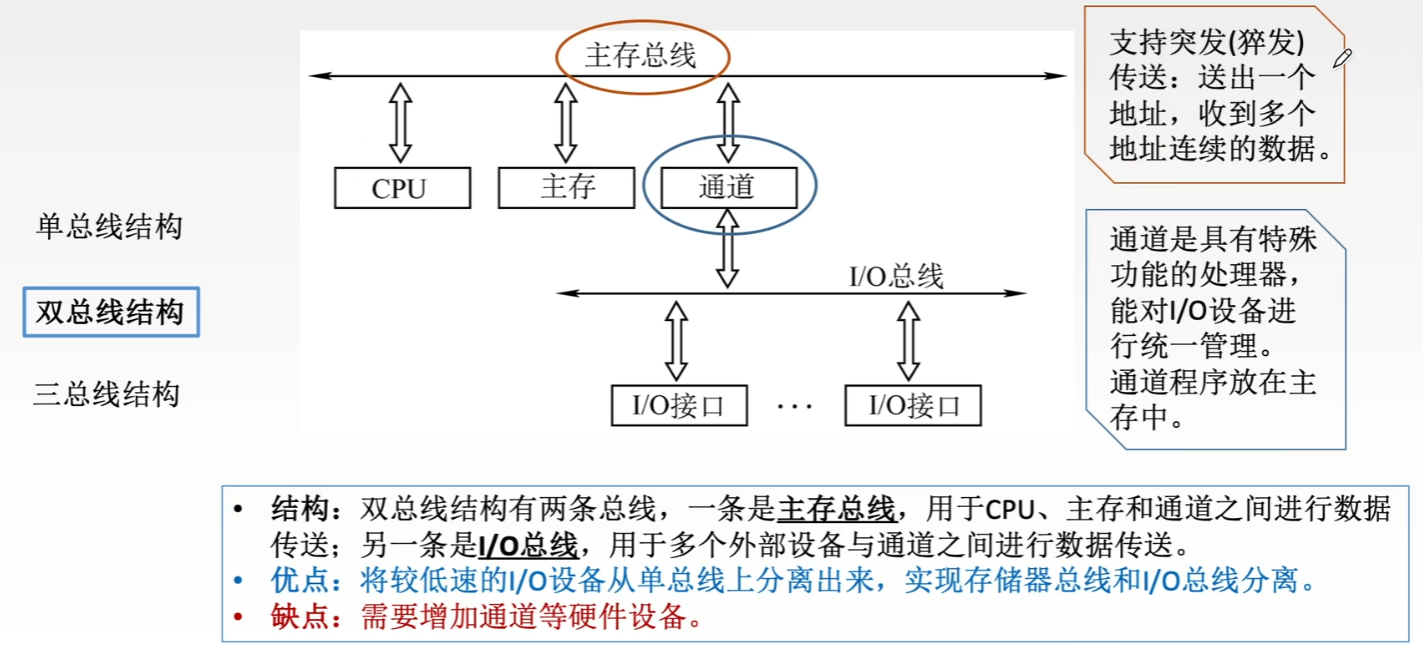

- 【双总线结构】

- 分2组总线,一组是【主存总线】、一组是【I/O总线】

- 特点就是:

- 分离【低速I/O外设】和【主存(高速)总线】

- 注意,【通道 】是一种 "弱鸡版CPU ",可执行I/O指令,他就是代替CPU来统一管理I/O这种慢速外部设备的

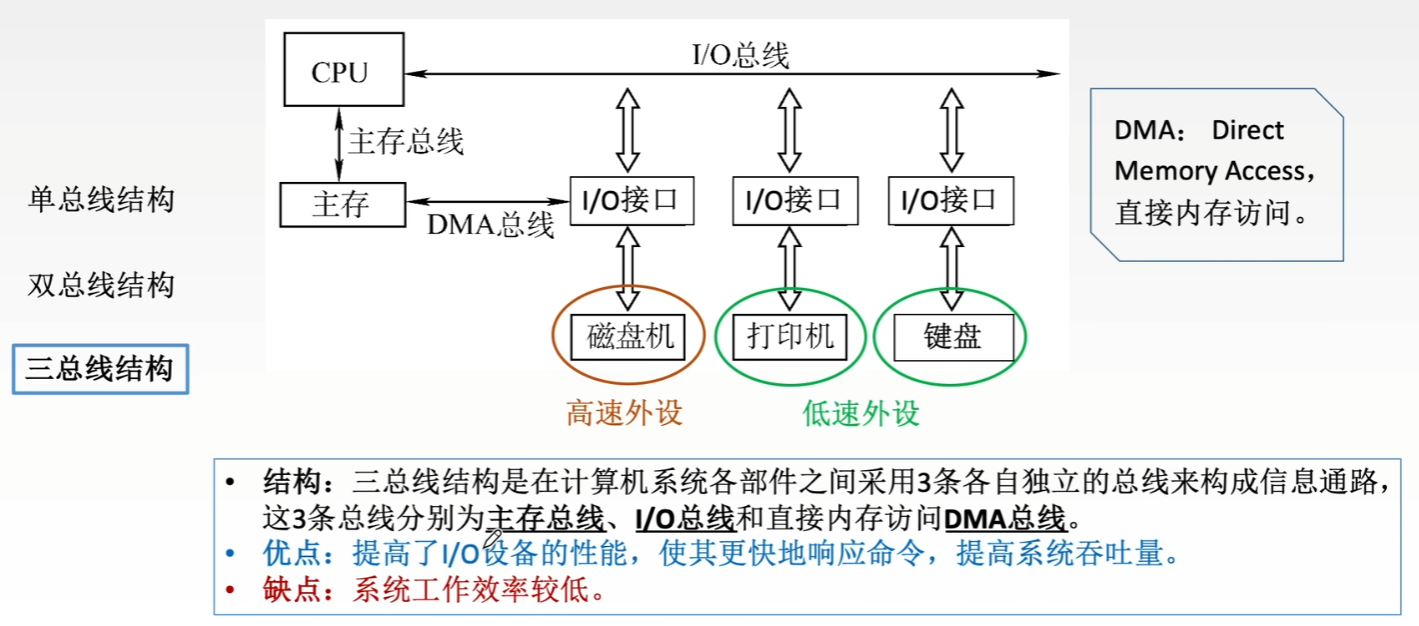

- 【三总线结构】

- 分3组总线,一组【主存总线】、一组【I/O总线】、一组【DMA总线】

- 特点就是:

- 提高了I/O设备性能

- 注意:DMA总线连接的是【高速外设】;另外他跟CPU都连着主存,所以它两不能同时访问主存,要交替着使用,具体后面会学

【提示】

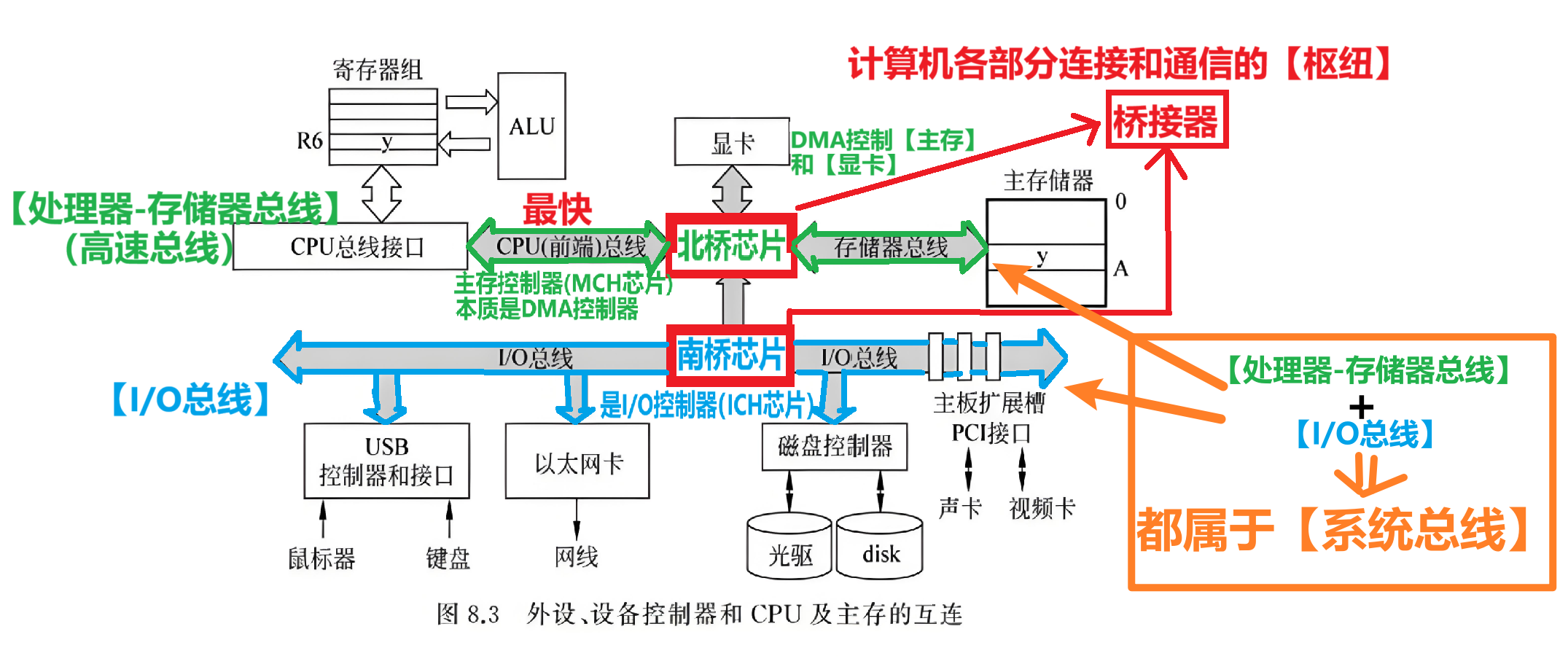

传统上,总线还有一种分类表达方式:

- 分为【处理器-存储器总线】+【I/O总线】

- 其中因为【处理器-存储器总线】很短,所以属于【高速总线】,还细分为:

- 【处理器总线 】:也叫【CPU(前端)总线】

- 是【最快的总线】!!!

- 用于【处理器---北桥芯片】

- 【存储器总线】:

- 由【北桥芯片】控制,连接显卡、主存

- 【I/O总线】:

- 用于连接I/O设备

然后【处理器总线】、【存储器总线】、【I/O总线】还需要一个【枢纽】连接

这也是计算机各个部件连接和通信的【枢纽】,也就是【桥接器】,分为:

- 【北桥芯片】:又叫【MCH芯片】

- 是【主存控制器】,本质是DMA控制器(不明白后期会学,这里有个印象)

- 主存控制器用于【提供主存块】给【Cache】或【CPU寄存器】

- 其中【DMA控制器】用于控制【主存】和【显卡】数据流通

- 【南桥芯片】:又叫【ICH芯片】

- 是【I/O控制器】

- 用于集成USB控制器、以太网控制器、磁盘控制器.....

;

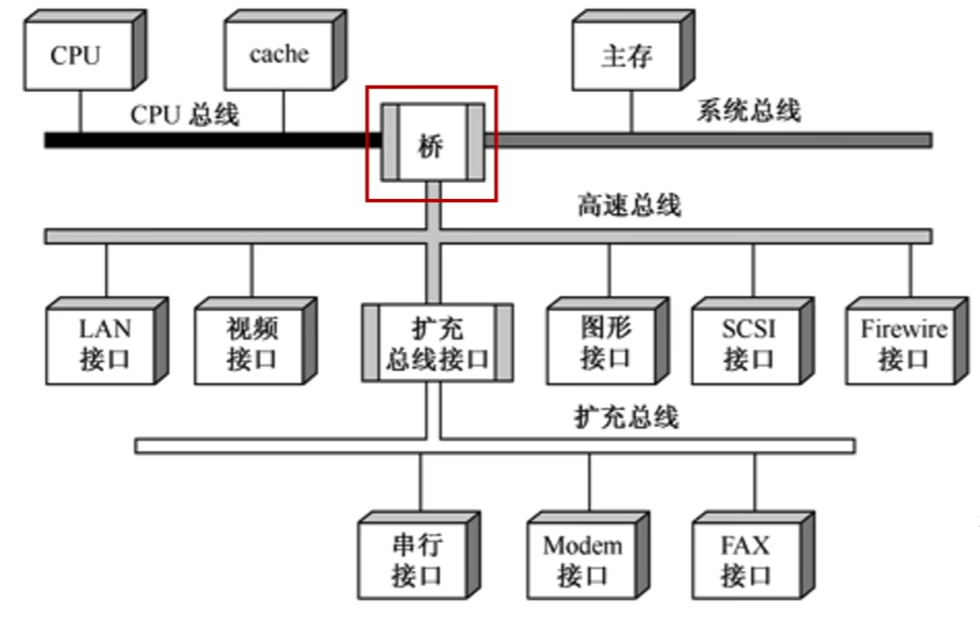

【拓展】

现代计算机依据【桥接器】实现了性能更高的【四总线结构的系统总线】,不考,但是知道就行

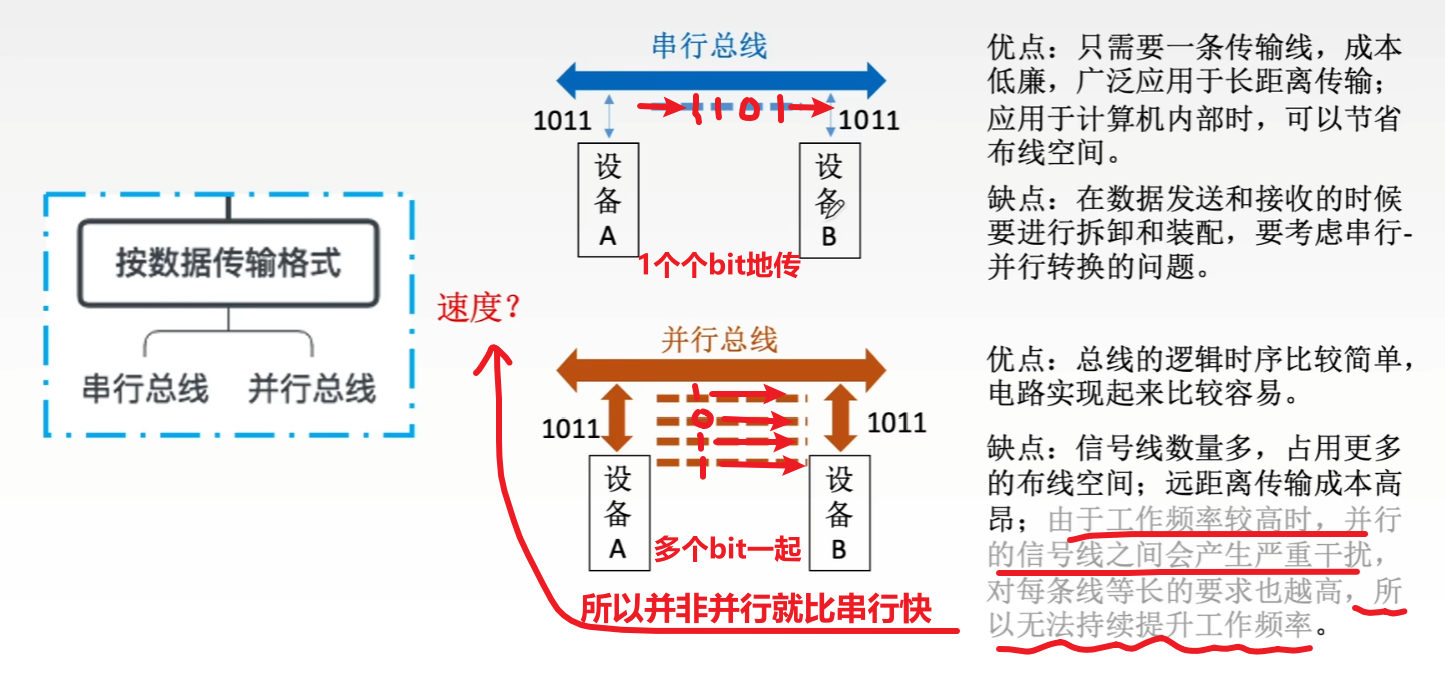

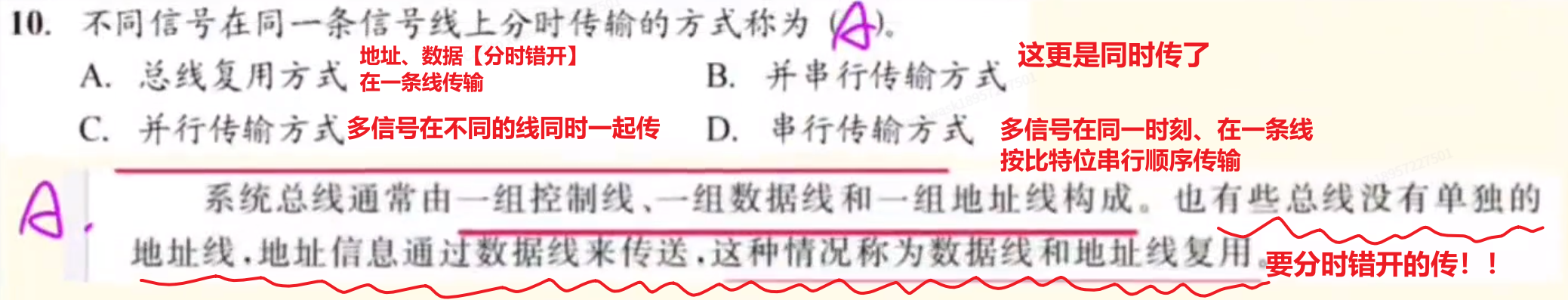

2)按数据传输方式分类

分为【串行总线】、【并行总线】

- 1、【串行总线】:

- 总线只要一或两根线

- 如果是双向传输的线,就只用一根

- 如果是单向传输的线,就只用两根

- 一根线同一时刻只能按单比特位顺序传【串行传输】

- 2、【并行总线】

- 总线还是多根线,都是双向传输

- 每根线传1bit,N根线能同时并行传Nbit,【并行传输】

- 重点:

- 【并行总线】并不一定比【串行总线】快,因为他多根线在一块容易受干扰,影响工作频率,线路越远就越受影响而变慢;所以【并行总线】只适合短距离

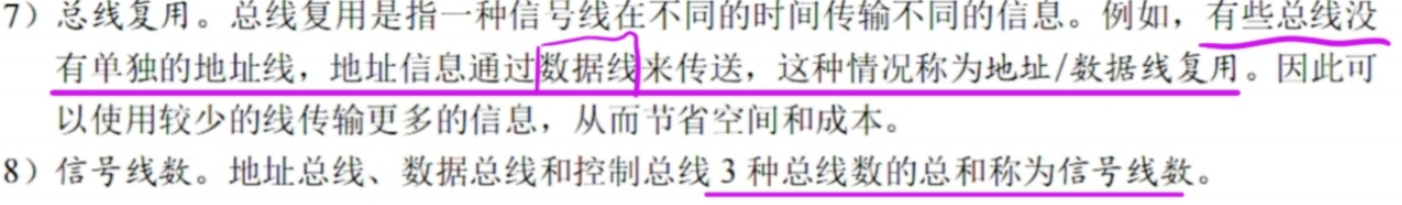

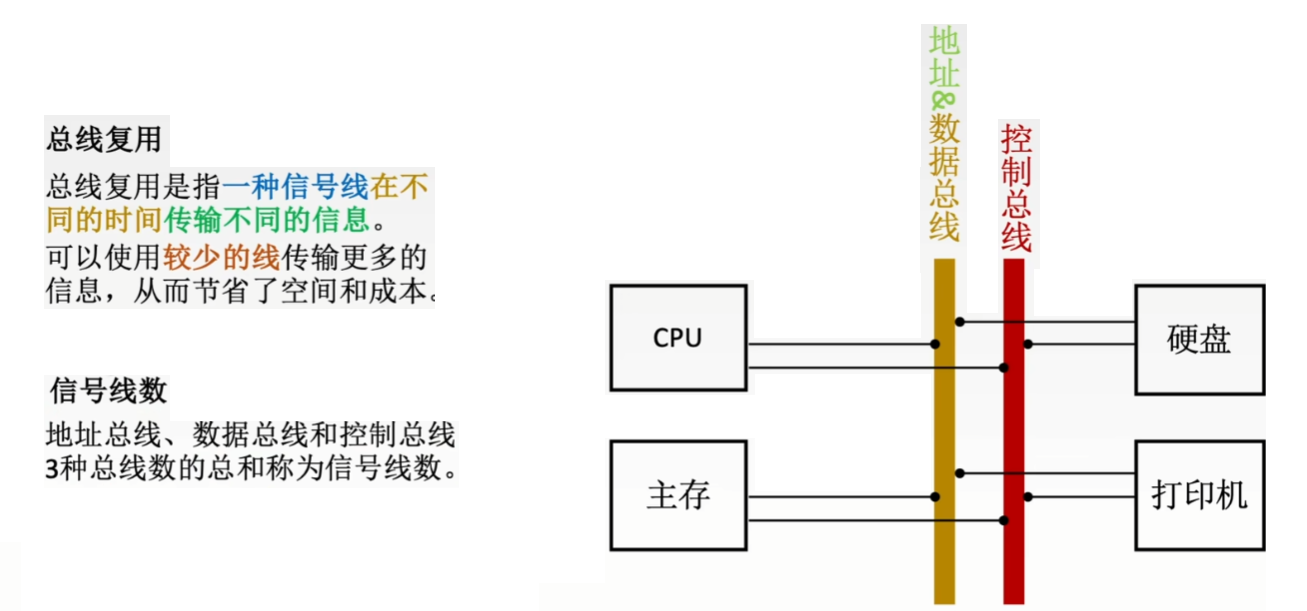

- 还有一种特殊传输方式:【总线复用】

- 这种总线没有单独的【地址线】,需要用【数据线】一起传【数据 + 地址】,不过重点是**【地址】和【数据】要 "分时错开" 地传**,不然就混淆了

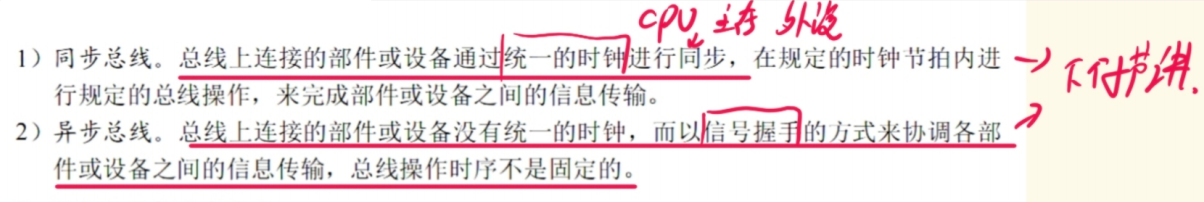

3)按时序控制方式分类

这是后面的重点,所以这里先不展开解释

4)总结

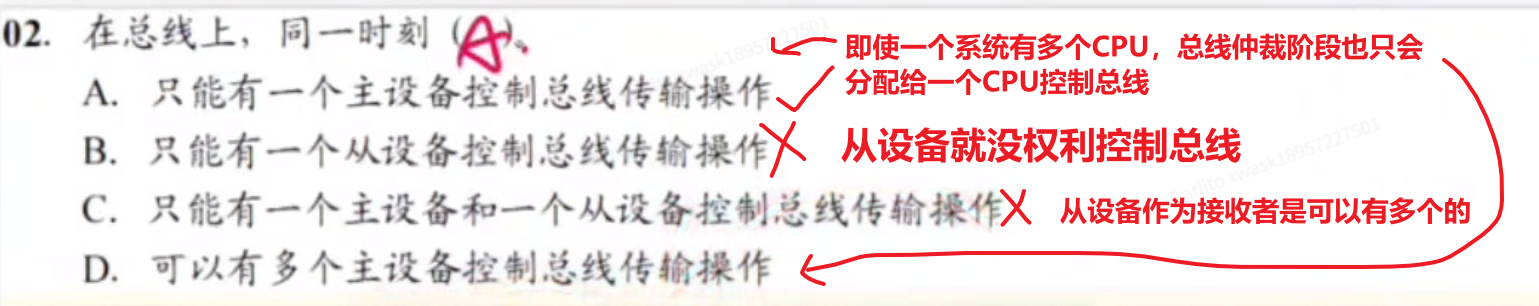

5)例题

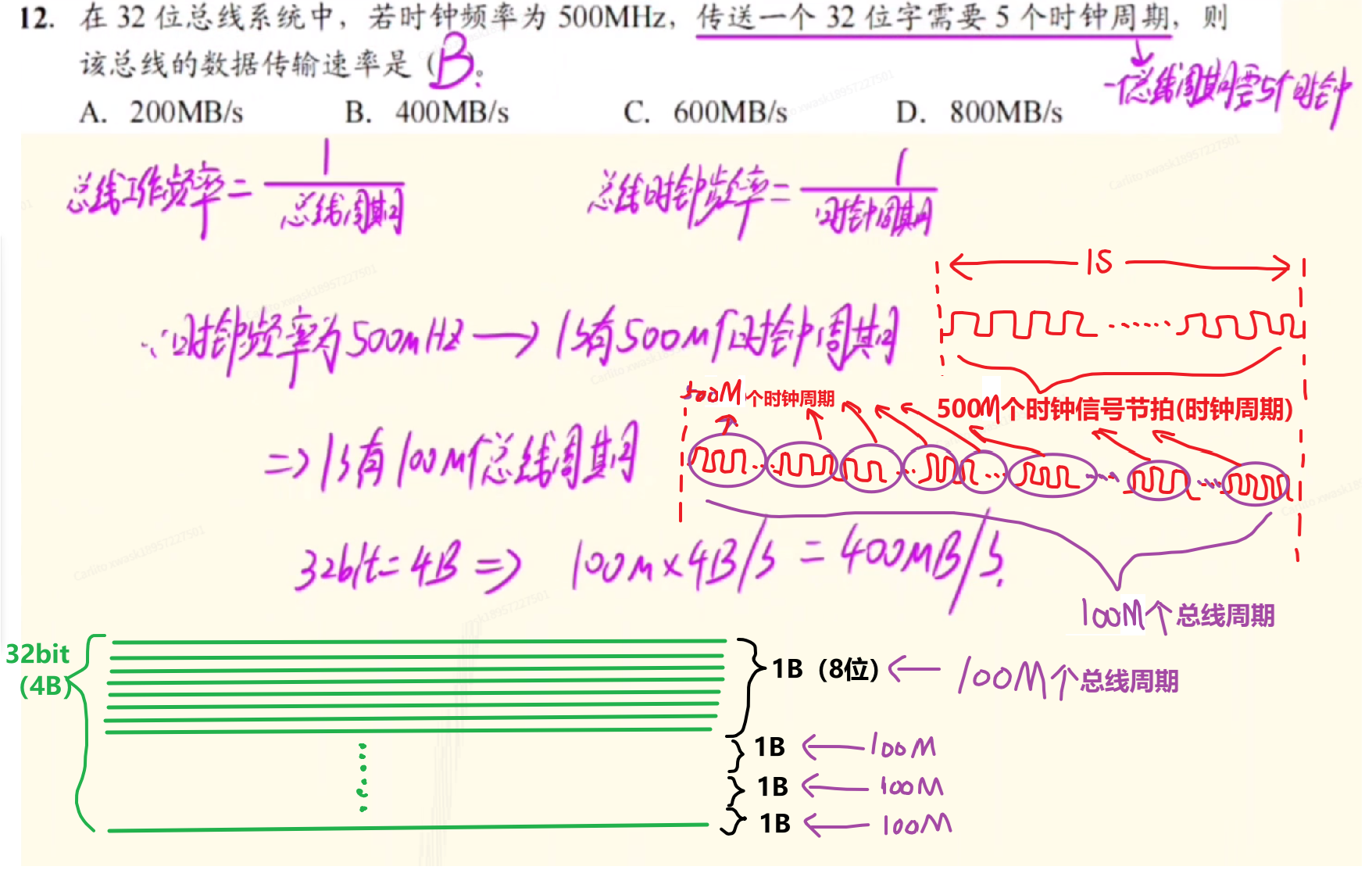

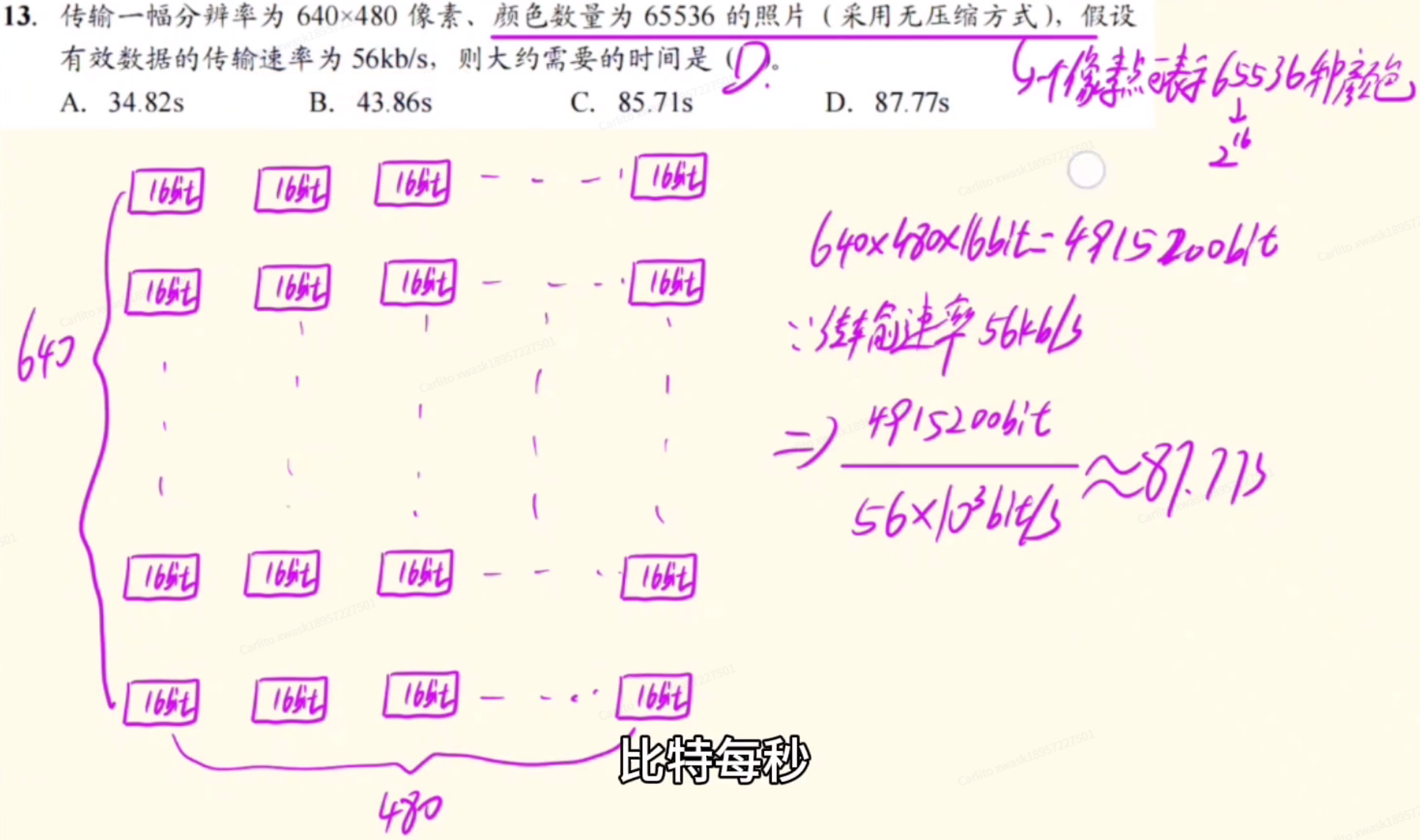

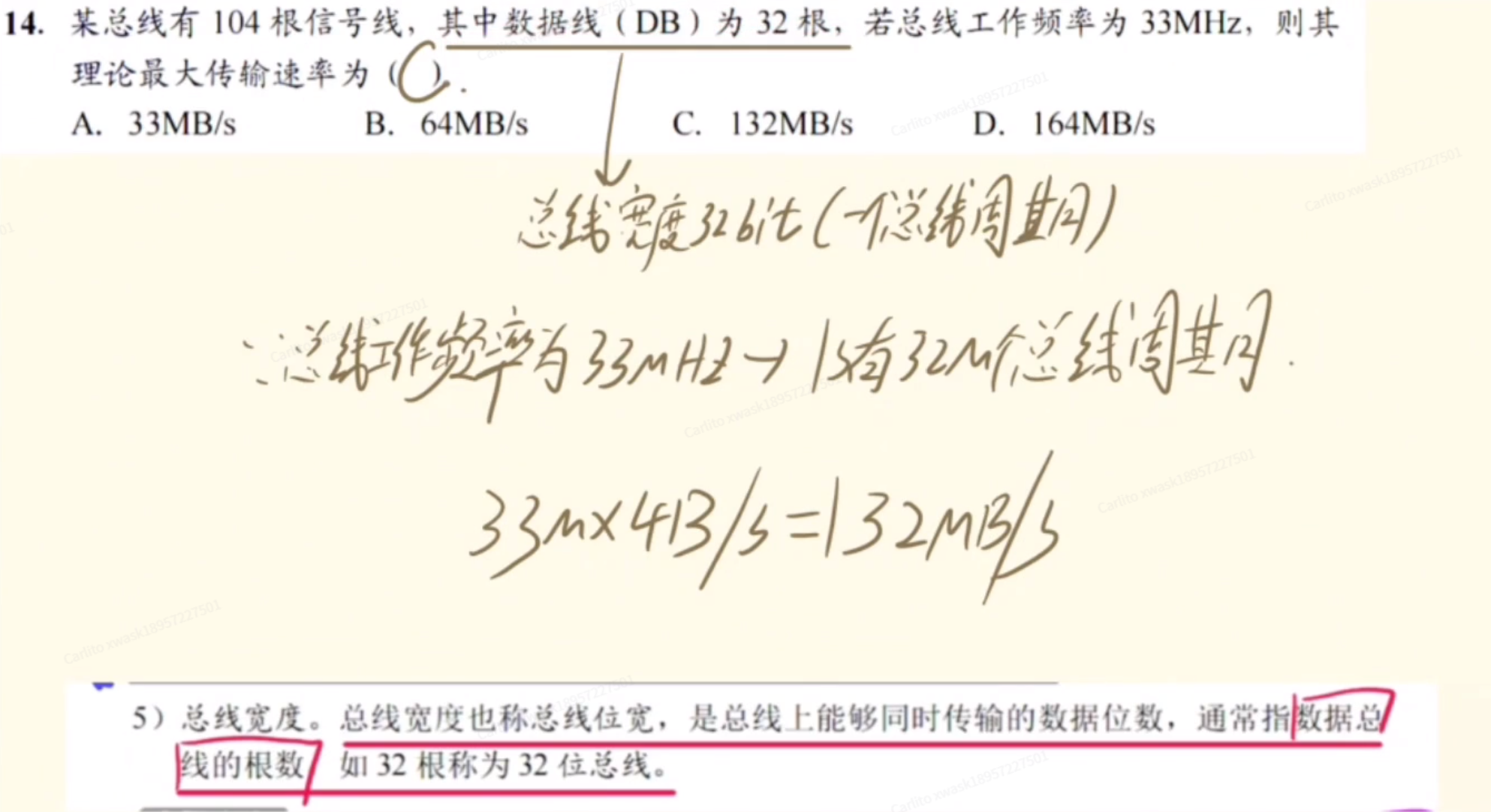

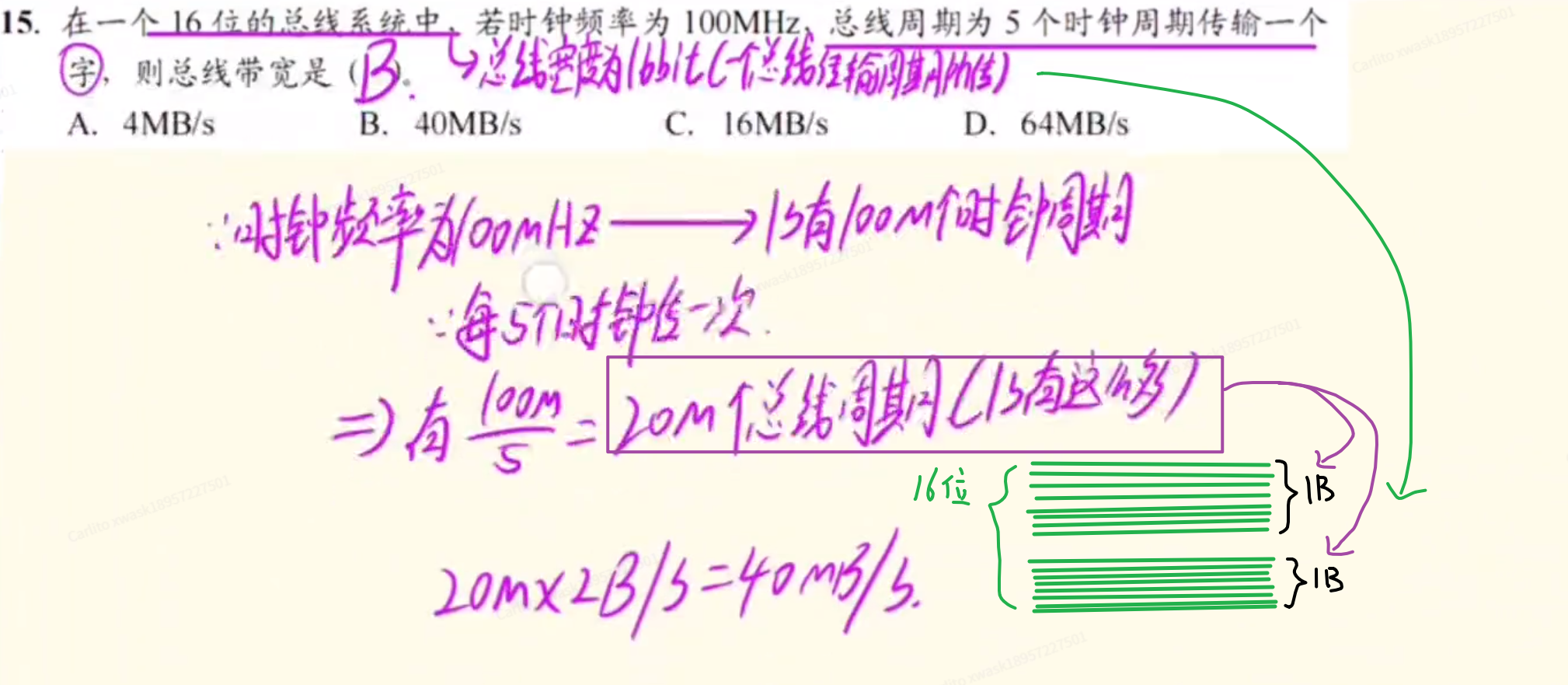

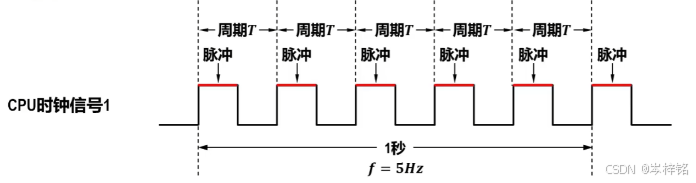

四、总线的性能

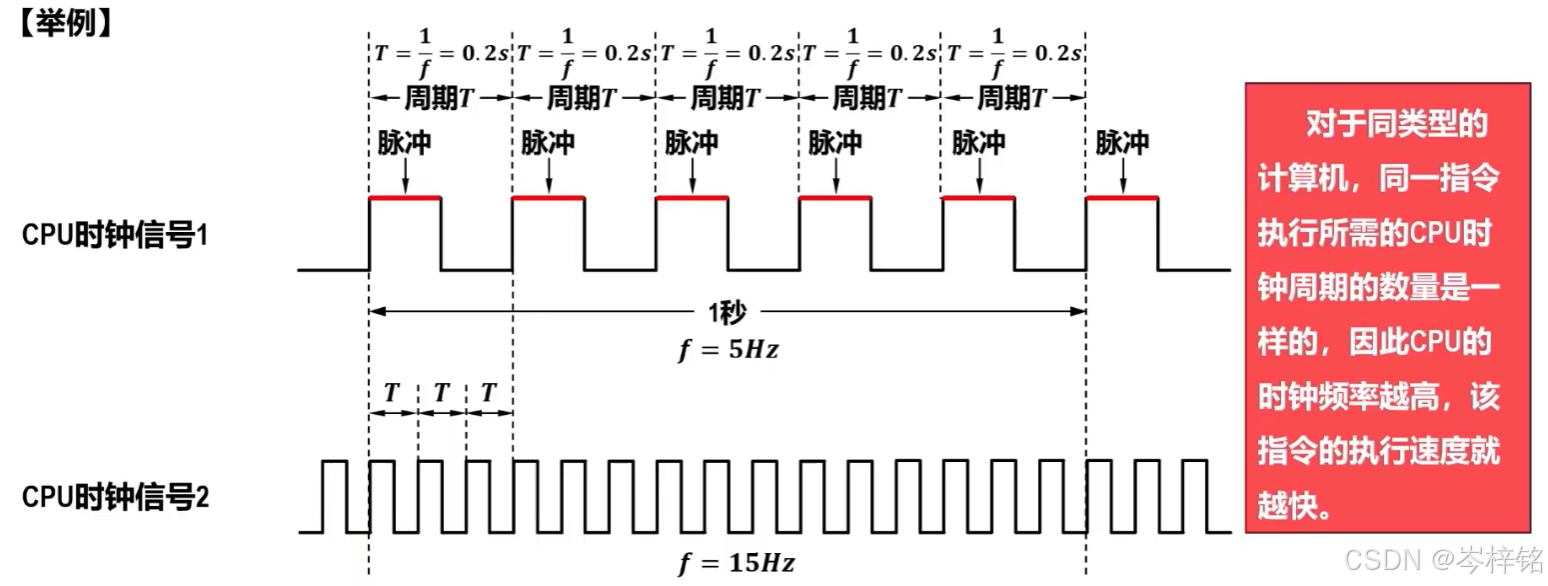

提示:涉及 "时钟周期" 的都可以按照第一章的计算机性能指标的知识点来理解,没什么区别

1、速度、时间方面

- 【总线的时钟周期】

- 概念:就是CPU时钟周期、描述总线传输周期的【最基本、最小单位】、一个信号节拍

- (因为计算机各个部件基本都是靠这个时钟控制)

- (当然现代计算机种,总线时钟周期也可能由【桥接器】提供)

- 计算:【时钟周期T】=【1 / 时钟频率f】

- (理解为是1秒里的一个信号节拍要多久;是**【时钟频率】的【倒数】**)

- 【总线的时钟频率】

- 概念:1秒内有几个时钟周期、1秒有多少信号节拍

- 计算:【时钟频率f】=【1 / 时钟周期T】

- (是**【时钟周期】的【倒数】**)

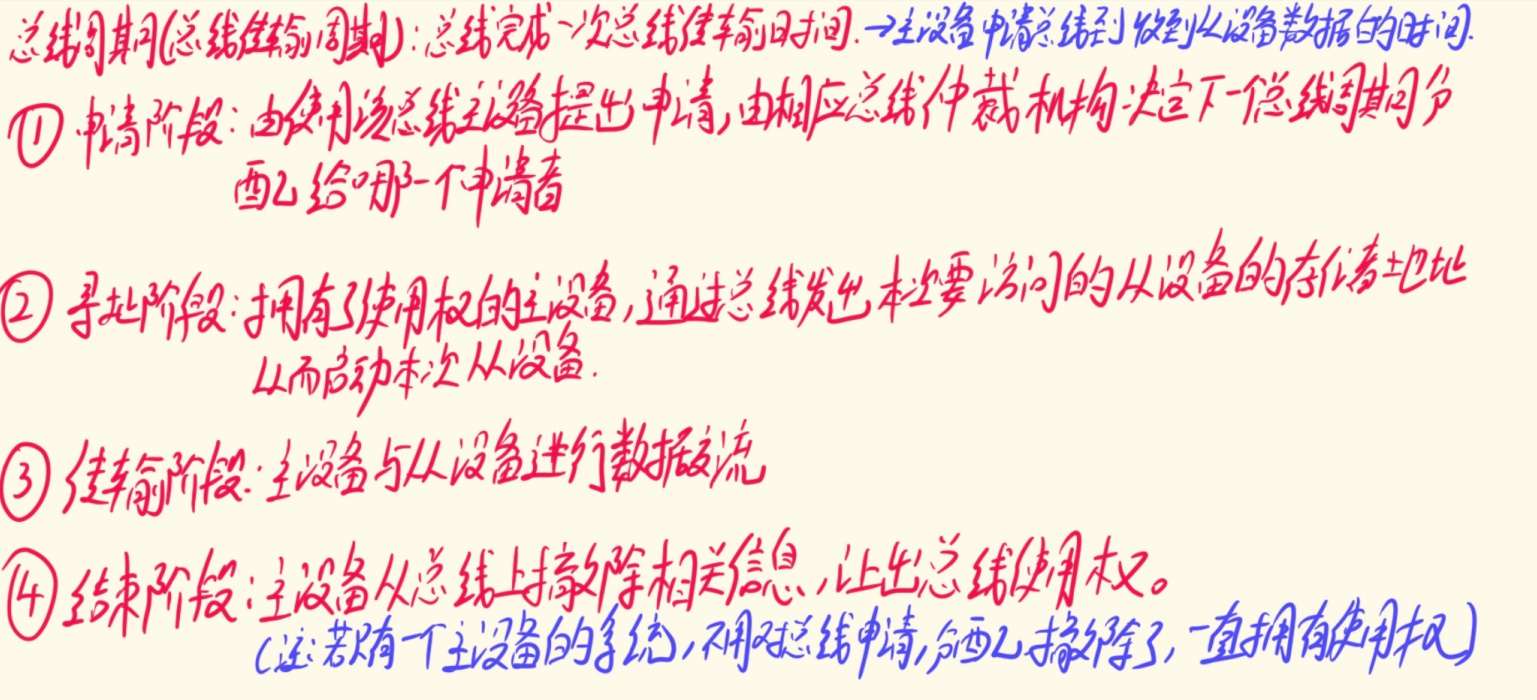

- 【总线的传输周期】

- 概念:总线1次操作所需时间(主设备申请总线------从设备响应回信息的时间)

- (可理解"指令周期"的概念)

- 包含了【申请阶段】+【寻址阶段】+【传输阶段】+【结束阶段】

- 计算:【总线传输周期 = N * 时钟频率】、【总线传输周期 = 1 / 总线工作频率】

- (是**【总线工作频率】的【倒数】**)

- 【总线的工作频率 】

- 概念:1秒内传几次数据

- (理解为速度,总线这个"工人"1秒能干多少活)

- 计算:【总线工作频率 = 时钟频率 / N】、【总线工作频率 = 1 / 总线传输周期】

- (是**【总线传输周期】的【倒数】**)

;

;

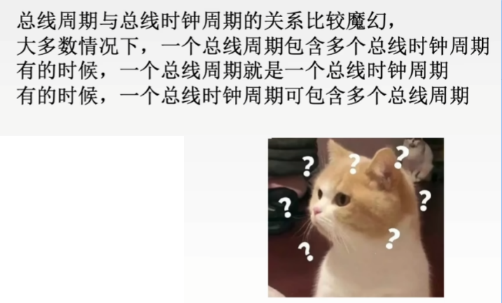

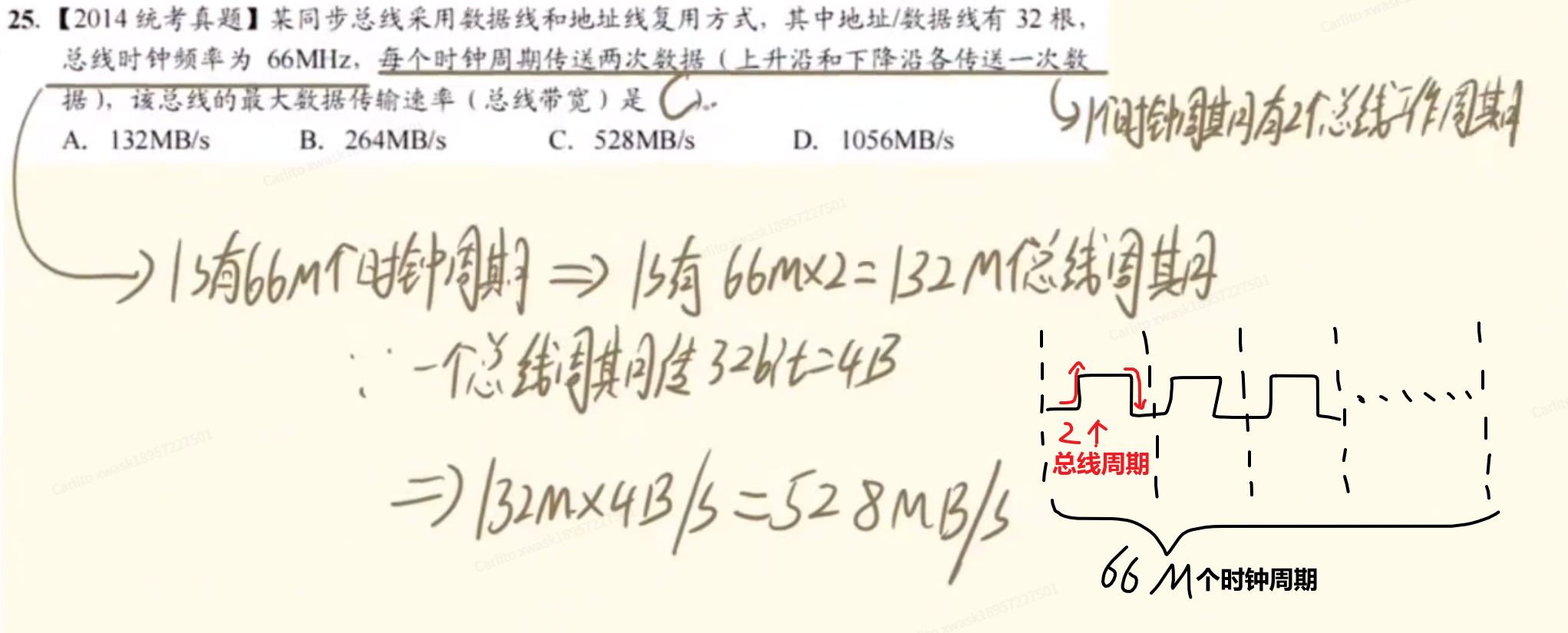

- 【总线传输周期】和【总线时钟周期】的关系

没有固定的关系,有可能【1个传输周期--->多个时钟周期】、【1个传输周期--->1个时钟周期】、【多个传输周期--->1个时钟周期】

比如【多个传输周期--->1个时钟周期】情况:

如果检测到**

上升沿**(电信号由低电平变为高电平),可以进行一次总线的数据传输。如果检测到**

下降沿**(电信号由高电平变为低电平),此时又会传送一组总线的数据。在这样的【1个时钟周期内】,上升沿和下降沿都进行了一次总线的数据传输。这就意味着包含了【两个总线传输周期】

2、总线宽度、总线带宽

【总线宽度】

- 也叫【总线位宽】

- 就是【总线上同时能传几位数】

- (一般指【数据总线 的 根数】,如32跟数据线组成数据总线,就称该计算机32位总线)

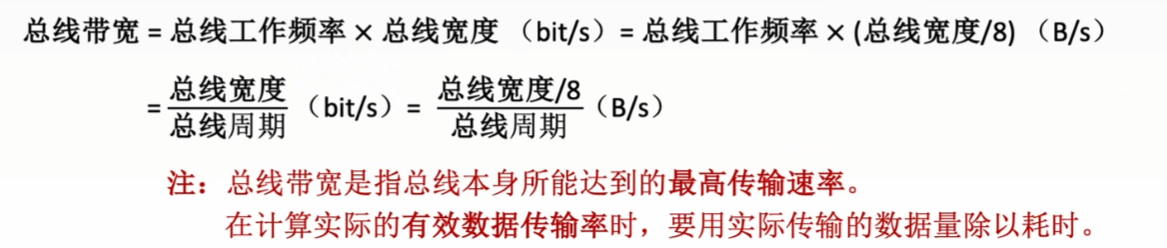

【总线带宽】

- 带入计算机网络的带宽概念,就是单位时间内,总线最多可传输数据的位数(总线最大数据传输速率)

- 通常用【 字节/s 】、【 B/s 】表示

- 计算公式:你就理解为一条马路有n条道(总线宽度)、每条道1秒有几辆车通过(总线工作频率),它两相乘不就是这整个马路1秒最大的车辆吞吐量了吗

别的一些性能指标概念

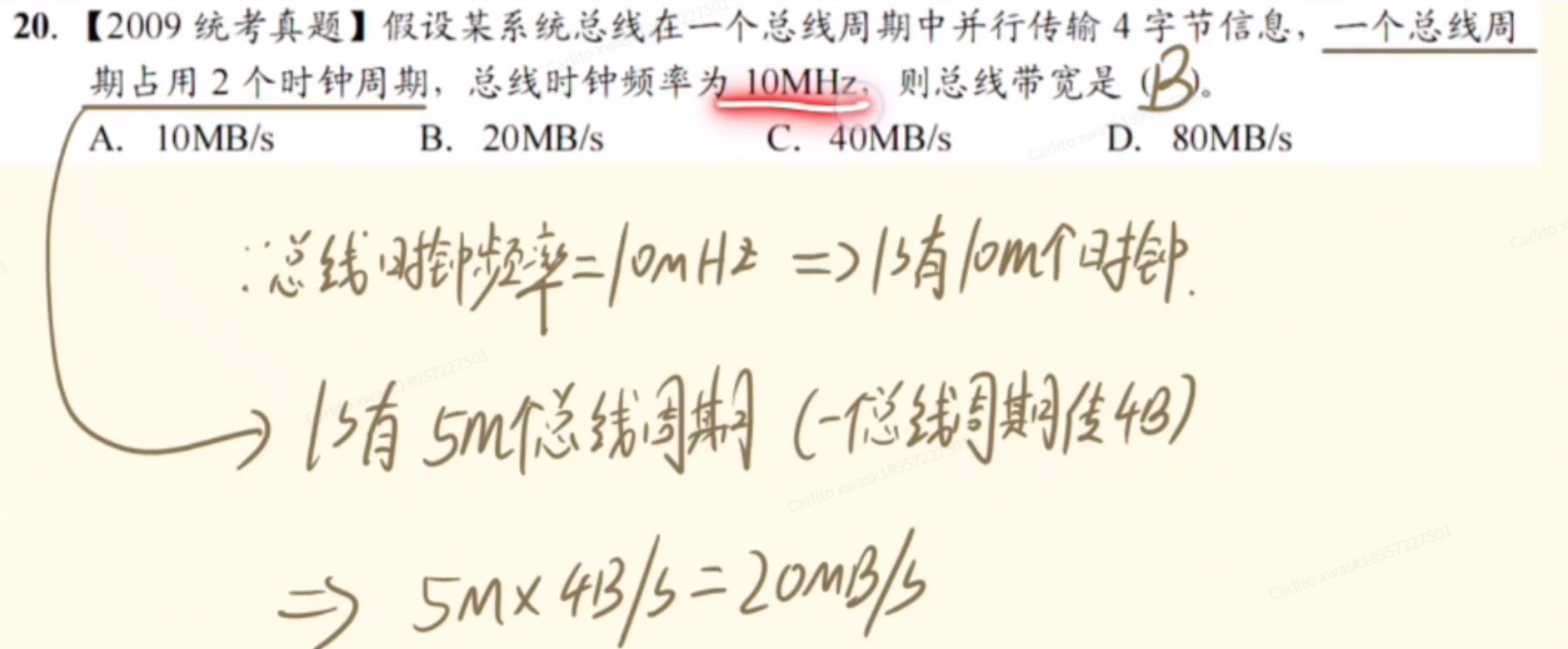

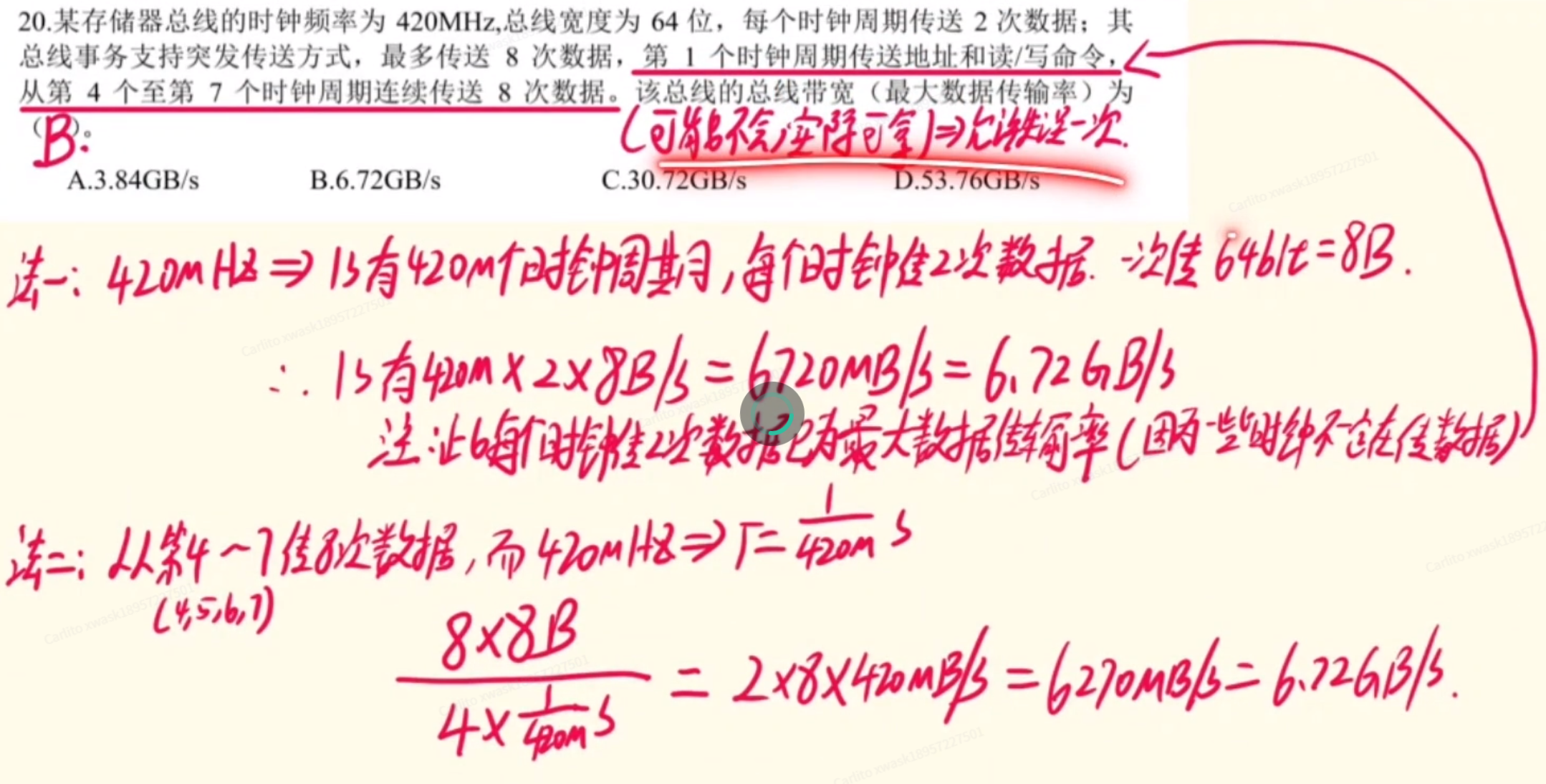

例题

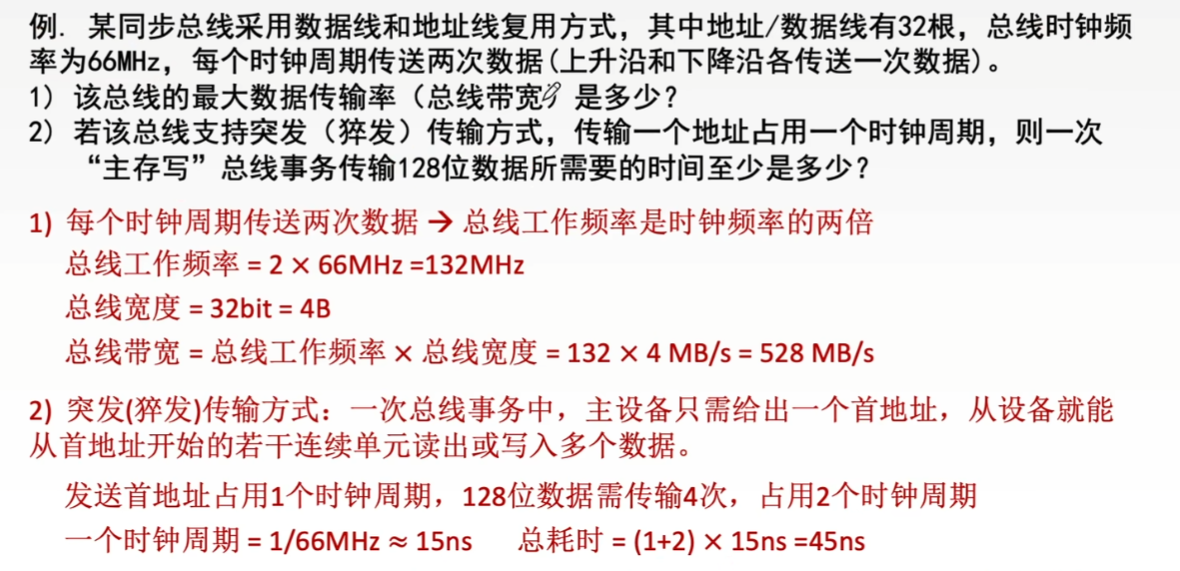

下面是王道的解释,还涵盖了【突发传输方式】

五、冷门但是会考的死人知识点

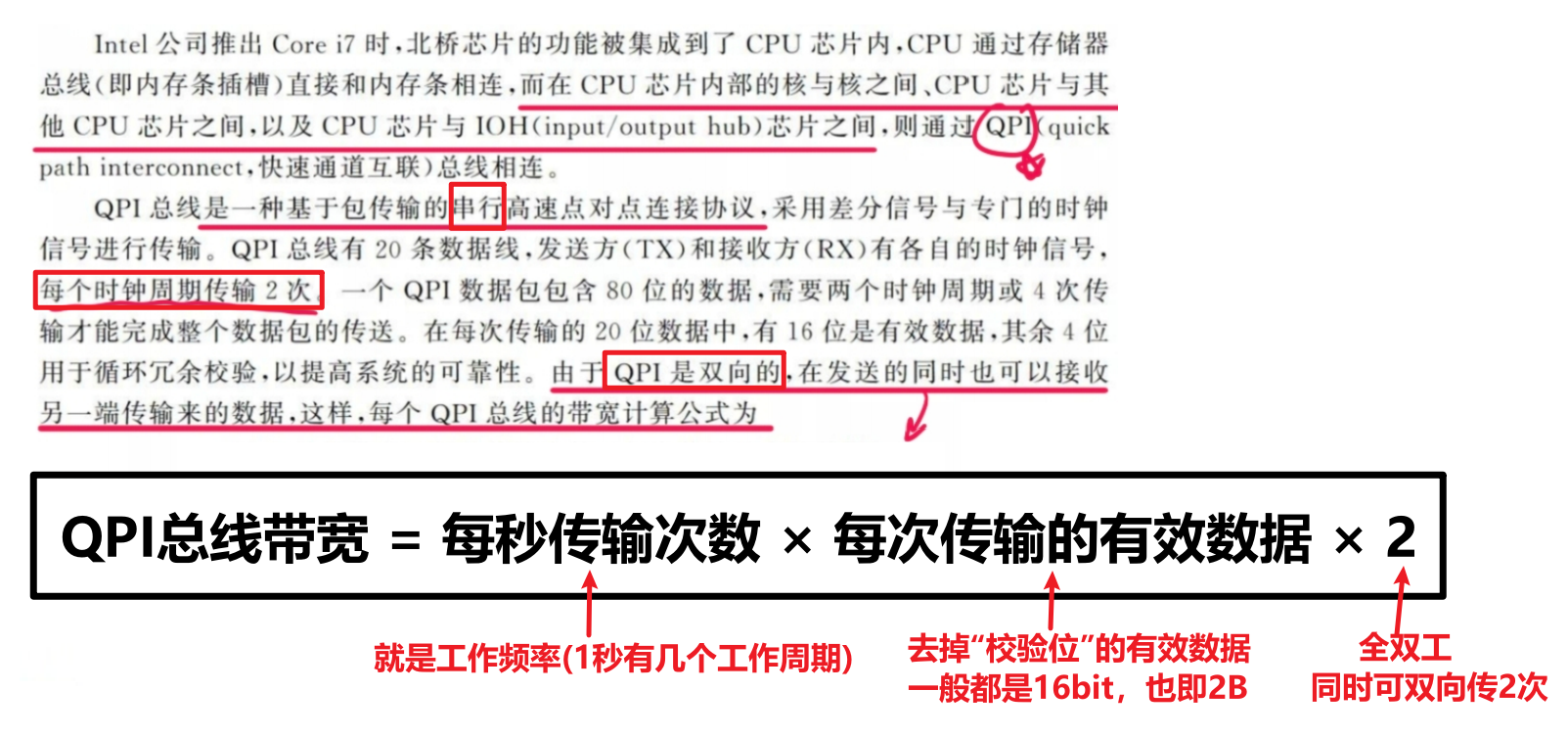

1、【处理器总线】里的 "QPI总线"

别管是啥了,记住重点:

- 1、是CPU内部的核与核、CPU与其他CPU之间的总线

- 2、串行传输

- 3、一个时钟周期可以传2次,也就是【1时钟周期】含【2个总线周期】

- 4、全双工,可以同时【双向传输】(你可以理解为2组线各自反向传,1个总线一时钟周期传2次,那其实相当于1个QPI总线(2组线)在1时钟周期可传4次)

- 5、所以公式就是【QPI总线带宽 = 每秒传输几次 × 每次传输的有效数据 × 2】

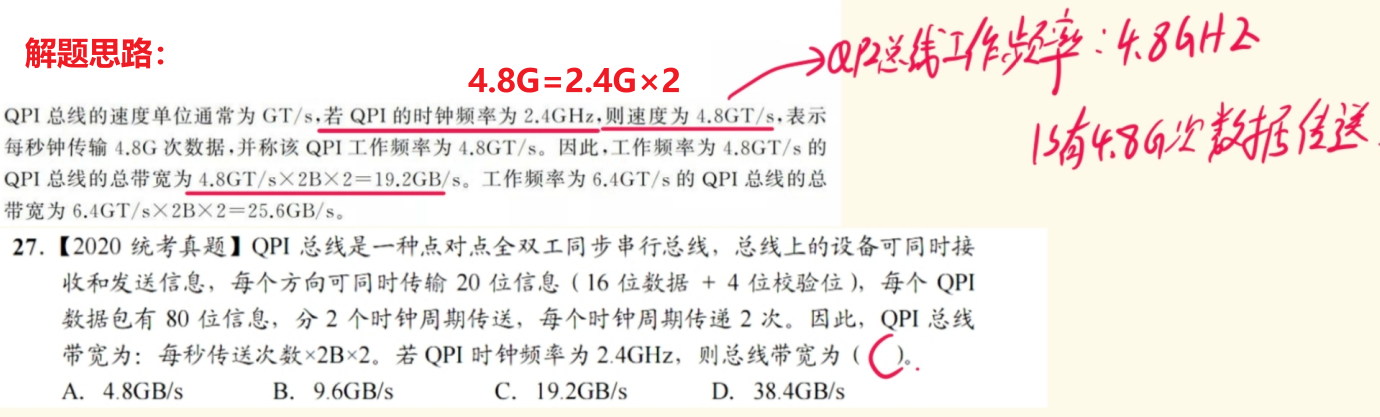

【例题】

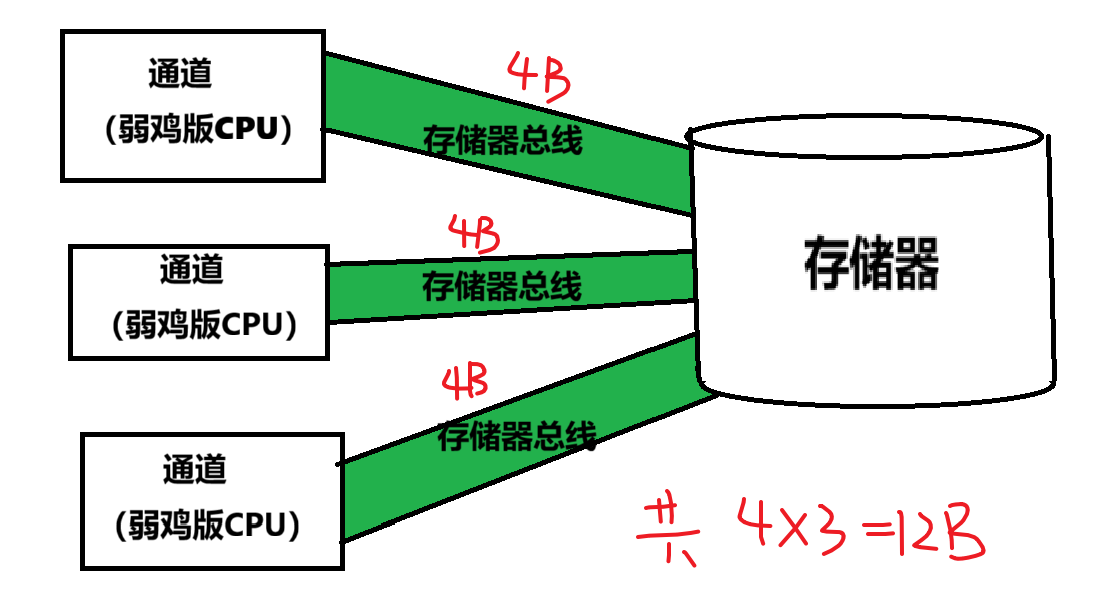

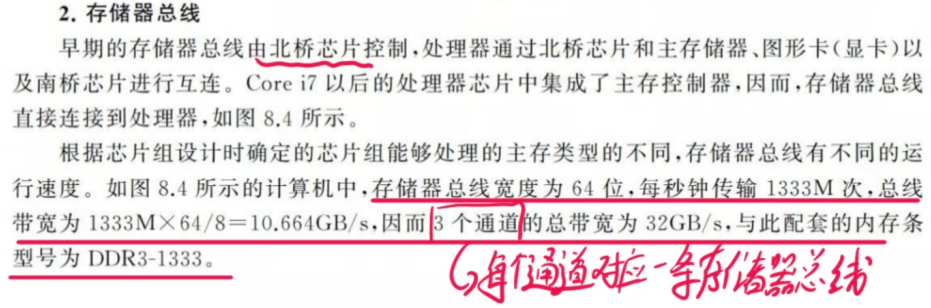

2、【存储器总线】

虽然大致上计算还是按【总线性能】那样,但是多一个一个要素:【通道】

我们只需要把【通道】理解成一个 "弱化版CPU",那有几个通道,就说明连了几组存储器总线,我画个图方便大家理解

【例题】

前面依旧是按【总线周期(每秒传几次)× 总线位宽(单位是B)】求出一个存储总线的工作频率,但是因为3个通道要连3个存储总线,所以在这个基础上【×3】即可

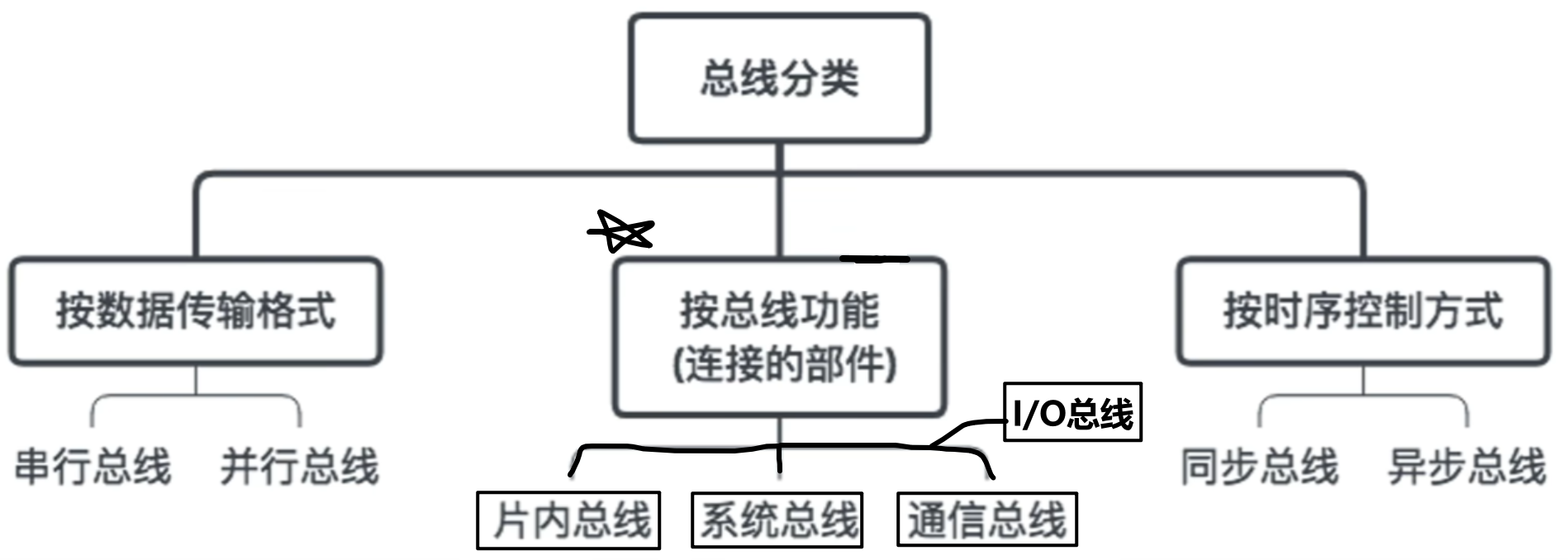

3、【I/O总线】

这更是死人知识点,能想出来这题的出题人家里也是中邪了

上面直接不看,只看这:

- 1、现在的I/O总线叫PCI-Express,是【串行】传输

- 2、通路数只能是【偶数】,别管为什么,题目说通路是奇数直接排除

- 3、每10bit数据里有2位垃圾数据,所以相当于【每10位】==>【传1B】(打比方传了50bit数据,那也就是传了50bit / 10 = 5B数据)

- 4、还有2差分信号线,甭管是啥了,反正就相当于也是全双工通道,一次可传2反向信息

- 5、接受速率是:2.5Gb/s,不过考试题目应该会给出

- 6、所以公式就是【PCI-Express带宽 = 2.5Gb/s × 2 × 通路数 / 10】