题目汇总版--链接:

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-CSDN博客

【硬件-笔试面试题-81】硬件/电子工程师,笔试面试题(知识点:详细讲讲同步时钟与异步时钟通信)

1、题目

详细讲讲同步时钟与异步时钟通信

2、解答

在数字系统中,时钟是协调电路工作的 "时间基准"。根据通信双方是否使用同一时钟源,可分为同步时钟通信 和异步时钟通信,二者在时序控制、数据传输方式和适用场景上有显著差异。

一、同步时钟通信(Synchronous Communication)

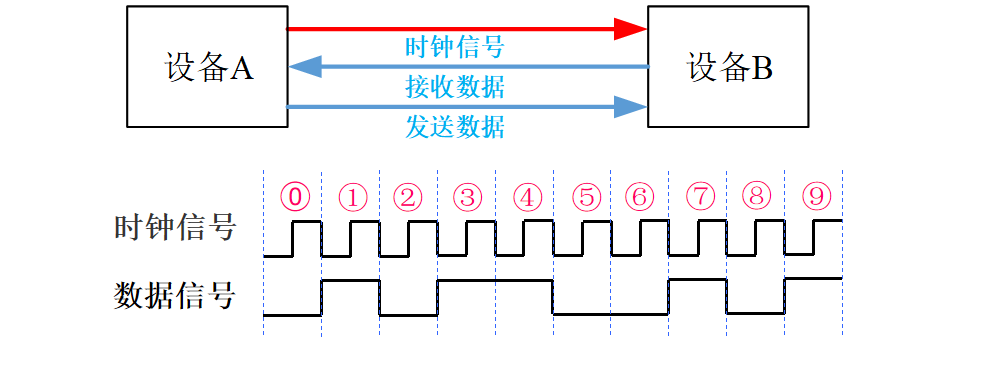

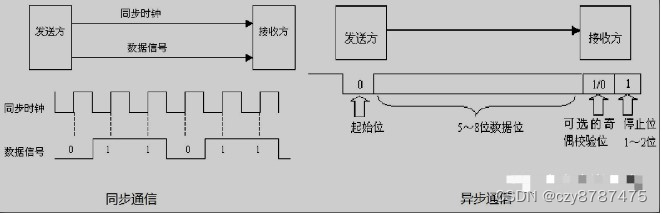

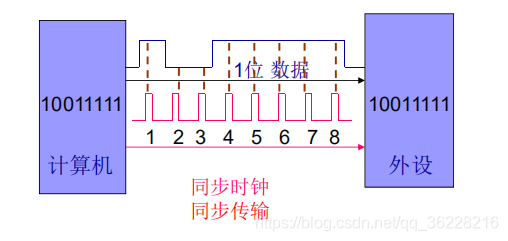

同步时钟通信中,发送方和接收方使用同一个时钟信号(或严格同步的时钟信号) ,数据传输的节奏由该时钟统一控制。

1. 核心特点

- 共享时钟源:发送方和接收方的时钟信号由同一振荡器产生,或通过时钟同步机制(如 PLL 锁相环)保持严格相位对齐(相位差固定,频率相同)。

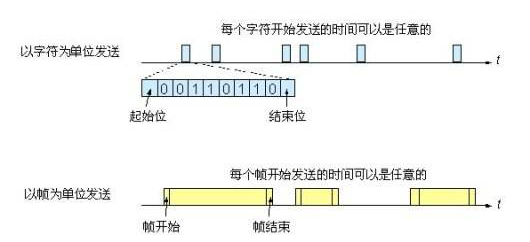

- 数据连续传输:数据以固定速率连续发送,无需额外的 "起始 / 停止" 信号标记帧边界,时钟信号直接定义每一位数据的采样时刻。

- 时序严格对齐:发送方在时钟的上升沿 / 下降沿发送数据,接收方在相同(或固定延迟)的时钟沿采样数据,确保数据被正确读取。

2. 典型工作流程

- 发送方和接收方通过硬件线路共享时钟(如单独的 CLK 线),或接收方从发送方的信号中提取时钟(如曼彻斯特编码的自同步)。

- 数据在时钟的驱动下按固定周期传输,例如:时钟频率为 100MHz 时,每 10ns 传输 1 位数据。

- 接收方根据时钟边沿判断数据位的起始和结束,直接采样数据线上的电平(高 / 低代表 1/0)。

3. 优势

- 传输效率高:无需额外的同步开销(如起始位、停止位),数据帧可连续传输,带宽利用率高。

- 速度快:适合高频、高速场景(如 GHz 级),因为时钟同步确保了精确的采样时机。

- 电路实现简单:接收方无需复杂的时钟恢复逻辑,只需按固定时钟采样即可。

4. 劣势

- 时钟同步要求高:时钟信号的延迟、抖动(Jitter)或噪声可能导致采样错误(如建立时间 / 保持时间违规)。长距离传输时,时钟信号衰减或相位偏移更明显,同步难度大。

- 布线约束严格:在 PCB 设计中,时钟线和数据线需严格等长(减少延迟差),增加布线复杂度。

- 灵活性低:通信双方必须严格同步,若一方时钟异常,整个通信链路会失效。

5. 典型应用

- 高速总线:如 SPI(Serial Peripheral Interface,有单独 CLK 线)、I²C(虽无专用 CLK 线,但 SCL 时钟由主设备提供,从设备严格跟随)、DDR 内存(双数据率同步时钟)。

- 芯片内部互连:CPU 与缓存、FPGA 内部逻辑块之间的通信(片内时钟同步性好)。

二、异步时钟通信(Asynchronous Communication)

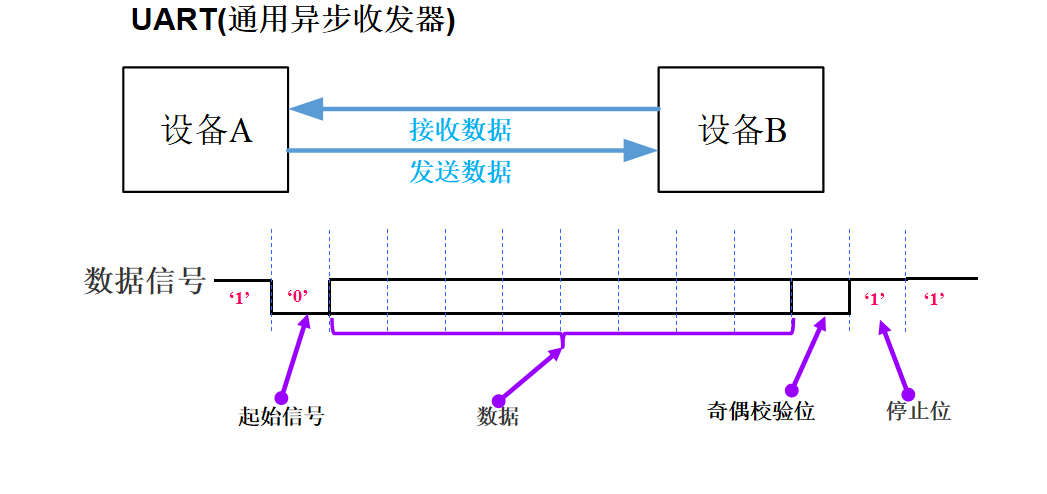

异步时钟通信中,发送方和接收方使用各自独立的时钟源 ,时钟频率可不同(或允许一定偏差),数据传输的同步不依赖共享时钟,而是通过信号本身的特征(如起始位、停止位)实现。

1. 核心特点

- 独立时钟源:发送方和接收方的时钟由各自的振荡器产生,频率可存在误差(通常允许 ±5%~±10% 偏差),无需同步。

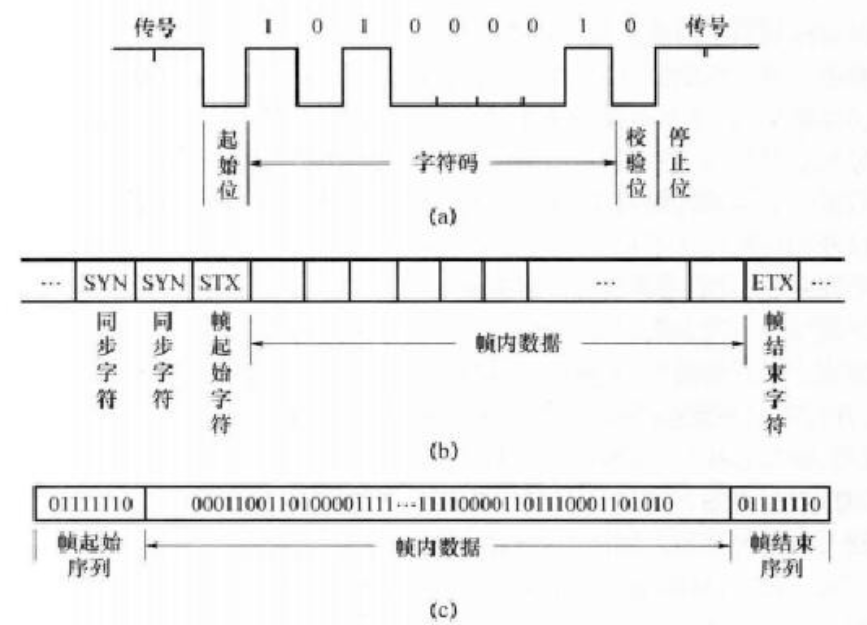

- 帧格式带同步信息 :每帧数据包含起始位 (标记数据开始)、数据位 (有效信息)、校验位 (可选,用于错误检测)和停止位(标记数据结束),通过这些信号实现接收方的同步。

- 采样依赖信号边沿:接收方通过检测起始位的边沿(如从高电平到低电平的跳变)触发内部时钟,开始对后续数据位采样。

2. 典型工作流程(以 UART 为例)

- 发送方要传输数据时,先发送 1 个 "起始位"(低电平),通知接收方 "数据即将到来"。

- 接收方检测到起始位后,启动内部时钟(频率通常是数据率的 16 倍),在每一位数据的 "中间时刻"(避免边沿抖动影响)采样电平,判断是 0 还是 1。

- 数据位传输完成后,发送方发送 1~2 个 "停止位"(高电平),表示一帧数据结束。接收方检测到停止位后,确认帧传输完成,可准备接收下一帧。

3. 优势

- 无需共享时钟:发送方和接收方时钟独立,降低硬件连接复杂度(如 UART 只需 TX/RX 两根线)。

- 抗干扰性强:长距离传输时,即使时钟有偏差,通过起始位和中间采样可修正误差(只要偏差在允许范围内)。

- 灵活性高:适用于不同设备间的通信(如电脑与传感器),无需严格同步时钟源。

4. 劣势

- 传输效率低:每帧数据包含起始位、停止位等额外开销(如 UART 每 8 位数据需 1 位起始位 + 1 位停止位,开销占 20%),不适合高速、大数据量传输。

- 对时钟精度有要求:接收方时钟频率需与数据率匹配(允许小偏差),否则采样时刻会偏移,导致数据错误(偏差过大会错过正确采样点)。

- 电路设计复杂:接收方需要边沿检测、位同步(找到每一位的中间时刻)等逻辑,尤其在高速场景下实现难度更高。

5. 典型应用

- 低速串行通信:如 UART(通用异步收发传输器)、RS-232/RS-485(工业控制中常用,抗干扰,适合长距离)。

- 简单设备交互:如单片机与传感器、蓝牙模块的通信(对速度要求不高,注重连接简便)。

三、关键区别对比

| 维度 | 同步时钟通信 | 异步时钟通信 |

|---|---|---|

| 时钟源 | 共享同一时钟(或严格同步) | 各自独立时钟(允许频率偏差) |

| 同步方式 | 依赖时钟信号边沿同步 | 依赖起始位 / 停止位等帧内信号同步 |

| 传输效率 | 高(无额外开销) | 低(含起始 / 停止位等开销) |

| 速度 | 适合高速(如 GHz 级) | 适合低速(如 kbps~Mbps 级) |

| 抗干扰与距离 | 短距离抗干扰好,长距离时钟易偏移 | 长距离抗干扰较好(依赖信号本身同步) |

| 硬件复杂度 | 时钟布线严格,接收逻辑简单 | 无需时钟线,接收逻辑复杂(需位同步) |

| 典型应用 | SPI、I²C、DDR 内存、片内互连 | UART、RS-232/RS-485、简单设备交互 |

四、混合场景:跨时钟域通信

在复杂系统中(如 SOC 芯片),常存在多个独立时钟域(如 CPU 核用 1GHz 时钟,外设用 100MHz 时钟),此时同步时钟和异步时钟可能需要交互,称为 "跨时钟域通信"。

- 核心问题:异步信号进入同步时钟域时,可能因 "亚稳态"(信号在时钟沿附近跳变,导致采样结果不确定)引发错误。

- 解决方法:通过 "同步器"(如两级触发器)、"握手协议"(如 req/ack 信号)或 "FIFO 缓冲" 等机制,确保数据在不同时钟域间可靠传输。

总结

- 同步时钟通信依赖共享时钟,效率高、速度快,适合短距离、高速、高带宽场景,但对时钟同步要求严格;

- 异步时钟通信无需共享时钟,灵活性高、适合长距离和低速场景,但效率低,依赖帧内同步信号;

- 实际系统中,二者常结合使用,跨时钟域通信需特殊设计以避免数据错误。

题目汇总--链接:

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-CSDN博客