一、原理

参考这个博主,讲的很仔细:基于脉冲功率的雷达脉冲参数检测原理详解

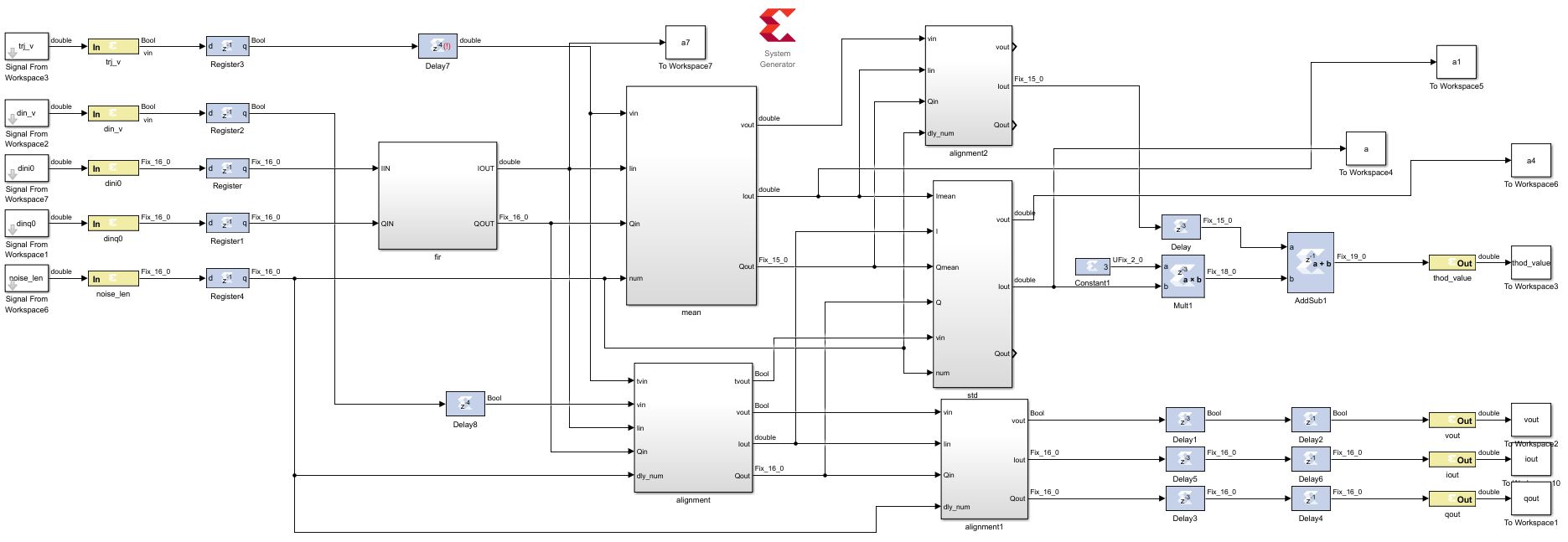

二、FPGA实现

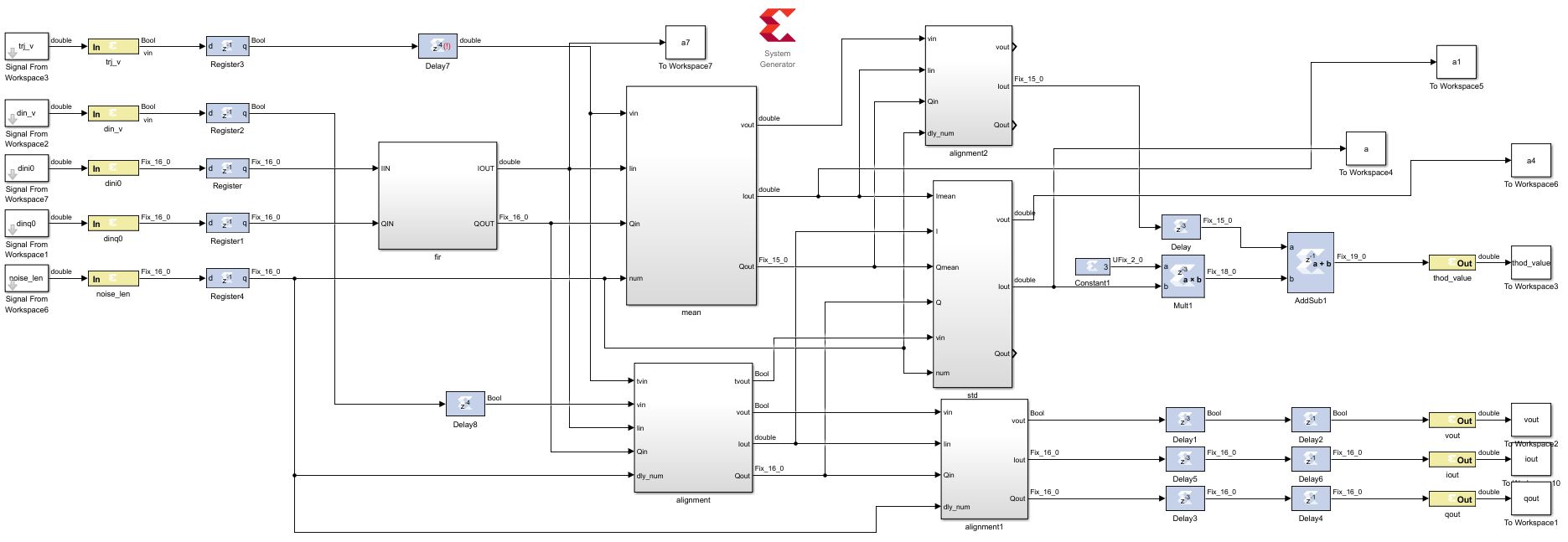

使用system generator搭建算法模型如下:

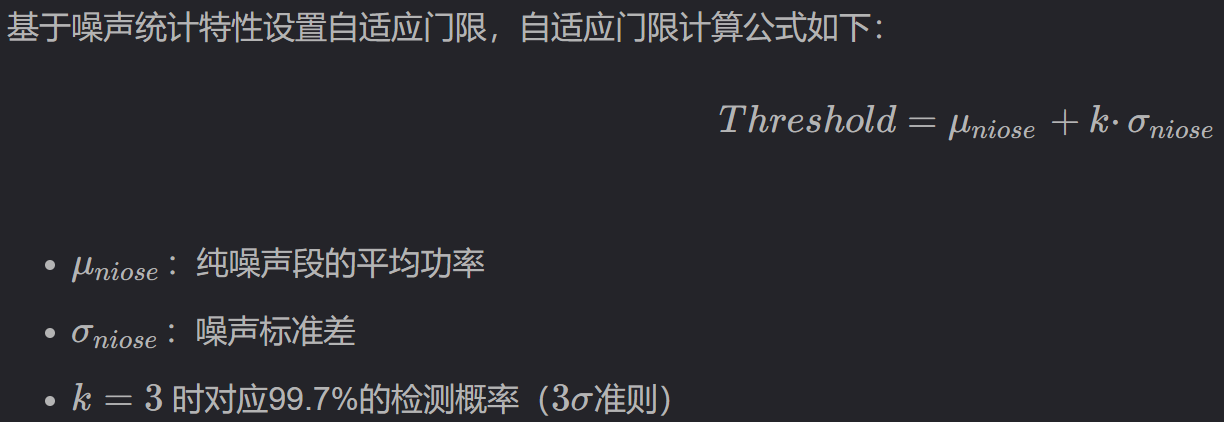

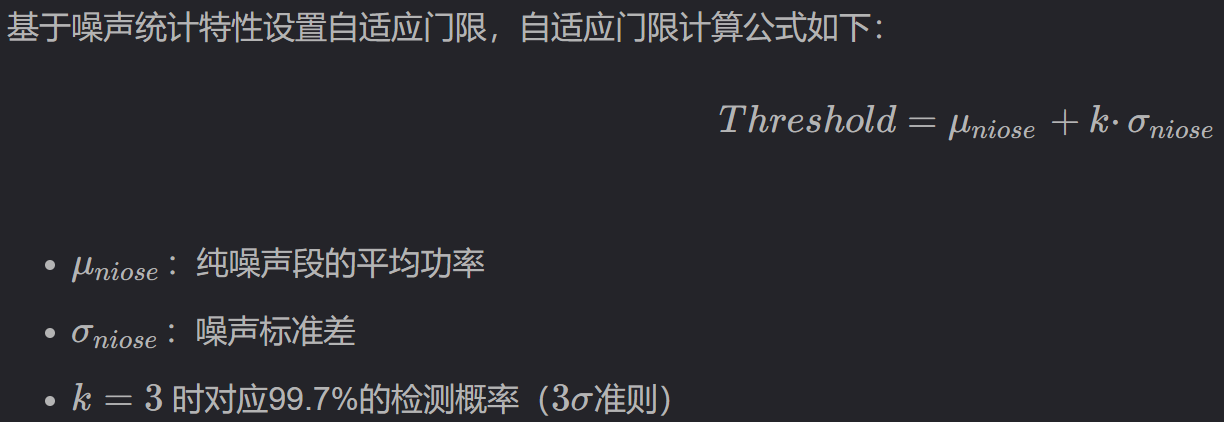

在这里,滤波器窗长度为8,原博主设置为50效果更好,门限公式如下:

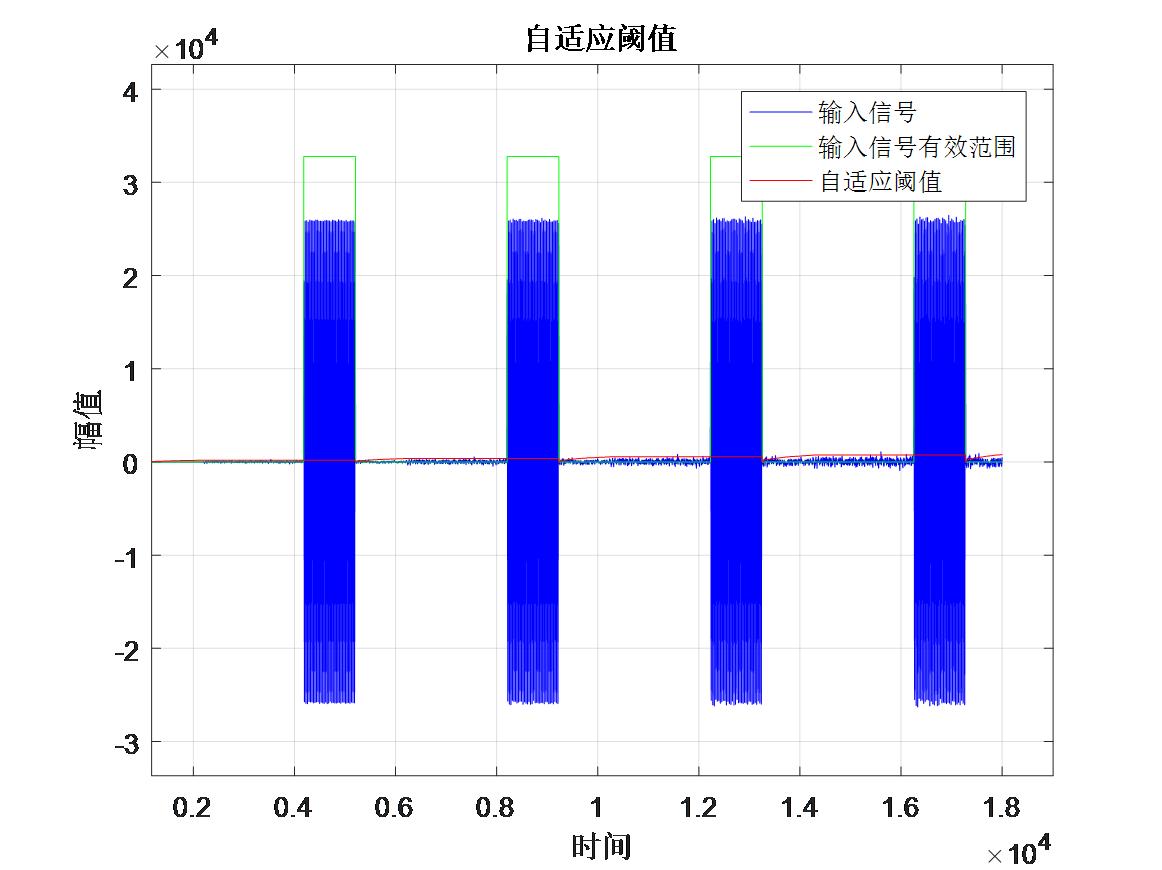

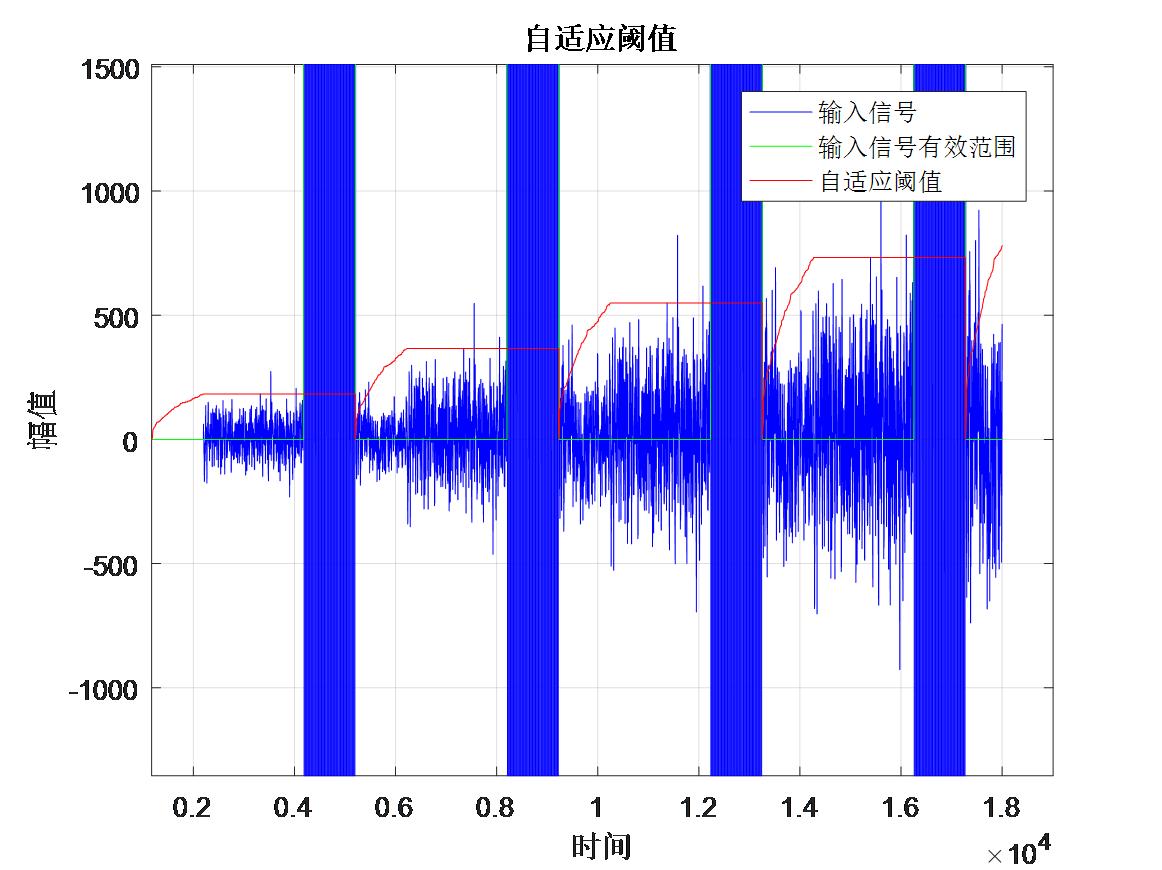

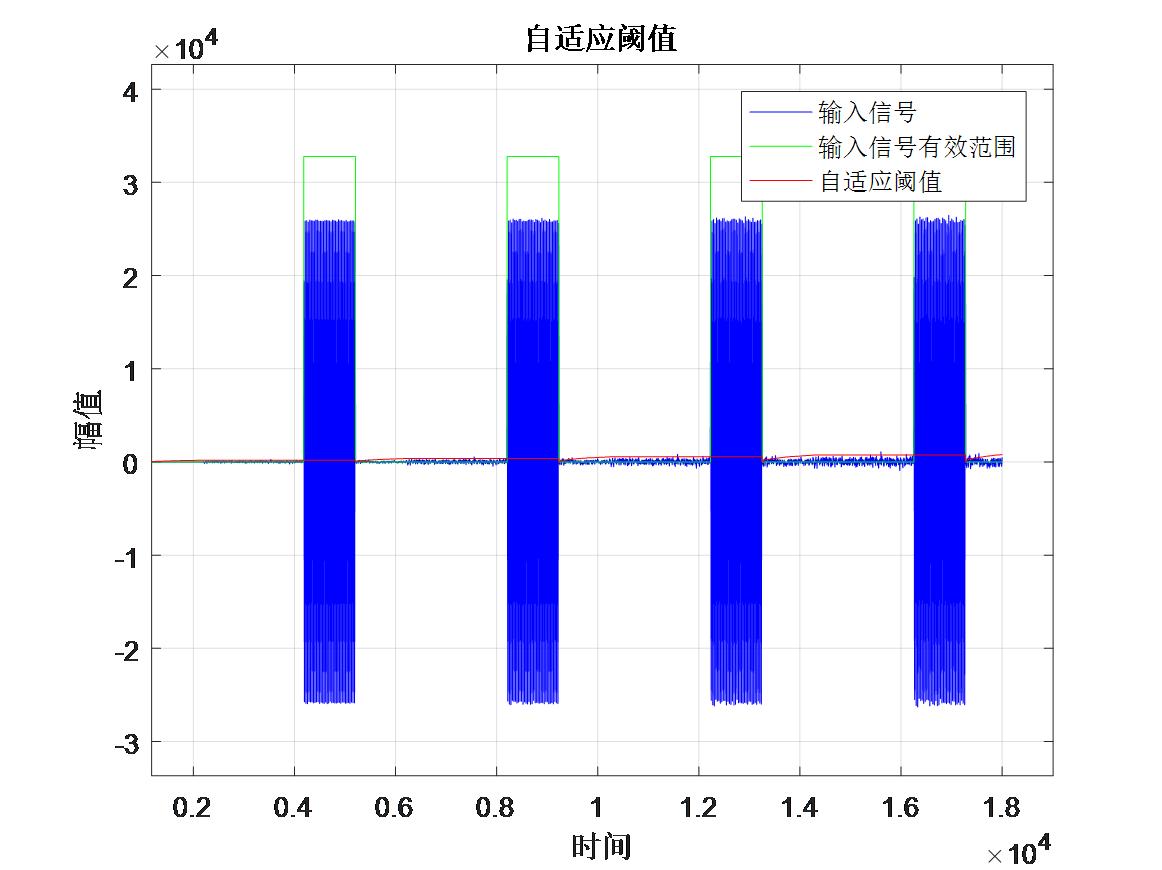

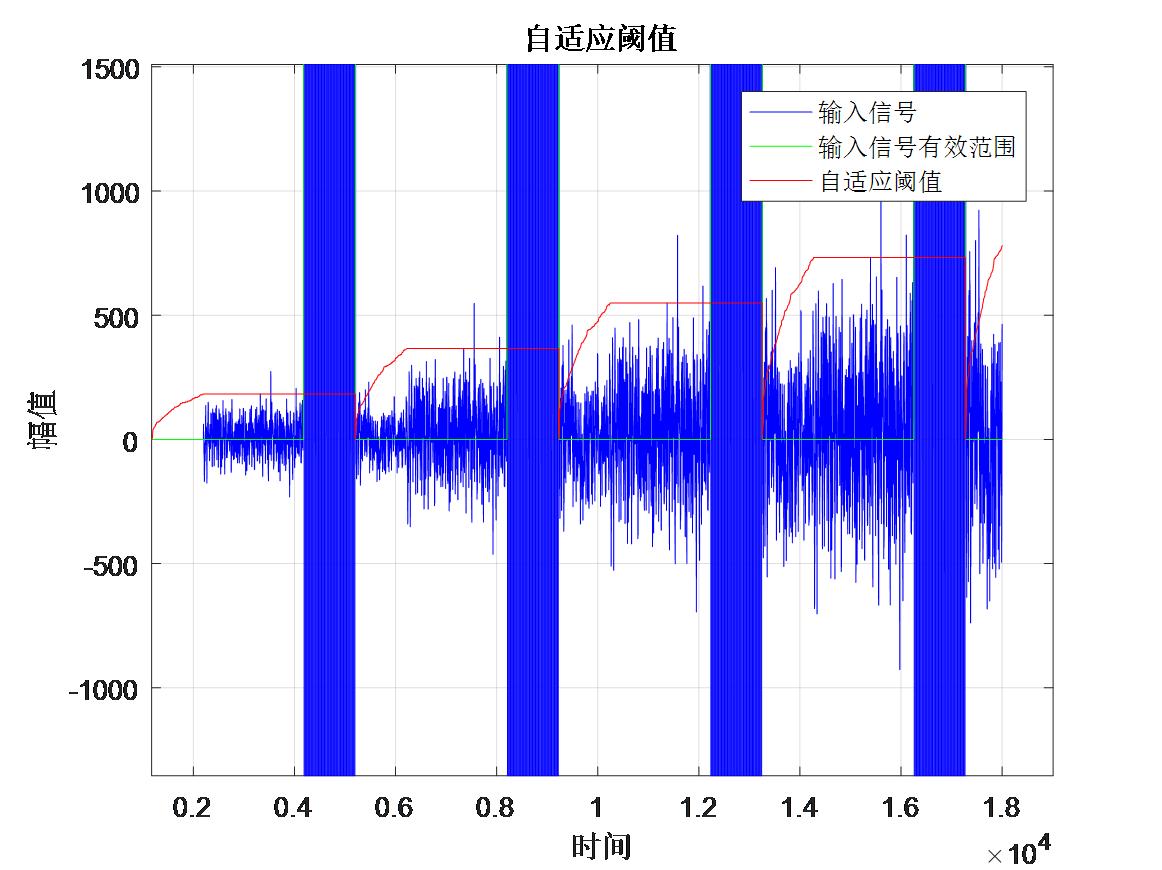

三、实现效果

基本满足设计要求,在实际使用时可以进行优化,可以增加滤波器窗长度,或者对求出的门限值进行等比例放大。此外,应该先求功率再滤波。

参考这个博主,讲的很仔细:基于脉冲功率的雷达脉冲参数检测原理详解

使用system generator搭建算法模型如下:

在这里,滤波器窗长度为8,原博主设置为50效果更好,门限公式如下:

基本满足设计要求,在实际使用时可以进行优化,可以增加滤波器窗长度,或者对求出的门限值进行等比例放大。此外,应该先求功率再滤波。